# Exam solutions (DAT091, DAT092, DAT093)

Lars Svensson

Jan 3, 2015

What follows are brief suggested answers/solutions. Other solutions than those listed here may be acceptable.

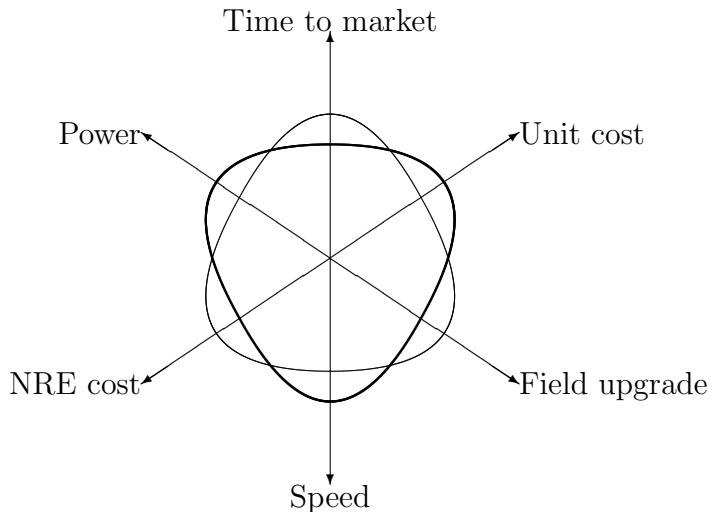

1. (a) *A diagram similar to the one below was shown in one of the lectures. Please copy the diagram below to a numbered solution sheet (you don't want your solution to be lost by mistake!) and mark approximate curves for an FPGA technology and an ASIC technology in the diagram. Use the "bigger is better" convention. (Note that the order of the axes has been changed with respect to the figure shown in the lecture.) The thicker line below is for ASICs, and the thinner one is for FPGAs.*

1. (b) *Under what circumstances might it be a good idea to implement a processor in an FPGA rather than just use a processor off the shelf? Please give a cost-driven example and a performance-driven example.*

Some non-trivial operations with relaxed performance requirements might be well served by a soft processor such as a PicoBlaze; if the FPGA is already in the system and has unallocated hardware, the processor is essentially free of cost.

Computations that fit a traditional processor badly could improve in performance with a tailor-made datapath. An example might be encryption algorithms which may operate on very long words.

2. *Pick any three of the following challenging trends for future electronic system design, and suggest possible approaches to managing or handling them.*

Here are some approaches mentioned during the course:

- *Growing complexity:* Larger development teams, CAD support at higher levels of abstraction

- *Increasing performance requirements:* Parallelism in microprocessors and other computing elements

- *Shrinking development time:* Platform design and other forms of design re-use

- *Stricter power requirements:* Specialized, highly efficient hardware blocks for different classes of computations

- *Reduced manufacturing cost:* Reconfigurability in order to meet several needs with one piece of hardware

3. (a) *Compare and contrast a hard deadline and a soft deadline in a real-time system.*

A missed hard deadline causes system failure; a missed soft deadline merely causes system performance degradation (graceful degradation, hopefully).

(b) *A multi-chip package, such as an MCM, may offer an alternative both to a single-chip solution and to a “traditional” multi-package assembly of the same chips. List some benefits and drawbacks of MCMs compared with each of the other alternatives. Two points per acceptable list item, up to a maximum of four items.*

Here are some:

- Higher packaging efficiency than the PCB version

- Better performance than a PCB version

- Better reliability than PCB version

- Need bare dies (chips w/o packages)

- Typically more expensive than PCB version

- Not as compact as a single-chip version

- Possible to use different technologies for the chips in the module (memory, processor, radio, etc)

4. (a) *In VHDL, what is the difference between signals and variables?*

Signals are used to describe data flow; signal assignment denote relations between variables which are in principle valid at all times.

Different assignments to a variable, on the other hand, take effect one by one in the order they occur. Variables are used to capture state in processes.

(b) *In VHDL, what is the difference between ports and generics?*

Ports provide connections between hardware blocks. Generics provide parameter values for parameterizable blocks.

(c) *In VHDL, what would you use constants for? Would you consider some other construct instead of a constant, and what might the benefits be?*

Constants are for immutable values, for example setting the size of some hardware structure; they help the designer avoid using literal values all over the code and thereby to avoid a common class of errors.

Replacing constants with generic parameters makes your VHDL description parameterized. You may now re-use the same core regardless of what the size of the hardware structure is.

5. (a) *PCBs are central components in most electronics systems, and system-level requirements often cause or motivate requirement for the PCB design. Briefly describe three PCB-level requirement types, together with corresponding system-level requirements. Two points per acceptable pair.*

Here are some:

| System requirement              | PCB requirement                                                                                                                     |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Processing speed                | Signal delay and bandwidth                                                                                                          |

| Power requirement and delivery  | Supply current capacity                                                                                                             |

| Structural strength of assembly | Stiffness of PCB                                                                                                                    |

| Ruggedness                      | Lack of brittleness of PCB and connectors etc                                                                                       |

| Thermal dissipation handling    | Evacuate heat from components<br>Survive thermal expansion and contraction<br>Avoid thermal degradation of solder joints            |

| Low cost                        | Few layers, standard materials (preferably FR4)<br>Cheap component assembly<br>Compatibility with cheap component packaging options |

(b) *The lecture on PCB design brought up time-of-flight ringing. Briefly describe the phenomenon and suggest how to handle it.*

Any characteristic-impedance discontinuity encountered by a signal transition travelling along a transmission line will cause a reflected transition which travels the other way. Thus, a transition will bounce back and forth between two such discontinuities, forming an oscillating signal with a decaying amplitude and with a period given by the round-trip time-of-flight between the two discontinuities.

Often the most significant impedance mismatches will occur at the source (transmitter) and sink (receiver) ends of the transmission line. Thus, to minimize these effects, designers strive to match transmitter and receiver impedances to the transmission-line impedance, and also to avoid other discontinuities along the line.

6. (a) *Please state the fundamental equation for dynamic power dissipation in digital CMOS circuits.*

$$P = f \cdot C \cdot V^2$$

(b) *The equation from task 6a suggests several ways to reduce the dynamic dissipation. List three concrete examples of design approaches that can be expected to reduce dynamic dissipation.*

As the power grows with  $f$  and  $C$  and grows with the square of  $V$ , reducing either of these entities should be good, as long as the other parameters are kept constant.

(c) *The approaches given in the previous task will not guarantee an overall low dissipation. Give at least two reasons why not.*

Reducing the frequency too far will reduce the throughput for the same hardware. The increased amount of hardware required to maintain throughput (for example, the number of additions per unit time) will eventually overwhelm the gains from the voltage reduction possible at the lower voltage levels. Likewise, reducing the voltage too far will bring the circuits into the subthreshold region, where performance falls much more rapidly than the voltage. Also, the equation only includes the dynamic power; the static power is not accounted for.