## Chapter 2

# DESIGN FOR MANUFACTURE

Barrie Gilbert

*Analog Devices Inc.*

### 2.1. Mass-Production of Microdevices

We generally think of mass production as a uniquely twentieth-century phenomenon. However, its evolution can be traced back much further. The explosion in printed books, following Johannes Gutenberg's fifteenth-century development of the Korean invention of movable type, had an impact on human society of heroic proportions. Precursors of modern mass-production, based on the *specialization of labour* and the *use of specialized machinery* to ensure a *high degree of uniformity*, can be traced to the eighteenth century. Writing in *The Wealth of Nations* in 1776, Adam Smith used the manufacture of pins to exemplify the improvement in productivity resulting from the utilization of uniform production techniques. Today, every conceivable sort of commodity is mass-produced. Pills, paints, pipes, plastics, packages, pamphlets and programs are mixed, extruded, poured, forged, rolled, stamped, molded, glued, printed, duplicated and dispatched worldwide on an immense daily scale. The most successful modern products are an amalgamation of many disciplines, years of experience, careful execution, rigorous production control and never-ending refinement.

In no other industry is the cross-disciplinary matrix so tightly woven, and the number of interacting elements so incredibly high, as in the semiconductor business. Reaching back to Gutenberg, and drawing on the principles of photography pioneered by Daguerre in the 1830s (embracing optics, lens-making, photosensitive films and chemistry), transistors are defined by a process of lithography, which is essentially *printing*. But what eloquent printing this is! A 200-mm silicon wafer has a useful area of about  $200\text{-cm}^2$ , a little less than a page of this book containing some 400 words of text, equivalent to perhaps 16,000 bits. However, when divided into  $1\text{-cm}^2$  chips - the size of a modest microprocessor, today containing about 50 million transistors, through perhaps 20 successive layers of printing and processing - each wafer generates some 10 billion devices in a single mass-produced entity. In a production lot containing 40 such wafers, some 400 billion tiny objects are manufactured in a single batch. Multiply this by the daily manufacture of integrated circuits worldwide, and it will be apparent that the number of transistors that have been produced

since the planar process was invented<sup>1</sup> runs to astronomical proportions far exceeding the expectations of its most optimistic and visionary progenitors.

Indeed, it is hard to identify any other mass-produced object that is fabricated in such prodigious quantities as the transistor. Even pills are not turned out in such numbers, and even when molecularly sophisticated, a pill remains a primitive amorphous lump of material. A transistor has a *complex fine-scale structure*, having a distinctive personality of its own (and a devious one: try modeling an MOS transistor!). Its near-perfect crystalline structure at the atomic level, and its precise dimensions and detailed organization at the sub-micron level, are fundamental to its basic function. No less important is the way these cantankerous virus-scale devices are tamed, teamed up and harnessed, in the *design of micro-electronic circuits*.

As their designers, we are faced with exciting opportunities and challenges. It is our privilege to turn essentially identical slabs of silvery-grey silicon – the stuff of mountains and the earth's most plentiful solid element – into clever, highly specialized components of crucial importance to modern life, handling everything from deceptively simple signals (voltages and currents, time intervals and frequencies) in analog ICs, all the way up to sophisticated packets of mega-information in computers and communication systems. Each of our creations will elicit uniquely different behaviour from the same starting material, and possess a distinctive personality of its own. How we shape this little piece of silicon, and the assurance with which it goes forth into the world and achieves its diverse functions, is entirely in our hands.

Integrated circuit designers who experience the rigour of dispatching their products to manufacturing, and watch them flourish in the marketplace and subsequently generate significant revenues for their company, soon discover that their craft entails a balanced blend of technique and judgment, science and economics. The path from concept to customer is strewn with numerous pitfalls, and it is all too easy to take a misstep. The practicing designer quickly becomes aware that silicon transistors, and other semiconductor devices, have a mind of their own, demanding full mastery of the medium if one is to avoid falling into these traps. One also learns that a circuit solution, no matter how original, elegant or intriguing, is of little value in abstraction. Cells, which will here be defined as small, essentially analog circuits of up to a dozen or so transistors, are merely *a resource* to be created (or discovered and understood), then tamed, refined and catalogued. Artful cell development is of fundamental importance to robustness in manufacture, but cells are certainly not the proper starting point for a *product* development, whose genesis arises within the context of broad commercial objectives, and which will exploit cell properties selectively

---

<sup>1</sup> By Jean Hoerni of Fairchild, U.S. Patent 3,025,589, filed May 1, 1959 and issued March 20, 1962.

and judiciously as the need arises. These basic fragments cannot be given any freedom to misbehave, if the products within which they are later utilized are to be manufacturable with high yields and at low cost.

This book is about how to design these basic cells so as to elicit some optimum level of performance, and particularly by considering the many trade-offs that invariably arise in adapting them to a specific use in a product. Such trade-offs are inevitable. Performance is always a compromise reached by giving up certain less desirable aspects of behavior in favor of those other objectives that are identified as essential. When such optimization is pursued with a set of public standards in mind (such as a cellular phone system like GSM), it is exceedingly important to find and utilize the “right” trade-offs, to provide an efficient and competitive design. Where the product is in the nature of a proprietary standard part, the choice of trade-offs may be harder, and involve more judgment and risk, since one often has considerable freedom to improve certain aspects of performance at the expense of others, in pursuing a particular competitive edge, which may be more sensed than certain.

For example, to halve the input-referred *voltage* noise spectral density in a bipolar junction transistor (BJT) low noise amplifier (LNA) one must at least quadruple the bias current.<sup>2</sup> However, this would be of little benefit in a cell phone, where battery power is severely limited, and provided that a certain acceptable noise figure is achieved, further reduction would be surplus to the system requirements. On the other hand, the same benefit would be very attractive in a state-of-the-art *standard product*: it could be the one thing that distinguishes it from all other competing parts. But then, with this increase of bias, the current-noise at the input port will double and that would no longer represent an optimal solution when the source impedance is high. While this is a rudimentary example of the pervasive “noise-versus-power” trade-off, decisions of this kind in the real world are invariably *multi-dimensional*: many different benefits and compromises must be balanced concurrently for the overall performance to be optimized for a certain purpose. It follows that trade-offs cannot be made in abstraction, in absolute terms; they only have relevance within the scope of a specific application.

### 2.1.1. Present Objectives

This chapter strives to illuminate the path to production a little more clearly, by providing a framework for successful commercial design. While it includes

---

<sup>2</sup> Specifically, the base-emitter voltage noise spectral density for a BJT due to shot noise mechanisms evaluates to  $0.46 \text{ nV}/\sqrt{\text{Hz}}$  at a collector current  $I_C$  of 1 mA, and varies as  $1/\sqrt{I_C}$ . The current noise at this port, on the other hand, varies as  $\sqrt{I_C}$ . To these noise components must be added the Johnson noise due to the junction resistances, which does not depend to any appreciable extent on the bias current.

a few illustrative trade-offs, its emphasis on sounding down some more general tenets of robustness in cell design, with high-volume production in mind. The examples are drawn mostly from BJT practice. It outlines some basic cautions we need to observe in our design discipline, including our awareness of the limitations of device models and simulation, and examines the notion of worst-case design. Later, it delineates a dozen work habits of the manufacturing-oriented designer. A brief discussion of some of the ways we can minimize risk and optimize performance through the use of careful layout practices can be found in Chapter 33.

To reach the point of being ready to mass-produce a robust, cost-effective, highly competitive product, we will use many tools along the way. The best tool we will ever have, of course, is the magnificent three-pound parallel processor we carry on our shoulders. Nevertheless, for the modern designer, a circuit simulator, such as SPICE, when used creatively and with due care, can provide deep insights. Many brave attempts, including those of the author in his younger years, have been made to capture design expertise, in the form of programs that automate the design process. These range from such simple matters as calculating component values for a fixed circuit structure, to choosing or growing topologies and providing various kinds of optimization capabilities. Advanced design automation works well in coping with procedures based on clearly-defined algorithms, of the sort that are routine in digital design. However, they have been less successful in aiding analog design, and are of little help in making trade-offs. This is largely because each new analog IC development poses distinctly different design challenges, often calling for on-the-spot invention, since cell reutilization is fraught with problems and of limited value. In this field, as elsewhere, there are no algorithms for success: we must continue to rely on our creativity, our experience, our ability to draw on resources, and our judgment in facing the matter of design trade-offs.

Numerous pitfalls and obstacles will be encountered on the path between the bright promise of the product concept and that moment the IC designer most looks forward to: the arrival of first silicon. But the seasoned engineer knows that these first samples are just the tokens we handle at the beginning of a longer and more arduous journey. Still ahead lie many months of further documentation and extensive testing, during which the glow of early success may fade, as one after another of the specifications is found to be only partially met, as ESD ratings are discovered to be lower than needed on some of the pins, or as shadowy, anomalous modes of operation make unwelcome cameo appearances. There follows the challenge of finding ways to make only minor mask changes to overcome major performance shortfalls; the interminable delays in life test; and the placating of impatient customers, not to mention the marketing folks, who see the window of opportunity at risk of closing.

## 2.2. Unique Challenges of Analog Design

Such obstacles stand in the way of all professional IC designers, but there are radical differences in individual design style, and between one sub-discipline and another. In the digital domain, the design focuses on assembling many large, pre-characterized blocks, comprising thousands of gates, amounting in all to a huge number of transistors (often known only approximately<sup>3</sup>) each one of which must reliably change state when a certain threshold is reached. Advances in this domain stem largely from improvements in micro-architecture, a relentless reduction in feature size and delay times, and advances in multi-layer metalization techniques, which are also necessary to pack more and more functional blocks into the overall structure, while keeping the chip size and power to manageable levels.

As clock rates climb inexorably into the gigahertz range, the dynamics of these gates at the local level, and the communication of information across the chip, are generating problems that, not surprisingly, are reminiscent of those encountered in classical RF and microwave design. Further, the very high packing densities that are enabled by scaling give rise to new problems in removing the heat load, which, milliwatt by milliwatt, adds up to levels that demand special packaging and sophisticated cooling techniques. Such issues, and the sheer complexity of modern microprocessors and DSP elements, will continue to challenge digital designers well into the century. Their trade-offs will not be addressed here.

The challenges that arise in the domain of analog functions are of a distinctly different kind, and stem principally from two unique aspects of analog circuits. First, there is *much greater variety*, both in chip function, which can take on hundreds of forms, and in the particular set of performance objectives, and even the specification methodology (such as “op-amp” versus “RF” terminology), from one product to another. Second, the actual performance, in all its many overlapping and conflicting facets, *depends on the detailed electrical parameters of every one of the many devices* comprising the complete product, and in a crucial way for a significant fraction of this total. Obviously, it is quite insufficient to simply ensure that a transistor is switched on or off, or even that this transition occurs very quickly and at just the right time; such are only the bare bones requirement of the analog transistor. So much more is now involved in “meeting the specs”, and *this parametric sensitivity* touches at the very heart of what makes analog circuits so different from their distant digital cousins.

---

<sup>3</sup> Patrick Gelsinger of Intel told me the exact number of transistors in the 486 microprocessor is 1,182,486 (the last three digits were “a coincidence”) noting that how one counts devices is somewhat imprecise in the first place.

Much of what we do as designers will require constant vigilance in minimizing these fundamental sensitivities.

Many detailed challenges in signal management face the analog designer. In even a simple cell such as an amplifier, one is confronted with first, the choice of a topology that is both appropriate and robust; then the minimization of noise, distortion, and power consumption; maintenance of accurate gain; elimination of offsets; suppression of spurious responses; decoupling from signals in other sections performing quite different functions; coping with substrate effects; unrelenting attention to production spreads, temperature stability; the minimization of supply sensitivity, and much more.

In the domain of nonlinear analog circuits, special effort is needed to achieve accurate conformance to one or more algebraic functions, such as square-law, product and quotient, logarithmic and exponential responses, and the like. With all nonlinear functions there is also a special need for vigilance in the matter of scaling, that is, control of the coefficients of the contributing terms. Voltage references are often needed, which may need to be exact without recourse to trimming. In filter design, another set of imperatives arises, having to do with ensuring accurate placement of the poles and zeroes of the transfer function even in the presence of large production tolerances. Many modern products combine several of these various functions, and others, in a single chip.

Hard-won analog design victories are known only to a small group of insiders, who are proudly aware of the continual, quiet improvements that so often are behind many of the more visible successes that shape modern communications devices, and which are likely to be bundled with the DSP and microprocessor parts of the system and presented to the public in the guise of yet another advance arising solely from the wondrous properties of digital technologies. One can understand the indifference to analog techniques invariably displayed by the public, but it is worrisome to see this now appearing in the attitudes and skill-sets of new graduates in electronics. Behind all of the glamor that digital systems generate in the popular eye, there is a massive infrastructure of essential analog electronics, and a growing need for skilled analog designers. In the twenty-first century, design challenges with a pure-analog emphasis will not diminish; rather, they will be plentiful. Unfortunately, the number of new engineers available to address these challenges may not keep up with the demand. University students are often led to believe – incorrectly, just like the public at large – the now familiar mantra that “analog is obsolete.” This is manifestly false.

These challenges will continue to be related to achieving *small but exceedingly difficult improvements* in certain key parameters, rather than increasing the raw number of transistors that can be crammed into the latest CPU. For example, while a 1-dB improvement in the signal-to-noise ratio of a receiver does not seem very impressive, it typically results in a ten-fold improvement in

the bit-error-rate of a digital channel. It requires considerable inside knowledge to separate the confusing claims made for the latest digital gadget, so persistently and persuasively made by their promoters, from the fact that analog techniques remain important even in the most sophisticated of these products.

The common view is that, by virtue of the certainty of binary data, digital systems avoid the many ambiguities of analog circuits, which have a reputation for being unrepeatable, temperamental, unstable, prone to drift and loss of calibration, or bursting into oscillation without warning. Many of these weaknesses are real, and can be traced to poor design, particularly through inattention to the all-important matter of *robustness* and the *minimization of parametric sensitivities*, which is why there is a need for a book of this sort. Nevertheless, a crucial dependence on the precise values of certain dimensional parameters – for example, those determining the bandwidth of an amplifier – is frequently unavoidable, and unrelenting vigilance is needed during design to ensure robustness in production. Close attention to component tolerances and design margins is essential, and trade-offs must be made carefully.

For example, it is soon discovered that there are inherent trade-offs to be made between achieving uncompromising state-of-art performance on the one hand, while minimizing cost and ensuring a high degree of robustness and chip yield on the other. Since this is true, modern system designers are only being prudent in seeking ways to reduce the “analog front end” to the barest minimum, or even eliminate it; invariably, they are not being unfair in asserting that “This is where our worst problems are to be found.” Analog circuits will always be prone to these criticisms, because they are fundamentally closer to the physical reality than are digital circuits. And this is where another key difference is to be found.

### 2.2.1. Analog is Newtonian

In an important sense, *analog circuits are closer to nature than are digital circuits*. This viewpoint can help us to understand why these two domains of endeavor are fundamentally so different.<sup>4</sup> Certainly, many of the challenges in digital electronics today also have a strongly physical aspect, mostly, although not entirely, at the cell level. But these stand apart from the more important development thrusts relating to the transformation of logical data, rippling through gates which reshape and retime this data, within which the strictures of sequential discrete algorithms replace the unfettered autonomy of the analog

---

<sup>4</sup> There are actually *three* fields of electronics today: the two major groupings, analog and digital, and a third, smaller but well-defined and rapidly-growing group of techniques which we can call *quasi-analog* or *binary-analog*, exemplified by “sigma-delta” techniques. The three basic disciplines overlap strongly and are co-dependent: they are at once symbiotic and synergistic.

circuit. Once a library of digital cells has been generated, with careful attention to time delays and threshold margins, their inherently analog nature is no longer of interest in digital design.

Analog circuits are more deeply allied to the physical world because they are concerned with the manipulation of *continuous-time*, *continuous-amplitude* signals, often of *high accuracy*, having *dimensional* attributes, traceable to *fundamental physical constants*. (Logic signals are, of course, dimensionless.) The primary physical units are length [L] in meters, mass [M] in kilograms, and time [T] in seconds, and we here use charge [Q] in coulombs as the fourth basic unit.<sup>5</sup> The *physical algebra* of analog-circuit analysis differs from ordinary algebra in requiring attention to *dimensional homogeneity*. Thus, *voltage* signals embed the dimensions of  $[ML^2T^{-2}Q^{-1}]$ . Sometimes, greater importance is attached to the signal *currents*, which are of dimension  $[QT^{-1}]$ . Voltages are just another way of representing *energy*  $[ML^2T^{-2}]$  normalized through division by the electron *charge* while current may be envisaged as counting multiples of charge quanta over a specified *time* interval. It follows that *current-mode* signal representation is more prone to absolute-magnitude errors than voltage-mode representation, since in the latter case, scaling can be quite directly traced to such things as the bandgap energy of silicon, the Boltzmann constant  $k$ , temperature and electronic charge,  $q$ . Nevertheless, current signals can maintain high *ratio accuracy* and have certain benefits.

Dimensional quantities are inextricably woven into the fabric of the universe, from sub-atomic forces up to the largest cosmic objects. They are also embedded in energy fields. RF signal levels in a transceiver can be equated to an electromagnetic *field strength* at the antenna, and expressed as a *power*,  $[ML^2T^{-3}]$ , at *some frequency*  $[T^{-1}]$ . Similarly, the electrical circuit elements within which these signals flourish and propagate have their own set of physical dimensions: *resistance*  $[ML^2T^{-1}Q^{-2}]$ ; *capacitance*  $[M^{-1}L^{-2}T^2Q^2]$ ; and *inductance*  $[ML^2Q^{-2}]$ . The attribute of *spin*,  $[MLT^{-1}]$ , is an essential aspect of semiconductor device behavior, as are the *mass* [M] and *velocity*  $[LT^{-1}]$  of holes and electrons, and the pure *length, width and thickness* [L] of device structures. In view of this strongly-physical nature of analog circuits, it is not inappropriate to use the term *Newtonian* to describe them.

### 2.3. Designing with Manufacture in Mind

Designing integrated circuits in a commercial context, one is daily confronted with the need for compromise, expediency and pragmatism – which

---

<sup>5</sup> The International System of Units (SI) uses the Ampère, rather than charge. Charge is used in the present context because it is an intimate aspect of semiconductor physics.

continually orbit our concerns about development time and product cost – while preserving performance and robustness. These imperatives are rarely addressed in technical university courses. It is common to pursue only those aspects of design which one most enjoys, such as exploiting an exotic new technology, conceptualizing intriguing and bold new approaches, constructing grand system architectures, devising new circuit functions, discovering novel topologies, laying down a fine theory, acquiring a patent or two, or writing a paper for a major conference or professional journal. At times one may lean toward a highly favorable, idealized viewpoint of the task, deferring criticism and “second order effects” for another time. If not careful, one may completely lose sight of the fact that the variables which are so confidently manipulated in spread-sheets and simulations (gain, noise, intermodulation, power, matching and stability criteria, bandwidth, phase margin, frequency, and the like) are but a simplification of harsher realities.

Assailed by all the slings and arrows of outrageous wafer processing, products conceived in the refined conceptual world face a traumatic trial, which only the fittest survive. While intellectually aware that this is so, we may pursue our design work with optimism, in the tacit belief that our devices are basically uniform and predictable, and element variability is only a secondary consideration. Because of the tight controls on the many steps used in a modern IC process, this is not an entirely vain hope. We have come to expect extraordinarily high manufacturing standards and prodigious production yields, often to exacting specifications. Nevertheless, many disappointments can creep into the performance of production components. Some of these are certain but unavoidable; others, while equally predictable, can be averted by the use of thoughtful design practices. Often, we have to sacrifice certain desirable aspects of performance to ensure some others will be met, the essence of a trade-off, which is the central theme of this book.

### 2.3.1. Conflicts and Compromises

In the world of commercial product design, *performance trade-offs are rarely two-fold in nature*. Certain design conflicts arise in pairs when utilizing a given technology, such as between bandwidth and power consumption, between intermodulation and noise, in balancing the contributions of voltage and current noise, and so on. But these can just as easily be coupled in other ways: noise is in a constant contest with bandwidth; intermodulation distortion can often be lowered only by using higher power consumption; and many aspects of static accuracy are in conflict with achieving high bandwidths. Each design involves complex, multi-variable interactions, and compromises are inevitable.

Good practice demands that adequate consideration is given to every one, perhaps hundreds of such conflicts that can arise during several weeks of design

time, sometimes within the compass of a dozen transistors. Indeed, as we shall see later in this chapter, even a one-transistor LNA can consume a great deal of effort in order to optimize its performance and to be able to guarantee that it will fully meet all of its specifications in every one of millions of future instantiations of the product in which it is embedded.

A thorough understanding of these interactions is the essential starting point in the long road to design mastery in the analog domain. A very basic consideration is that of suppressing, as far as possible, the effects of temperature on circuit behavior. The second most obvious objective is to minimize the impact of changes in supply voltage. And even when suitable countermeasures have been found, and all the fundamental circuit relationships have been aligned in the most optimal manner for a particular set of objectives, there remains the significant hurdle of desensitizing performance to *production variances*.

These three top-level obstacles to achieving robust and reliable performance are sometimes referred to as the PTV (Process, Temperature, Voltage) aspect of the design challenge. Beyond these barest of necessities lie the broad plains of optimization, the central design phase in which performance conflicts will be met by making trade-offs. However, before we can proceed with a detailed discussion of some examples, and start to think seriously about optimization, we must give further consideration to the various types of process sensitivities that can arise in analog design. Further, it must be understood that these are in no sense sequential parts of a design flow, during which each potential sensitivity, or an aspect of optimization, is addressed and then set aside. Undesirable circuit interactions can appear at any time. The most dangerous are those which arise due to “trivial” changes made late in the design process, changes that are in the nature of an afterthought, and which thus do not receive the benefit of the thousands of hours of simulation studies that probably went into shaping the rest of the product, and rigorously verifying its behavior.

### 2.3.2. Coping with Sensitivities: DAPs, TAPs and STMs

In a typical IC manufacturing process, there are numerous production parameters that vary, including: implant dose rate and time, and other factors affecting total doping concentrations; furnace temperature and time; gas flow rates; etch and deposition times; resist composition, and other factors related to chemical quality; oxide growth rates, fine structure and uniformity; resist thickness and uniformity; micro-assay composition of sputtering targets; and so on. These “low-level” physical variations will manifest themselves through an even wider variety of effects in the “high-level” electronic parameters at the device level.

Beyond this, the use of numerous different circuit topologies in the design phase, and the broad and essentially unconstrained choice of operating

conditions for each device, create even greater *parametric complexity*. It is inevitable that these variances will influence the “top-level” performance of our circuit, to a greater or lesser degree. We have to allow these variances full reign, while ensuring that nearly every instantiation of the product across the wafer meets its operational specifications (which is the first aspect of the *robustness challenge*) and that every sample passing muster during production testing will remain within its performance limits over its lifetime, when large temperature and supply voltage variations can occur (the second aspect of the *robustness challenge*).

Success in this context requires attention to the most minute detail, and may easily fall out of our grasp, if even a seemingly minor detail is neglected. The simplest of components, such as monolithic resistors and capacitors, embody numerous low-level process parameters which influence their absolute value. Suppose that we are relying on a resistor–capacitor product to determine a time-constant, and thus set the frequency of an oscillation. We must design our product so that the error in the unadjusted frequency can be accommodated; that is, either we can formulate a method for manually trimming to the needed accuracy, or the worst-case<sup>6</sup> uncertainty is within the capture range of some automatic tuning means. Errors in the resistor and capacitor contribute equally to the error in frequency, which is of the form  $k/CR$ .

Most basically, the sheet resistance of the layer used for fabricating the resistor is subject to considerable variation. In a diffused or polysilicon resistor this will arise from variations in doping concentration and the depth of the diffusion or film, and can easily be as high as  $\pm 15\%$ , a 30% spread. Conductance in any resistive layer is also a function of temperature, sometimes a strong function. For example, the sheet resistance of a diffused resistor may typically vary by 1,500 ppm/K at  $T = 300$  K, which extrapolates to variation of about 20% over the 130 K range from 230 to 360 K ( $-43^\circ\text{C}$  to  $87^\circ\text{C}$ ). This raises the tolerance band to about 50%. Hopes of containing the frequency within a narrow range are already fading.

Variations in the width and length of the resistor must also be accommodated. When the absolute value needs to be well controlled, one would normally choose to use a physically large resistor, but this may be contraindicated when operation at high frequencies is also required, and the parasitic capacitances of the resistive layer become prohibitive. Assuming a moderate width of about  $10\ \mu\text{m}$  for such a situation, and allowing for a maximum variation of  $0.25\ \mu\text{m}$  at each edge, we are faced with a further 5% uncertainty. There may also be some voltage modulation of resistance. Thus, the resistance alone may vary over a

---

<sup>6</sup> The question of whether the term *worst-case* always has a definite meaning is discussed later in the chapter.

60% range, in a high-volume, robust design context. Adding to this estimate all the similar variations in the capacitor value, particularly those due to variations in the dielectric layer, and for junction and MOS capacitors their varactor behavior, it is easy to understand why the frequency of our basic oscillator can be predicted in only approximate terms: it already has process, temperature and possibly supply sensitivities even before considering the effect of the active elements. Specifications based on the assumption of tighter controls are worthless.

This is a very common situation in analog design, and stems directly from the physical nature of analog signals and components. Aspects of performance that exhibit this particular kind of sensitivity can be classified as *Dependent on Absolute Parameters*; we will refer to such aspects of performance as “DAPs”. It is impossible to eliminate sensitivity to this class of parameters by design tricks, though we may in special cases be able to reduce the sensitivity.

For example, the gain-bandwidth of an IC operational amplifier invariably can be traced to the product of a resistance (ultimately setting the value of a  $g_m$ ) and a capacitance (which may be defined by an oxide layer, as would usually be true for a low-frequency op-amp, or an incidental junction capacitance, as might be the case for a wideband amplifier). Since even carefully designed resistors may have a tolerance of up to  $\pm 25\%$ , and capacitors can vary by  $\pm 15\%$ , the control of gain-bandwidth in an op-amp<sup>7</sup> may be no better than  $\pm 40\%$ . However, it is later shown that when using this amplifier cell in a closed-loop mode, one can introduce a lag network into the feedback path such as to implement an overall two-pole response just above the high-frequency roll-off in which the gain at some (known) signal frequency can be made much less dependent on the position of the dominant pole. The method invokes the reliable *matching* of similarly-formed components, the cornerstone of all monolithic design, to lower the sensitivity to their actual values, in a rather non-obvious way.

In the fastest amplifiers we can make, using BJT processes, and in which the transistors are operating near their peak  $f_T$ , it is more likely that the variations in effective base-width and current density cause the production spreads in bandwidth. In turn, the current density depends on the actual emitter area (thus, on lithography) and is invariably dependent on some on-chip voltage source and at least one resistor. Since the  $f_T$  is a diminishing function of temperature,

---

<sup>7</sup> Few op-amp data sheets are forthcoming about this spread, often stating only a typical value. Similar vagueness is often found in the specifications for RF products. Some of this imprecision can be traced to the cost of testing ICs to allow these aspects of performance to be fully guaranteed; some of it has arisen as a kind of tradition, with concerns that the explicit revelation of the magnitude of such spreads would put a more completely-specified part in a “bad light”.

spreads from this source must also be addressed. In those cases where devices are operated at very low currents, however, the device's  $g_m$ , its (uncertain and voltage-dependent) junction capacitances, and interconnect capacitances set a limit to attainable bandwidth. Whatever the precise mechanisms, the bandwidth of virtually all monolithic amplifiers is strongly “DAP”, and in system design we must find ways to accurately define the channel bandwidth (which is only a fraction of the amplifier bandwidth) by the use of off-chip components, such as LC resonators, SAW or ceramic filters, or high-precision CR networks. Certainly, it would be very unwise to depend to any critical extent on the unity-gain frequency of common feedback amplifiers.<sup>8</sup>

As a rule, most (though not all) specifications which have a dimension<sup>9</sup> other than zero will be DAPs. These include time  $[T]^1$  and frequency  $[T]^{-1}$ ; current  $[A]^1$  in a cell (setting  $g_m$  and total consumption); all internally-generated voltages  $[V]^1$ , (such as noise,  $V_{BE}$ , bandgap references, etc.); inductance  $[L]^1$ ; capacitance  $[C]^1$ ; resistance and impedance  $[\Omega]^1$  or  $[L]^{0.5}[C]^{-0.5}$ ; conductance and admittance  $[\Omega]^{-1}$  or  $[L]^{-0.5}[C]^{0.5}$ ; etc. These sensitivities are addressed in various ways, some well known. Where absolute accuracy is essential, we can bring the dimension of “time” to an IC by utilizing a reference frequency defined by a crystal; or we can introduce the International Volt by laser-trimming against a primary standard during manufacture; we can use external resistors to establish accurate currents; and so on.

Next we turn to the second of these sensitivities. Absolute errors in the element values of *all components made of the same materials* (of all resistors, all capacitors, all current-gains, all  $V_{BES}$ , etc.) need not affect certain crucial aspects of performance. By relying on the use of *pure ratios*, we can assure the accuracy of any specification having dimension zero. Examples are gain at relatively low frequencies (and gain matching); attenuation (even up to high frequencies); relative phase between two signals (and precision in quadrature); filter Qs and overall filter shapes; conformance to functional laws (such as logarithmic, hyperbolic tangent, square-law); waveform, duty-cycle, weighting coefficients; DAC/ADC linearity, and the like.<sup>10</sup>

---

<sup>8</sup> In the 1970s a great deal of nonsense was being published about using “the operational amplifier pole” as a basis for the frequency calibration of what were misleadingly called “Active-R Filters”.

<sup>9</sup> Again, the dimensions used here are those familiar to electrical engineers. In a formal treatment, they would of course be expressed in fundamental MKS or CGS units. Logical signals have dimension zero.

<sup>10</sup> Of course, the use of digital ratios brings an even higher level of accuracy, for example, in frequency division. But not all logical circuits are above reproach. Phase jitter and non-quadrature are just two examples of error in supposedly pure-binary circuits where analog effects lead to degraded performance.

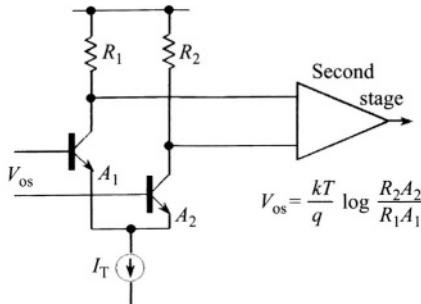

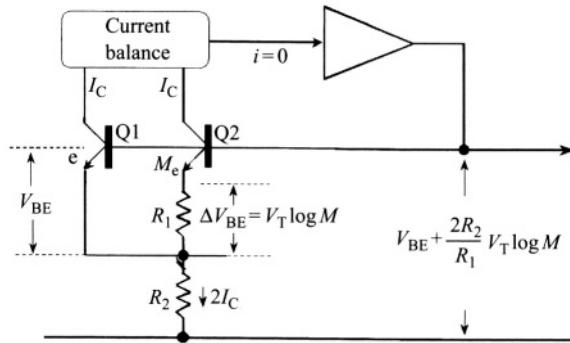

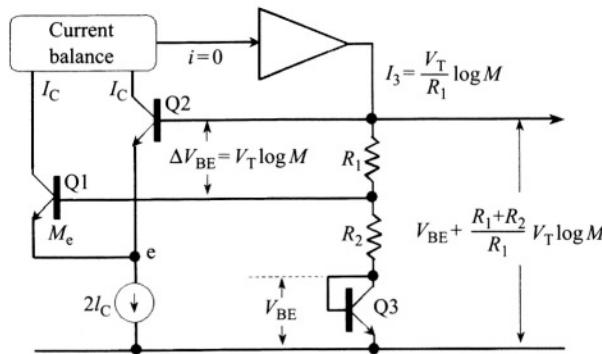

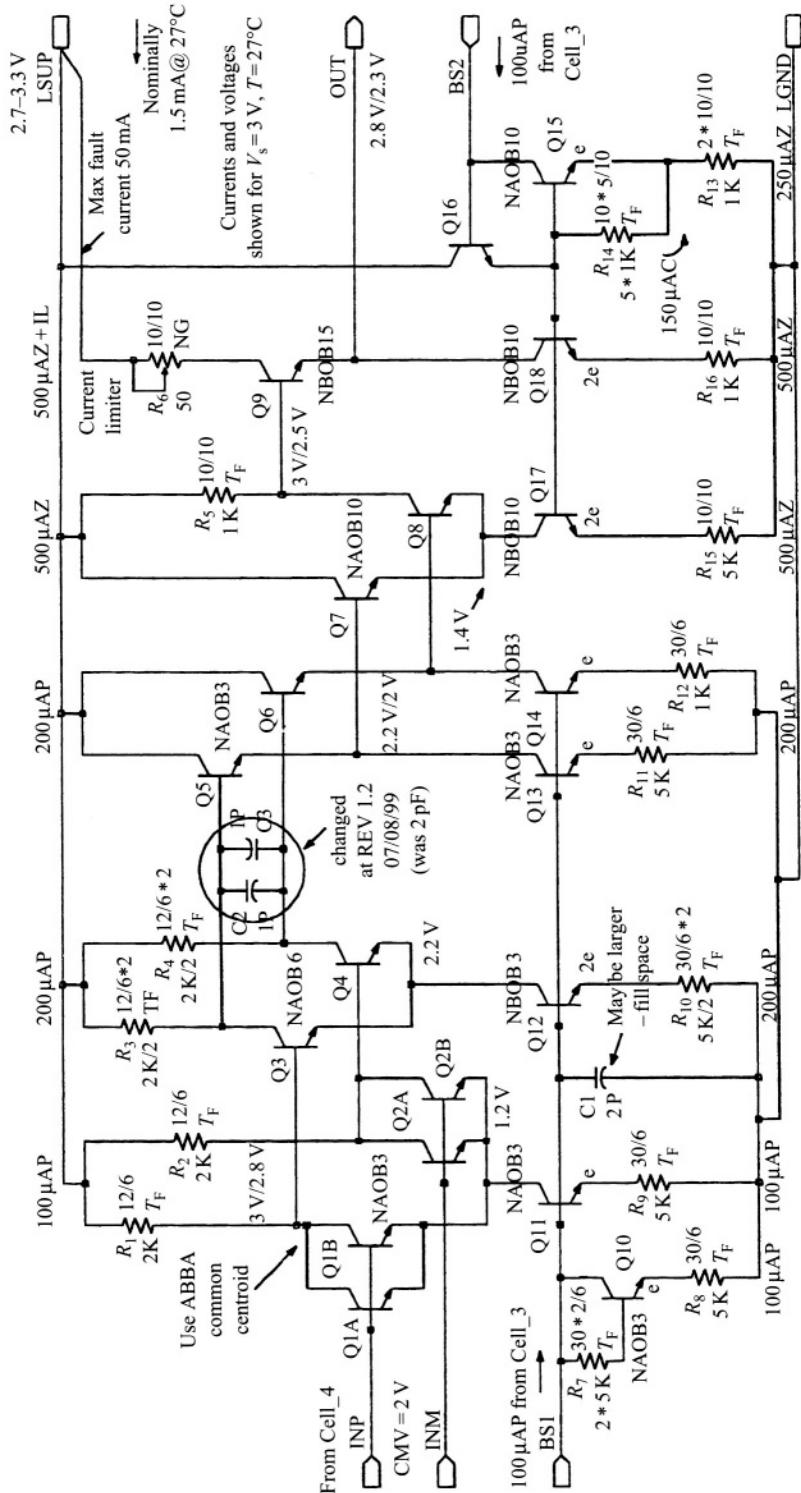

Figure 2.1. Some ratiometric circuits produce dimensional quantities.

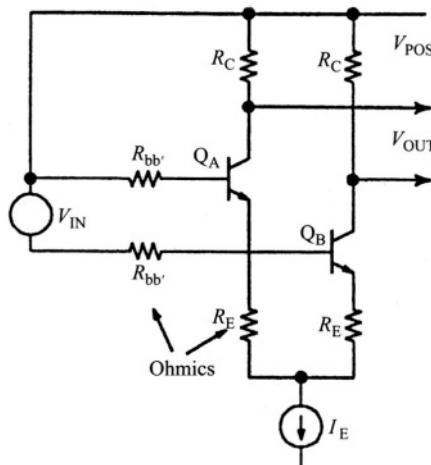

We may call such specifications *Tolerant to Absolute Parameters*, and will refer to them as “TAPs”. Because of this tolerance, or low sensitivity to tracking element values, we can in principle achieve highly accurate low-frequency gain, even in the presence of large absolute variations. In special cases, even some dimensional variables are in this class of TAPs. For example, the input-offset voltage of an op-amp using a BJT differential-pair as its  $g_m$  stage (Figure 2.1) is a precise function of the circuit parameters:

$$V_{os} = \frac{kT}{q} \log \frac{I_1 A_2}{I_2 A_1} = \frac{kT}{q} \log \frac{R_2 A_2}{R_1 A_1} \quad (2.1)$$

Provided that the emitter areas and the load resistors can each be made closely equal,<sup>11</sup> the offset voltage will be small, typically sub-millivolt. Its actual magnitude will be dependent on neither the absolute size of the emitters nor the absolute value of the resistors, and it is scaled only by the fundamental dimensional quantity  $kT/q$  (25.85mV at  $T = 300$  K). In monolithic analog design, we are constantly on the lookout for phenomena of this sort. The TAP perspective relies on a strong reliance on *ratios* to eliminate the effect of large absolute variations in parameters, and on an appeal to fundamental scaling phenomena rather than a reliance on external stimuli.

A related use of the above equation is the generation of a bias voltage based on the “delta- $V_{BE}$ ” idea, in which the emitter-area ratio  $A_2/A_1$  (sometimes in combination with the resistor ratio  $R_2/R_1$ ) is deliberately made much greater than unity. For example, when the net ratio is set to 48,  $V_{os}$  has a theoretical value of 100.07 mV at 300 K. This voltage will be proportional to absolute temperature (PTAT), which is often the most suitable biasing choice in BJT design. Since its basic value can be precisely determined by a pure ratio, and subsequently

<sup>11</sup> This is a simplification; other factors, including base-width modulation (early voltage) and various on-chip gradients are involved.

multiplied up to a higher value, better suited for IC purposes (say from 300 mV to 1 V) by another pure ratio, we can fundamentally eliminate the sensitivity to absolutes. Incidentally, it will be apparent that the  $\Delta V_{BE}$  concept can be used as the basis of a silicon thermometer, and when implemented using more careful techniques than briefly described here, the voltage can be accurate to within 0.15%, corresponding to a temperature error of < 0.5 K at 300 K.

Finally, in this set of process sensitivities, we must address aspects of circuit performance that are *Sensitive To Mismatches*, which we call “STMs”. Clearly, this includes a great many effects, since the immunity conferred on a circuit function through the use of pure ratios is immediately lost if these ratios are degraded by mismatches. (As used in this frame of reference, the term refers not only to components that should be *equal*, but to the deviation from some *nominal ratio*.) Here again, the strongly Newtonian nature of analog circuits is apparent, since matching accuracy is directly related to device size. It is clear that the greater the number of atoms used to define some parameter, the lower the sensitivity to absolute variations in this number. We are here faced with a very basic trade-off, since the use of large devices, whether passive or active, is at odds with the minimization of inertia,<sup>12</sup> and also with the minimization of die size. In fine-line processes, one is inclined to use small geometries rather uniformly, to achieve the highest speed and packing density; but high accuracy analog design requires careful attention to the *optimal scaling* of devices. Bigger is not necessarily better, however. Even when die size and device parasitics are not critical considerations, the use of excessively large devices can actually cause a *reduction* in matching accuracy as various gradients (doping, stress, temperature, etc.) begin to assert an influence.

This interdependence of circuit design and layout design is found in all integrated circuit development, and serious lapses will occur if they are ever treated as separate and distinct activities, but especially so in analog design. There are many times when one can achieve a very distinct advantage, whether in speed, accuracy, packing density, or robustness, by altering the circuit design to accommodate a more promising layout scheme. Further, the generous use of similar device orientations, sets of physically parallel resistors, and dummy components at boundaries pay significant dividends in preserving analog accuracy.

With some thought, it may be possible to actually avoid the need for transistor matching at all, through the use of dynamic element matching, based either on the better matching that can be achieved between capacitors, or through the use of clever switching of the topology, either to alternate error sources in a

---

<sup>12</sup> A general term favored by the author to describe the net effect of all mechanisms leading to the storage of charge in a device, which causes sluggishness in the response.

cancelling fashion, or by an appeal to averaging. Thus, the most accurate silicon thermometers do not depend on the (still somewhat risky) matching between two separate transistors, which can also be degraded by mechanical strain across the die. (Transistors are always willing to operate as strain gauges.) Instead, a single junction can be used, and biased sequentially at two or more current levels. The integer ratios between these excitation phases can be generated to very high accuracy. The resulting small PTAT voltages are amplified, and subsequently demodulated, by switched-capacitor techniques.

One can implement dynamic band-gap references using similar methods, although in this case there remains an unavoidable dependence on the actual saturation current of the junction,  $I_S(T)$ , which is always a matter of total doping level and the delineation of the junction area. While this DAP remains, there are still further tricks up the analog designer's sleeve to reduce these sensitivities in the design of advanced band-gap references, from "direct" to "diluted", but they cannot be fully eliminated. One can see why this is so, by remembering that the transistor is used essentially as a *transducer*, from the domain of temperature to the domain of voltage. Also, since this  $V_{BE}(I, T)$  is dependent on the *absolute current density* in the device, which in turn depends on some on-chip resistor, it can be stated with certainty that there is no way to design a reference to be inherently traceable to a fundamental physical constant such as the bandgap energy of silicon.

In making trade-offs in device structure, scaling and placement for analog design, one can appeal to *principles* and *guidelines*, but it is unwise to rely on *rules*. Some of the principles of matching are obvious and unequivocal; others tend to be wrapped in folklore, a reflection of the common fact that insufficient statistical data is available to state much with certainty, in many practical cases. This is often because one is designing on a new IC process for which statistically-reliable data has not yet accumulated. Guidelines for matching, which is not a matter of basic circuit design but rather, the design of the layout, are provided in Chapter 33. However, absolute attention to device sizing must be made during the design phase, and very definite parameters assigned to all components prior the Design Review, since one cannot assume the layout designer is a mind-reader. These should not only be embedded in electronic form, in the captured schematics, but should also be immediately visible on these schematic, in the pursuit of total clarity and the elimination of ambiguity, as well as in the spirit of full disclosure of all design issues for peer review, and possible correction.

## 2.4. Robustness, Optimization and Trade-Offs

The expression *robust design* is widely used. We have an intuitive sense of what this means and entails. A robust product is one whose design ensures that

it is not critically dependent on the precise materials used in its construction, and is able to fully perform its intended function under all anticipated operating conditions and endure vigorous environmental forces without significantly affecting its long-term utility. In civil engineering, such as the construction of a major bridge, these would include a consideration of material stress limits in the presence of worst-case traffic loading or unusually severe cross-winds, recognizing the criticality of choosing the construction materials and the actual process of fabrication.

The trade-offs related to robustness that go into the design of a modern ICs are at least as numerous as for large engineering projects, such as bridges and buildings. They may also involve similar concerns for product liability, for example, in components used in medical equipment, or where electromagnetic emanations may pose a threat to a human user.

**A robust circuit design is one in which the sensitivities of critical performance specifications to variances in the manufacturing process and the circuit's operating environment are first fully anticipated and identified and then systematically nulled, or at least minimized, through optimal choices of macro-structure, cell topology, individual device design, component values, bias conditions and layout.**

Can we define a “Robustness Coefficient”? Almost certainly not. Even some sort of “Figure of Merit” is unlikely. Can we delegate the maximization of robustness and its inverse, the minimization of sensitivity, to a computer? Only in a few special and limited situations. This is where one’s mastery of design will play its most indispensable role. Time and again, we find that the search for the most robust solution requires that we know how to shift attention, as circumstances require, from the *whole* to *the parts* and back again to the *whole* – numerous times in the course of the product development. There is a fractal-like quality to analog IC design, in the sense that whether we are viewing it at a high level, wearing the customer’s shoes, or stepping down through many layers of circuit structure and operation, the biasing of its components, device optimization, the physics at the next layer below that, there is at every level a huge amount of information to consider and a great deal of complexity to cope with.<sup>13</sup>

It is important to understand the distinctions between robustness, optimization and trade-offs. While these topics overlap very considerably, they stem

---

<sup>13</sup> Again, we may note that, once one gets down to the gate level, there is little to be gained, in the pursuit of digital system design, by probing deeper into structure.

from quite different impulses. As we have seen, robustness is a *state*; it is the outcome of pursuing analytical methods, simulation studies, and the selection of technologies, architecture and scaling and judgments in the course of a product design. The threads leading to this result will lead back to many sources, but most notably from the pursuit of optimization and the making of trade-offs.

Optimization is a *process*. It is the analytical consideration of a system and its parameters with a view to discovering local minima and maxima in  $n$ -space (where in practice  $n$  is often much greater than 2) which can be identified in some particular way as the best choice(s), where the performance aspects of special interest are closest to what can ever be achieved within the constraints of a given architecture, technology or specific component limitations. This is a methodical, systematic process very amenable to mathematical representations or, more commonly, numerical methods. Thus, optimization is an *algorithmic process*. Since the representational equations “know” nothing about the world beyond their  $n$  dimensions, there is no expectation of discovering new worlds of possibility; maxima and minima never turn into wormholes.

Consequently, one can never be sure that the solution offered by an optimization process is truly the *best of all possible choices*: it is only the best of a severely limited sub-set of choices. In this sense, it is as much the product of the framer of the algorithm as of the data. Further, numerical optimization provides little if any insight into extending performance beyond these boundaries, and because an analysis does not include all the variables, it may not even be finding the actual best case in practice. This will frequently be true even for rudimentary circuits, such as a cell-phone power amplifier. Finally, there is a strong likelihood that the under-skilled user of optimization procedures (“design programs”) will believe that the “answer” is genuine and reliable, while learning nothing in the process.

In contrast, the act of making a trade-off is *no sense* algorithmic. Trade-offs require a human *decision*, namely, the difficult and vexing choice between two or more *equally attractive alternatives*, and the sacrifice of one good for another. It is a zero-sum game. It involves risk and calls for judgment. In this common situation, there are no rules to lean on; if there were, the next step in a design would not be a trade-off, but the mechanical, unthinking application of some such rule. In the end, all decisions are emotional.<sup>14</sup> Many engineers are inclined to reject this tenet, proclaiming that this may be so in the social world, but not in technology, where each step in a development proceeds logically. However, it does not take many years practicing design to see the truth of this statement. When all the evidence, facts and analyses point clearly and unequivocally to a single, definite course of action, no decision is needed: that

---

<sup>14</sup> Due to Edward de Bono, a professor of psychology at Oxford University.

is optimization. But in the many cases where the data are flat, equally favouring many possible ways forward, a decision is called for. *That is* a trade-off.

It may even be a coin toss. In developing a standard linear product, having a wide applications domain, but lacking all the required market data, the designer is often forced to make guesses, based on personal “market savvy” and experience as to the most useful combination of performance parameters. One frequently needs to decide whether to pitch the product toward leading edge performance and stop worrying about its 50 mA supply current, or toward portable applications, by halving the current and accepting that performance will suffer. Similar trade-offs will arise between using bare-bones, ultra-cheap design practices with a view to achieving the smallest possible die area, in order to be competitive in pricing the product, or err on the side of extending the feature set and improving the performance, to extend the applications space, and considering such factors as ease of use and customer satisfaction. There are no algorithms for success.

### 2.4.1. Choice of Architecture

We will now look at several case histories, to illustrate the meaning of robustness in more concrete terms. In doing so, we will appreciate how elusive a quality it can be. To achieve the most satisfactory overall solution requires that numerous parallel and competing factors need to come into focus into a unified vision of the whole. Many trade-offs, which are open-ended decisions, are needed.

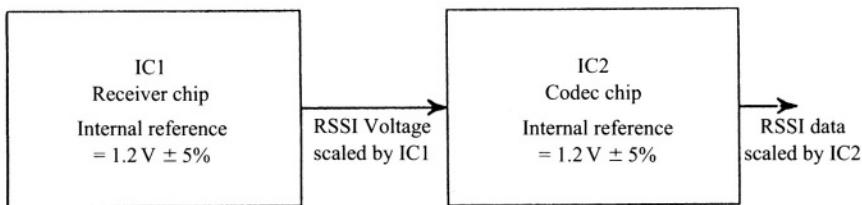

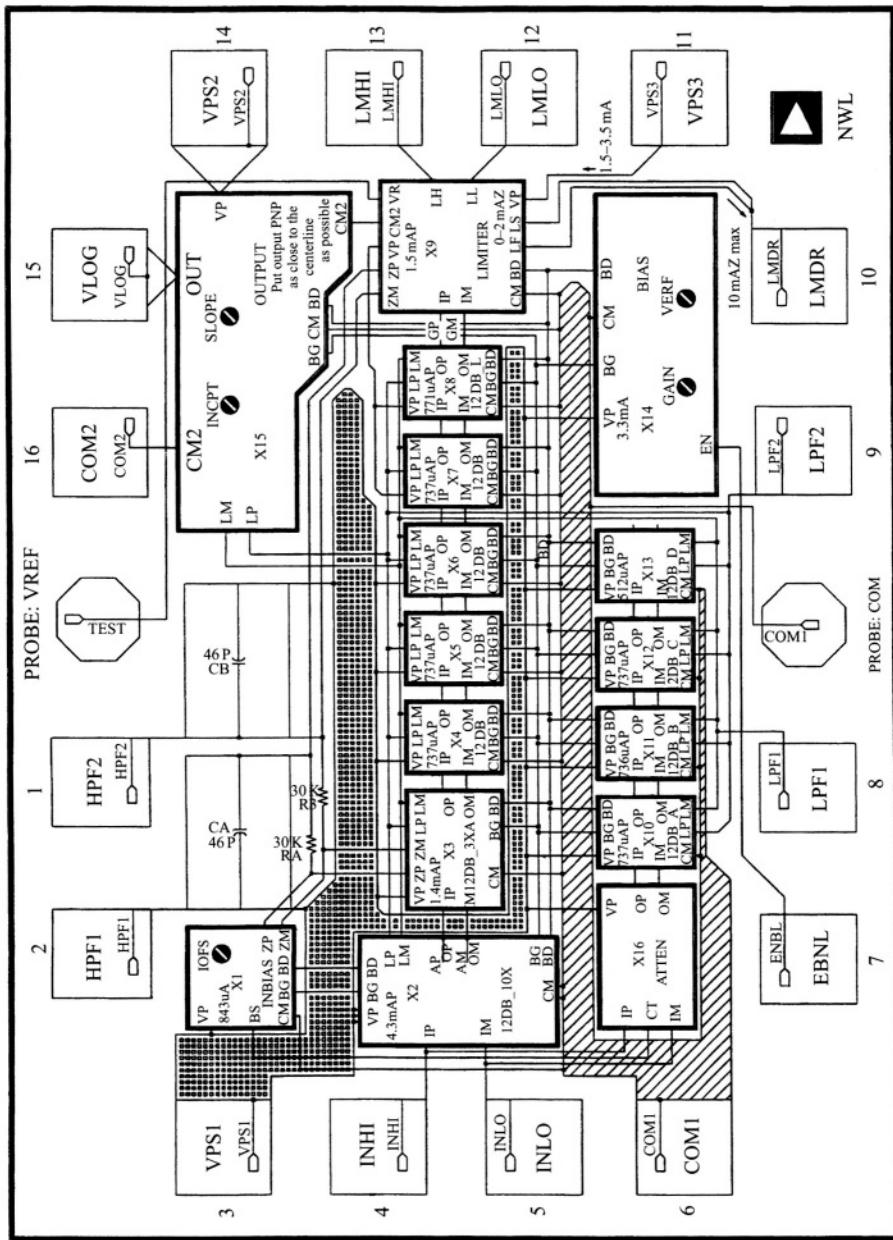

Clearly, we need to start with a robust architecture. Of the numerous ways we can satisfy a system requirement, some will be more sensitive to slight changes in parameter values than others. A simple example is provided by a cellular phone system involving a limiting IF with an received signal strength indication (RSSI) output (Figure 2.2). In this example, the RSSI output voltage – which reports to the cell supervisory system the strength of the received signal, in order to minimize the transmit power in the handset and at the base station – is scaled by a band-gap reference voltage, generated in the receiver sub-system. This voltage is then measured, and converted to digital form, by another IC, a codec, in which a second bandgap generator is embedded. Either or both of these circuits may be built in CMOS, a technology which is not noteworthy for high reference-voltage accuracy.<sup>15</sup> A guaranteed absolute accuracy of  $\pm 5\%$  in

---

<sup>15</sup> See B. Gilbert, “Monolithic voltage and current references: theme and variations,” in: J. H. Huijsing, R. J. van de Plassche, and W. M. C. Sansen (eds), *Analog Circuit Design*, pp. 269, which includes further examples of good and bad planning in the use of voltage references.

Figure 2.2. A vulnerable approach to scaling of nonlinear circuits.

Figure 2.3. Use of a common reference voltage removes uncertainties in scaling.

each reference is a reasonable objective if high yields are to be achieved and the cost objectives do not allow trimming.

There could have been historical reasons for the use of this approach. For example, one circuit may have been designed ahead of the other, as part of a separate venture. Clearly, in this scenario, there is a worst-case error in the RSSI calibration of  $\pm 10\%$ . If this occurs at the top end of a receiver's 70 dB dynamic range, the measurement error could amount to  $\pm 7$  dB. In this scheme, there is also some yield loss due to the use of at least one redundant reference generator. Finally, it is possible that the uncorrelated noise of the two independent references could lead to LSB instabilities in the measurement; this may be especially troublesome where there is a high level of flicker noise, as in a pair of CMOS bandgap references.

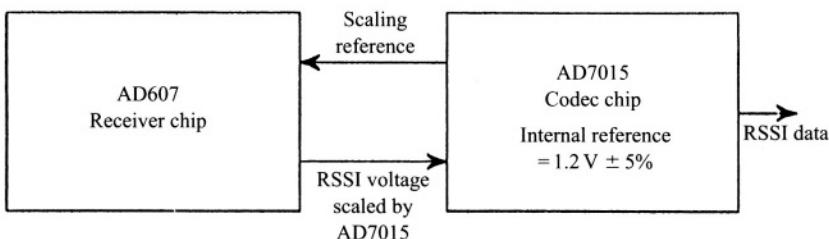

Figure 2.3 shows a first alternative, in which only a single reference is used. This method is used in the Analog Devices AD607 single-chip superhet receiver. The mixer and linear IF strip are provided with a linear-in-dB gain control (AGC) function, the scaling reference for which is derived from the companion codec (AD7015). The error in that reference is now inconsequential, since it alters both the scaling of the RSSI output (so many mV/dB) and that of the ADC in the codec (so many LSBs per mV). Here, we have a classic example of the minimization of sensitivities through a dependence on ratios at the *system level*. The revised approach can allow much looser tolerances on

Figure 2.4. Absolutely calibrated voltage references are often quite unnecessary.

the remaining reference, if accuracy is not needed for any other purpose. Close matching of resistor ratios (utilizing unit resistors throughout) results in a high overall RSSI measurement accuracy, from antenna to bits. There sometimes is a case to be made for using more than one voltage reference circuit within the confines of a single IC. These cells are invariably quite small, and the isolation resulting from using separate cells is valuable. But these situations generally arise in less-critical systems. For example, in extensive tracts of current-mode logic, local cells are used for biasing.

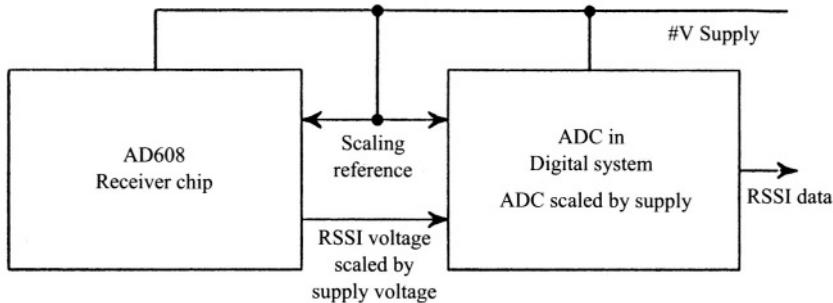

In some cases, an even simpler solution is possible. This is the use of the raw supply voltage to scale both the RSSI function and the ADC (Figure 2.4). This approach is used in both the AD606 (a Log-Limiting IF Strip) and the AD608 (a Single-chip Superhet Receiver with Log-Limiting IF Strip). The RSSI output is scaled directly by the raw supply voltage, but this is also used by the ADC as its scaling reference. Thus, both bandgaps have been completely eliminated, with no loss of accuracy, as well as their supply current, die area, bonding pads, package pins and attendant ESD concerns, and guaranteed robustness. The only trade-off in this case is only that the components must be used in partnership. This slight loss of flexibility is never of great concern in high-volume system-oriented products.

#### 2.4.2. Choice of Technology and Topology

Early in the design planning, we will select an appropriate technology for an IC product, based on issues of target cost, performance objectives, production capacity, time to market (and the possibility of cell re-utilization) and other issues of a strategic nature. In some cases, we will have little choice but to use a foundry process. We then start looking for robust circuit topologies – structures which have demonstrated low sensitivities to the absolute value of the individual passive components (minimizing the DAPs), and low sensitivities to mismatches, supply voltage and temperature (TAPs and STMs). The design

principles are invariably the same: lean heavily on the use of ratios wherever possible, in the pursuit of TAPs; adopt sensitivity analyses and chose low-sensitivity cells in the case of DAPs; use careful layout techniques to address the STMs.

A couple of examples of techniques that address robustness will be presented. In the second of these, we will consider a rudimentary voltage-mode amplifier based on a pair of bipolar transistors with resistive loads. Open-loop amplifier cells of this sort are often deprecated, partly because of concerns about gain accuracy. Rather, the common tendency is to appeal to the use of op-amp techniques, in the belief that they automatically circumvent such problems, and conveniently transfer the attainment of high gain accuracy to the ratio of just two resistors. Occasionally, this may be effective, if the op-amp has sufficient open-loop gain at the frequency of operation. But this is often not the case in practice.

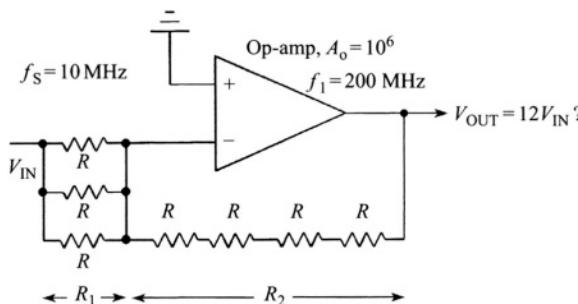

Indeed, one of the worst analog-circuit myths is the notion that the chief value of an op-amp is its “very high open-loop gain”. Suppose we have an op-amp cell that has been proven to have a reliable DC gain of  $10^6$  and a *nominal* unity-gain frequency of 200 MHz, and we are planning to use this cell to realize an amplifier having the (seemingly low) numerical gain of  $\times 12$  at 10 MHz. We choose the feedback ratio accordingly. For an inverting configuration, the input resistor  $R_1$  might be  $1\text{ k}\Omega$  and the feedback resistor to the summing node  $R_2$  would be chosen as  $12\text{ k}\Omega$ . With robustness in mind, we might decide to make  $R_1$  as 3 units of  $3\text{ k}\Omega$  in parallel and  $R_2$  as 4 units of  $3\text{ k}\Omega$  in series (Figure 2.5), use a generous width, and make sure the layout designer puts these resistors side by side, even interdigitates them and adds dummy resistors at each end to further ensure the ratio accuracy.

Then, in simulation (or perhaps in a bench experiment) we find that the actual gain is much lower; instead of  $\times 12$  it is found to be only  $\times 9.6$ . Why? Because the open-loop  $A_{OL}$  gain *at frequency* is only 200 MHz/10 MHz, or merely  $\times 20$ ,

Figure 2.5. A fixed-gain amplifier designed to be robust: but is it?

assuming the usual case of dominant-pole compensation. At this juncture, one might decide to just make a correction to  $R_2$ , of slightly more than the wanted-to-actual gain ratio 12/9.6, to compensate for the lower  $A_{OL}$  at 10 MHz. Either through the use of vector arithmetic or simulation, we find that  $R_2$  needs to be raised to  $16.44\text{ k}\Omega$ . This is no longer a low-integer ratio, but we choose to now use a total of *five* units for  $R_2$ , extending the length of each element by 9.6%, from 3 to  $3.288\text{ k}\Omega$ . A small change in the length (keeping the width constant) will not seriously jeopardize the ratio, because this dimension will invariably be relatively large. For example, using a sheet resistance of  $1\text{ k}\Omega/\text{square}$  and a width of  $10\text{ }\mu\text{m}$ , the length increases from 30 to  $32.9\text{ }\mu\text{m}$ , (the nearest  $0.1\text{-}\mu\text{m}$  increment, resulting in an error of  $+0.06\%$ ).

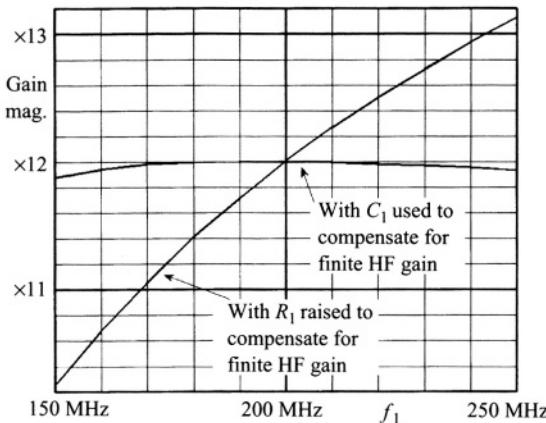

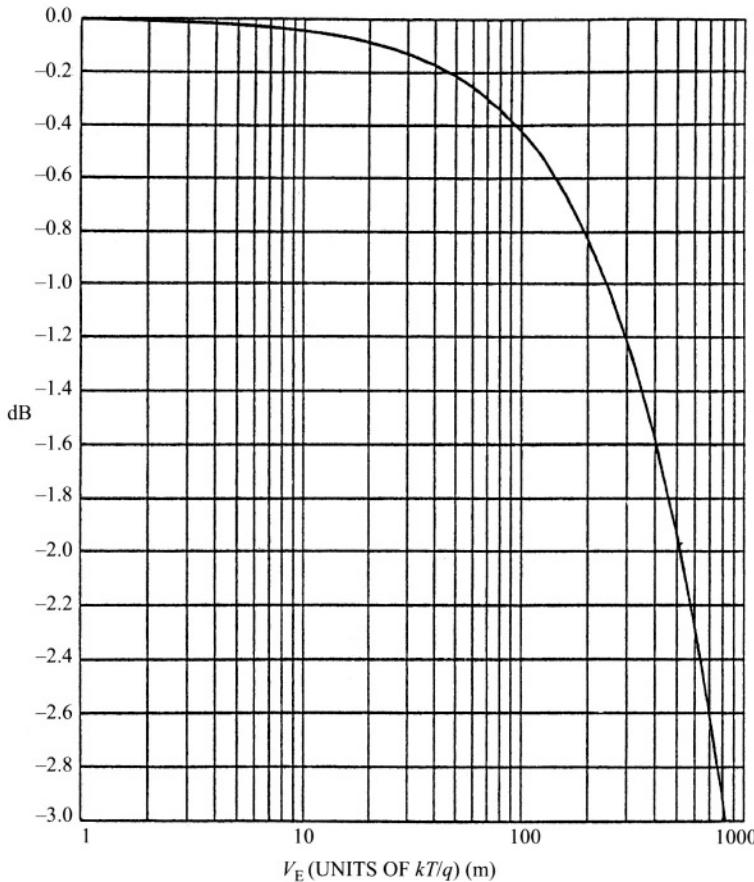

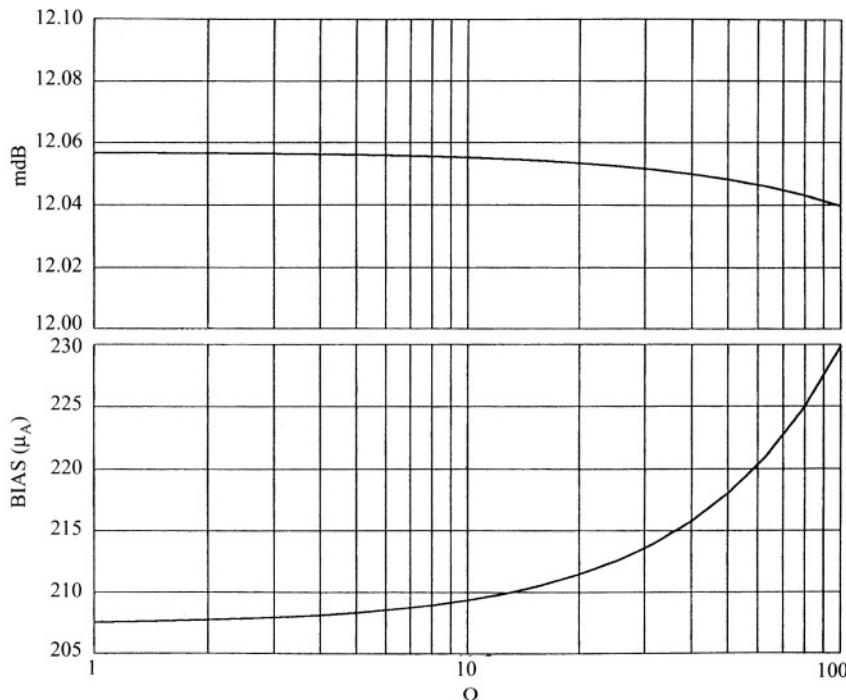

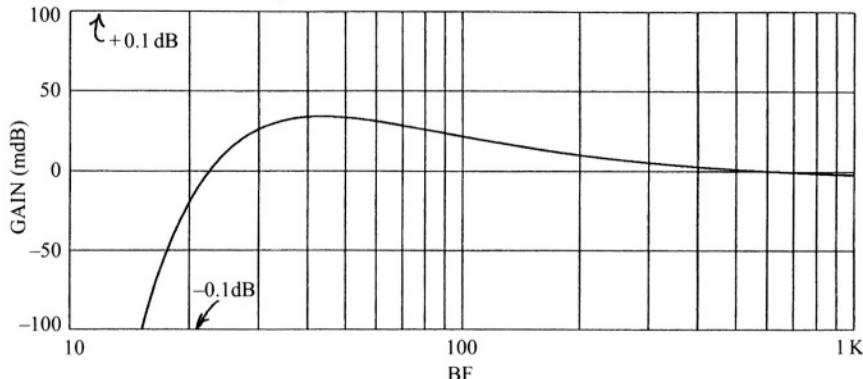

We may think we are pursuing a sound “TAP” approach in using these “ratio-based” tactics, but this would overlook the important fact that the unity-gain frequency  $f_1$  of the op-amp is itself a “DAP”, being subject to variations in the on-chip resistor that determines the bias current and thus the  $g_m$  of the input stage, and variations in the on-chip capacitor; together these set the unity-gain frequency,  $f_1$ , which can easily vary by up to  $\pm 40\%$  in production. Therefore, a *one-time adjustment* to the resistor ratio cannot guarantee accurate closed-loop gain at 10 MHz over all production units. In fact, the gain will vary from  $\times 10.3$  to  $\times 13.2$  over the lesser  $f_1$  range of 150–250 MHz, a variation of only  $\pm 25\%$  (Figure 2.6).

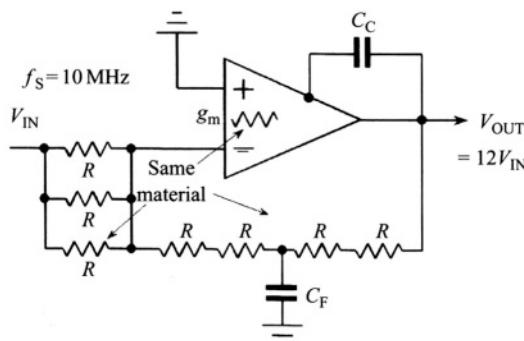

There are several ways in which this particular problem might be solved in practice. The preferred solution, whenever one has control over the complete ensemble, is to lower the op-amp’s internal compensation capacitor and substantially raise the  $f_1$  to a value better suited to the specific application of the amplifier cell, which no longer requires it to provide HF stability at all gains down to unity. Another solution, chosen to illustrate how robustness can often be achieved by the use of like effects, is shown in Figure 2.7. A second on-chip

Figure 2.6. Improved amplifier using carefully-scaled bandwidth compensation.

Figure 2.7. Simulation results for original and improved amplifiers.

capacitor  $C_F$  has been added at the junction of the two halves of  $R_2$ . If we make this component out of the same units as the internal HF compensation capacitor and also make the resistor that sets the bias, and thus  $g_m$ , of the input stage out of the same material and similar-sized units as  $R_1$  and  $R_2$ , we can achieve a useful desensitization of the closed-loop gain at the presumed signal frequency of 10 MHz. Now we are *matching time-constants*, and on the path toward a true TAP situation.

It is useful to show how this improvement in robustness is obtained. We begin by modeling the op-amp's forward gain as that of an inverting-mode integrator  $-1/sT_1$ , and define the feedback time-constant as  $T_F = R_2 C_F / 2$ , and the magnitude of the closed-loop DC gain as  $G_0 = R_2 / R_1$ . The transfer response of this circuit is

$$G(s) = \frac{-G_0 (1 + sT_F)}{1 + (1 + G_0) sT_1 + (1 + G_0) s^2 T_1 T_F} \quad (2.2)$$

This is a two-pole response with a  $Q$  of  $T_F / T_1$ . Thus, we can rewrite (2.2) as

$$G(s) = \frac{-G_0 (1 + sQ T_1)}{1 + (1 + G_0) sT_1 + (1 + G_0) s^2 Q T_1^2} \quad (2.3)$$

It is easy to hold the ratio  $Q$  to within fairly narrow limits, since both  $T_1$  and  $T_F$  are generated by CR combinations having exactly the same process sensitivities. For operation at a specific frequency, such as 10 MHz in this example, our only remaining concern is the *absolute value* of both time-constants, represented in (2.3) by the single integrator time-constant  $T_1$ . If we were concerned with the broadband response, we would choose to use a low  $Q$ ; but since the

main objective in this illustrative example is presumed to be the desensitization of  $G(s)$  to the actual value of  $T_1$  over a narrow frequency range, we may find it beneficial to use a somewhat higher  $Q$ .

Suppose we decide to make the magnitude of the gain  $G(s)$  at the operating frequency equal to the target (DC) gain  $G_0$ . Solving (2.3) for  $Q$  we obtain

$$Q = \frac{1 + G_0}{1 - (1 + G_0) s T_1} \quad (2.4)$$

Thus, for  $s T_1 = 10 \text{ MHz}/200 \text{ MHz} = 0.05$  and  $G_0 = 12$ , the optimal value of  $Q$  is 32.5. From (2.4) it also follows that this compensation scheme cannot be used above

$$s T_1 = \frac{1}{(1 + G_0)} \quad (2.5)$$

For the target gain of  $\times 12$ , this technique can provide accurate compensation only up to  $200 \text{ MHz}/(1 + 12) = 15.4 \text{ MHz}$ , at which frequency the  $Q$  would be dangerously high.

We might also determine the sensitivity to the value of  $T_1$ , and set that to zero. One could spend a few hours in this sort of analytical wonderland, but it would not be very helpful in providing practical insights. It is often the case that the actual operating conditions differ from those assumed at the start of a project, and all the effort poured into a specific analytical solution needs to be repeated. A more efficient way to explore the general behavior of such compensation techniques is invariably through *creative simulation*. The results that were shown in Figure 2.6 required about a minute of experimentation and optimization in real time (the maths shown above took considerably longer to go through). They demonstrate that, with the optimum choice of  $C_F$  and a small adjustment to  $R_2$ , good stability in the magnitude of the gain at 10 MHz ( $+0/-1\%$ ) is possible over a  $\pm 25\%$  range of  $f_1$ , which represents the bulk of the yield distribution of a production op-amp.

In this brief exercise, we were able to convert troublesome DAP behavior into a benign TAP form; that is, we ensured an accurate gain at a significant fraction of the op-amp's unity-gain frequency, with a near-zero sensitivity of gain to that parameter at the chosen frequency. Even when a higher  $f_1$  is employed, which, as noted, would be the preferable solution to minimizing this sensitivity, the addition of  $C_F$  would still be useful in further improving robustness in production, and at very little cost in die area, and at no cost in power consumption. By contrast, solutions based on further increasing the op-amp's  $f_1$  will incur power penalties, within a given technology.

An excessive reliance on small-signal modeling with linear equations, and the use of small-signal simulation, is always a *very* risky business. Unfortunately, these methods are widely used in many theoretical treatments of circuits

found in the academic literature to the neglect of the consequences of variations in circuit dynamics caused by perturbations in the working point, a result using signals of practical magnitude. Small-signal analyses and simulations totally hide numerous such effects.

It is common for device nonlinearities to introduce gain variations of a significant fraction of a decibel over the voltage (or current) swing corresponding to the full output of the circuit. This is the domain of nonlinear dynamics, which is invariably intractable using standard mathematical tools, while posing no problems to a simulator. Thus, one should spend relatively little time using simplistic frequency sweeps (“Bode plots”) examining the gain magnitude and phase at some nominal bias point, and *far more time* in various kinds of dynamic sweeps. These include full transient simulations, pushing the circuit to confess its secret weaknesses, not only for comfortable operating conditions, but also at the extreme limits of the process, voltage and temperature (PVT) range, with comprehensive package models,<sup>16</sup> for worst-case source and load impedance, and the like. This issue is revisited in Section 2.5.7.

### 2.4.3. Remedies for Non-Robust Practices

One of the most intensively studied design topics is that of active filters, of both continuous- and discrete-time types, reflecting their importance in all fields of electronics. The better texts on the subject emphasize the need to choose topologies and/or component values *that formally* minimize the sensitivity of the dimensionless specifications, such as gain and the geometric disposition of poles and zeroes. Unfortunately, these same authors often show a poor appreciation of the need to convert a beautiful “minimum-sensitivity” design (in the strictly mathematical sense) into a practical, *manufacturable* entity.

For example, there is little point in concluding that the optimal (least-sensitive) solution is one in which, say, resistors of 5.3476, 1.0086, 1.7159 and  $8.1030\text{ k}\Omega$  are needed, along with capacitors of similarly exotic values. Such component precision can rarely be met even in a board-level design. The chief appeal of text-book filter functions, such as the well-known Bessel, Butterworth and Chebyshev formulations, is simply that they are *mathematically tractable* and enjoy a certain sort of canonic rigor. But in these days of very fast computers and simulators, there is no compelling reason to stick to classical forms.

---

<sup>16</sup> It is essential to keep well in mind that circuits do not know what they’re *supposed* to do, and design mastery entails making sure that transistors dance to *your* tune, not theirs. Thus, if you are using a common 25 GHz IC process to realize, say, an audio amplifier at the tail end of a receiver, the circuit will surely promote itself to a microwave oscillator, unless you pay attention to easily-forgotten parasitic effects having no essential relevance to your intended application.

The art of designing *manufacturable* filters begins with the sure expectation that some slight departure from the “ideal” (often over-constrained) response will be forced by the difficulty of actually realizing non-integer element ratios to high accuracy in a production context, and that it will be necessary to juggle the partitioning and topologies so as to force a solution using *simple integer ratios of Rs and Cs*. In modern filters, this paradigm is less often practiced in the design of continuous time filters than in switched capacitor filters. The most likely explanation is that the former were developed in the age of electrical theory, while the latter arose in an intensively pragmatic context, where it was known from the outset that unit replications would be essential to robustness.

The approach to monolithic filter design thus *starts with a trade-off*, namely, the need to set aside the text-books, and cut loose from the canonic rigor presented in the filter design literature. The ensuing design exercises may involve a considerable amount of “inspired empiricism” using the simulation of cells containing only element ratios that one knows can be reliably reproduced in high-volume production. Such an approach is straightforward for low-order filters, but can quickly become very difficult when advanced filter functions must be provided. However, in such cases, it is usually possible to create some adjunct routines to perform algorithmic optimization in a few minutes of unattended computer operation. Because filters are invariably required to be linear, the computational burden can be greatly simplified by the temporary use of idealized active elements in SPICE, or the use of a platform such as MathCad.

It should be realized that this is just a starting point, and it is important to note that an appeal to empiricism should not be confused with guessing, or even worse, lazy-mindedness. It simply recognizes that situations often arise in which systematic and analytic methods are either inadequate to the task at hand, or become too cumbersome to provide the needed rate of progress in a product development, or fail to generate insights that can be translated into practice. After empirical methods have pointed the way forward, it remains the responsibility of the designer to ensure a controlled and predictable outcome in the face of production tolerances. Empirical searches for manufacturable solutions are in no way a *substitute* for robust design based on fundamental considerations, but they are needed to explore the use of (and the invention of) more robust cell structures. Diligence will always be needed thereafter to preserve low sensitivities and reproducibility.

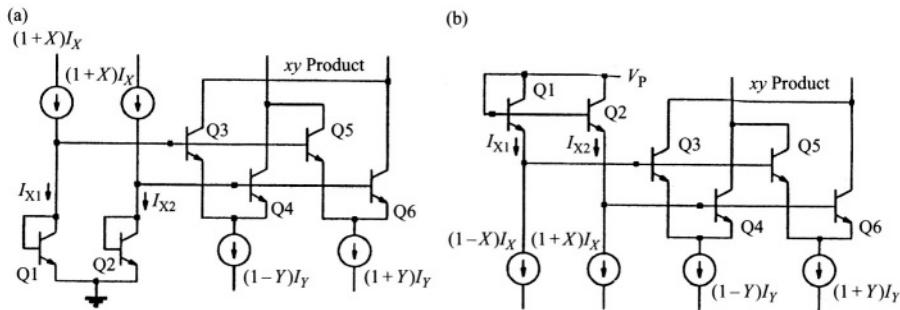

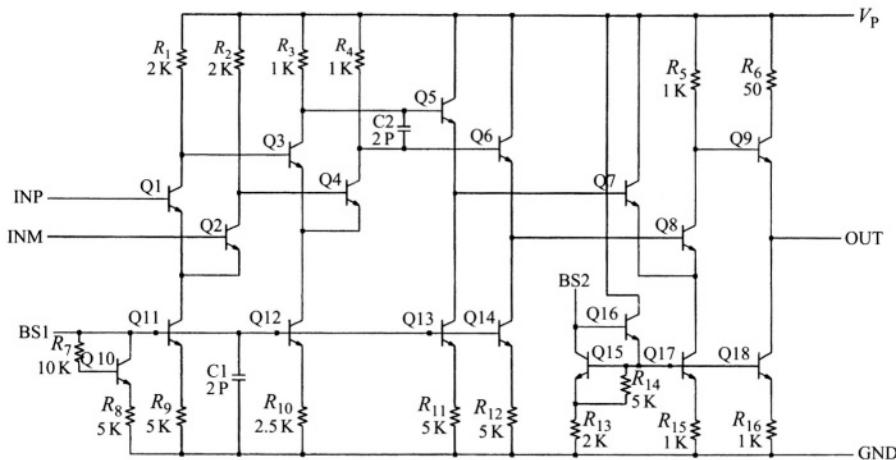

Some analog cells are inherently robust while others, that may quite appear similar, are not. Figure 2.8 shows two translinear multiplier cells.<sup>17</sup> The (a) form

---

<sup>17</sup> See B. Gilbert, “Current-mode circuits from a translinear viewpoint: a tutorial,” in: C. Toumazou, F. J. Lidgey, and D. G. Haigh (eds), *Analogue IC Design: The Current-Mode Approach*, Chapter 2 IEE Circuits and Systems Series, vol. 2, Peter Perigrinus, 1990.

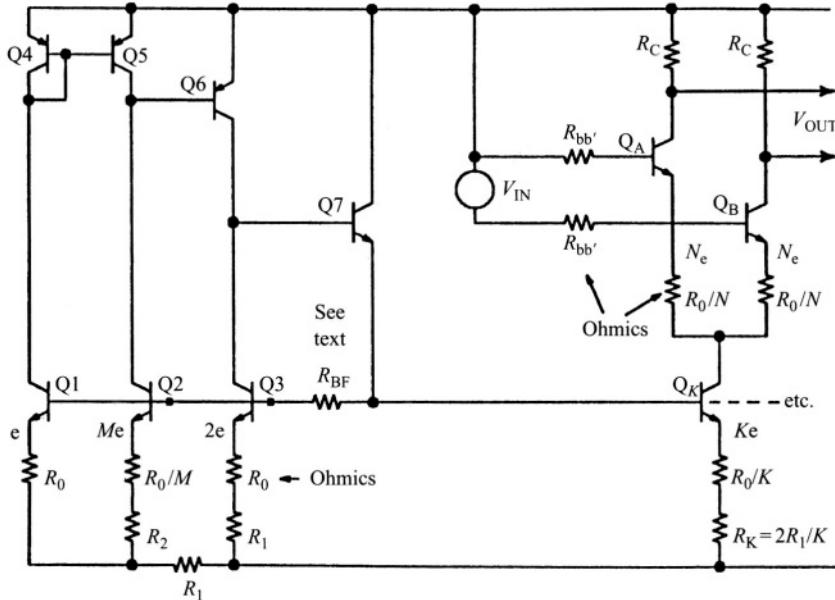

Figure 2.8. Two fundamental multiplier cells; (a) beta-immune, (b) beta-prone.

is called “beta-immune”, because its scaling is very little affected by BJT current-gain,  $\beta$ , and can remain accurate even when  $I_Y$  is almost as high as  $\beta I_X$ . The (b) form is called “beta-prone”, because its scaling is sensitive to beta, even for much less demanding bias conditions, for example, when  $I_Y = I_X$ .

The explanation is straightforward: in (a) all the base currents in Q3–Q6 are in phase with the corresponding currents in Q1 and Q2, and the ratios of  $I_{E3}/I_{E4}$  and  $I_{E5}/I_{E6}$  remain strictly equal to  $I_{E1}/I_{E2}$ . Assuming the betas are essentially equal and independent of current, the input-linearizing transistors are not affected by the reduction in the *absolute* bias levels due the current robbed by the bases of Q3–Q6, because these are in exactly the same ratio as  $I_{X1}/I_{X2}$ . On the other hand, in the (b) cell, the base currents are out of phase with the inputs, and the ratio  $I_{E1}/I_{E2}$  is therefore not equal to the input-current ratio. The overall consequence is that the scaling of the (a) cell includes the factor  $1/(1 + 1/\beta)$ , while for the (b) cell this factor is approximately  $1/(1 + 3/\beta)$ . Here we have a good example of a *trade-off in topology*. In practice, the (b) form is easier to drive (from voltage-to-current converters using the same device polarities for both the  $X$  and  $Y$  signals) than the (a) form, and the literature shows that the (b) cell has almost universally been chosen in monolithic analog multipliers because of this topological advantage, at the expense of static accuracy, temperature stability, intermodulation and slightly higher noise (due to the base currents of the core transistors). However, the beta-dependent scaling can be easily compensated in the synergistic design of the associated voltage reference.

#### 2.4.4. Turning the Tables on a Non-Robust Circuit: A Case Study

This lesson underscores the general point. Good topologies and biasing practice are fundamental requirements in the pursuit of sensitivity minimization, in

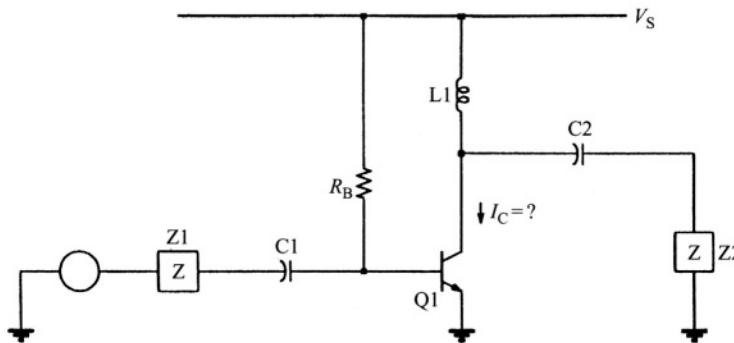

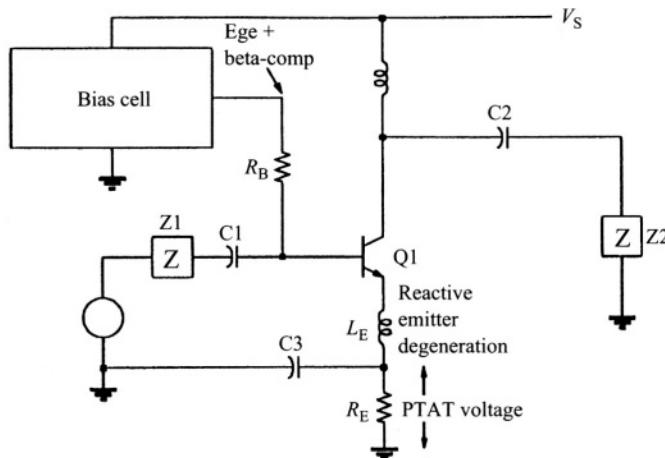

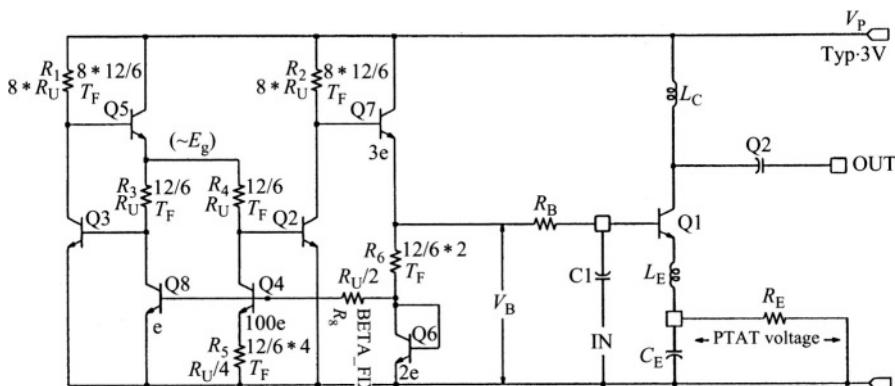

Figure 2.9. An LNA having inadequate attention to biasing.

the face of every sort of environmental factor, notably “P” (lot-to-lot production spreads leading to absolute parameter uncertainties), “V” (supply voltage) and “T” (temperature). In numerous cases, we would have to add “M” (matching) as one of these factors, though not in the following case study. Figure 2.9 shows the circuit, a low-noise RF amplifier (LNA). The topology used here is open to criticism, although the form was once widely used. The behavior of this *one transistor* circuit can be surprisingly complex, and abounds with trade-offs and compromises. It is often nonchalantly presented in articles with almost total emphasis on its high-frequency aspects and hardly any on the crucial matter of choosing and regulating the bias point. It amply illustrates the peculiarities of analog design.

We will focus here on the biasing methods. The general method shown, and regrettably still all-too-often employed in discrete-transistor RF design, uses a high-value resistor  $R_B$  taken directly to the supply voltage,  $V_S$ , in order to establish the collector current  $I_C$ . This immediately introduces serious and quite unacceptable sensitivities, of at least four kinds.