# Introduction to on-chip interconnect

Lecture 7

Professor Kjell Jeppson

Chalmers University of Technology

# Outline

- Introduction

- Interconnect Modeling

- Wire Resistance

- Wire Capacitance

- Wire RC Delay

- Elmore delay model

- Handling wires with branches

# Introduction

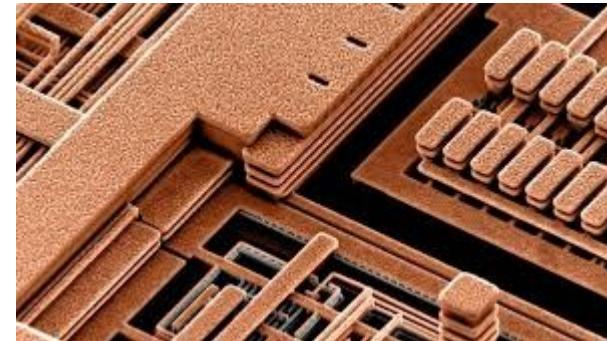

- Chips are mostly made of wires called *interconnect*

- In stick diagram, wires set size

- Transistors are little things under the wires

- Many layers of wires

- Wires are as important as transistors

- Speed

- Power

- Noise

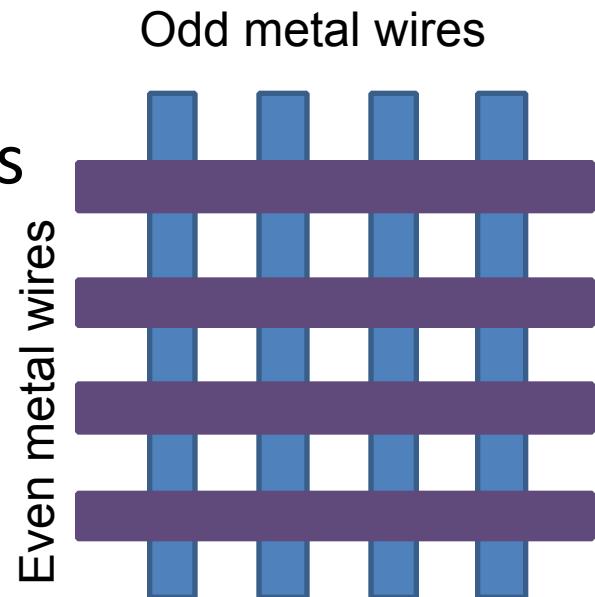

- Alternating layers run orthogonally

# Choice of metals

- Until 180 nm generation, most wires were aluminum

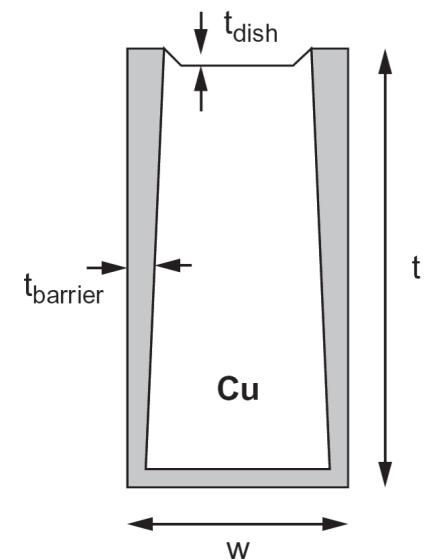

- Contemporary processes normally use copper

- Cu atoms diffuse into silicon and damage FETs

- Must be surrounded by a diffusion barrier

| Metal         | Bulk resistivity ( $\mu\Omega\cdot\text{cm}$ ) |

|---------------|------------------------------------------------|

| Silver (Ag)   | 1.6                                            |

| Copper (Cu)   | 1.7                                            |

| Gold (Au)     | 2.2                                            |

| Aluminum (Al) | 2.8                                            |

| Tungsten (W)  | 5.3                                            |

| Titanium (Ti) | 43.0                                           |

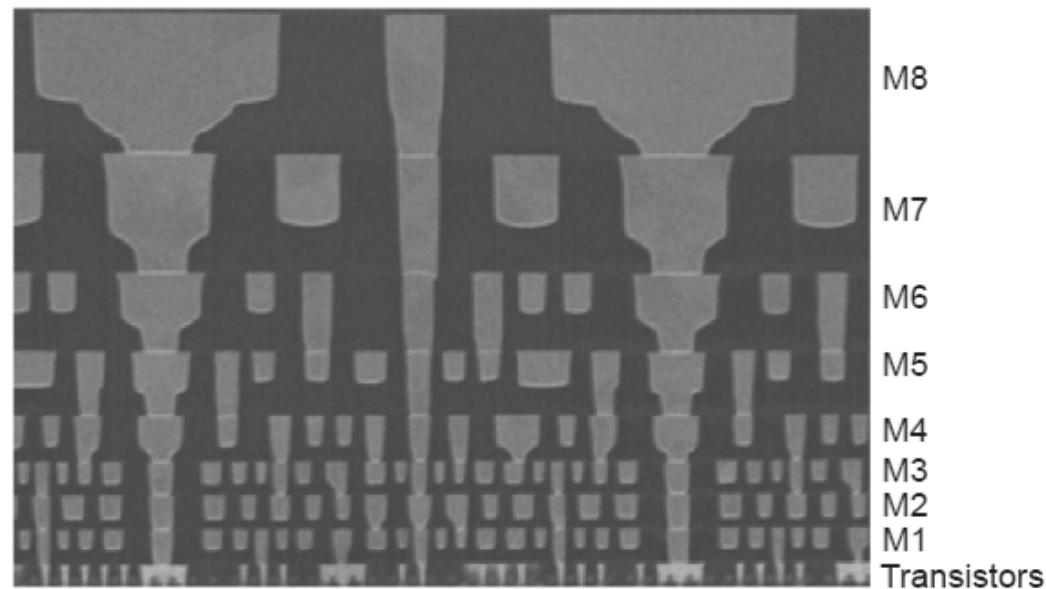

# Layer stack

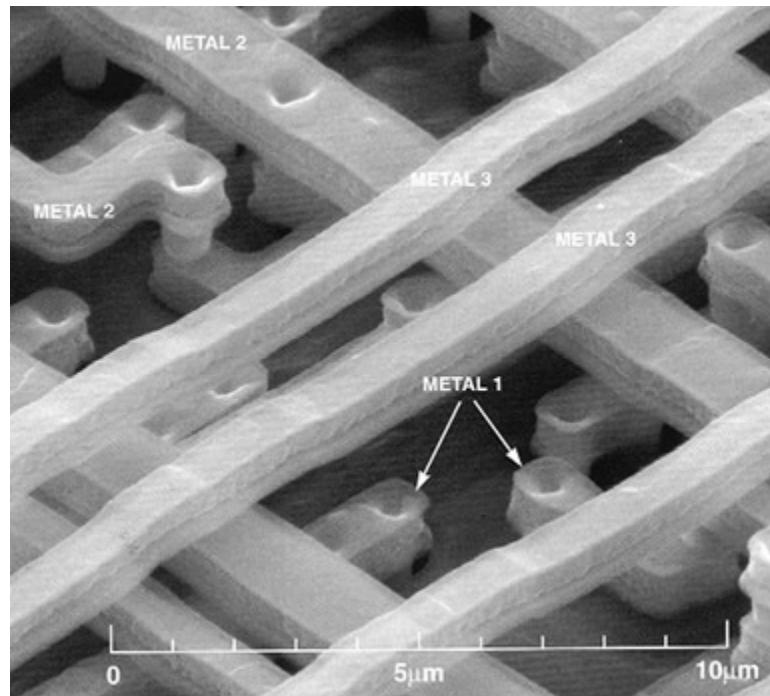

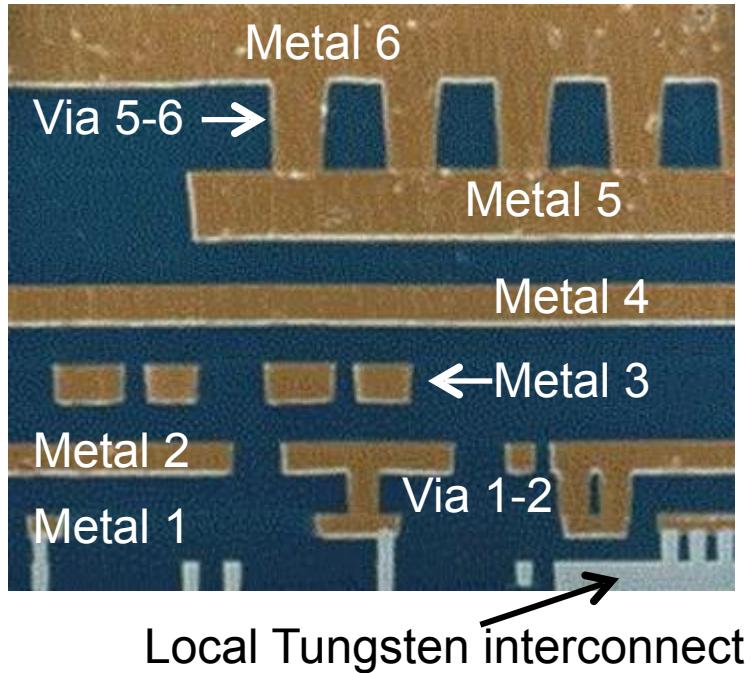

- AMS 0.35  $\mu\text{m}$  process has 3 metal layers

- M1 for within-cell routing

- M2/M3 for vertical/horizontal routing between cells

- Modern processes use 6-10+ metal layers

- M1: thin, narrow ( $< 1.5 \times$  minimum feature size)

- High density wiring in cells

- Mid layers: thick, wide

- Global interconnect

- Top layers: THICK, WIDE

- For  $V_{DD}$ , GND, clk

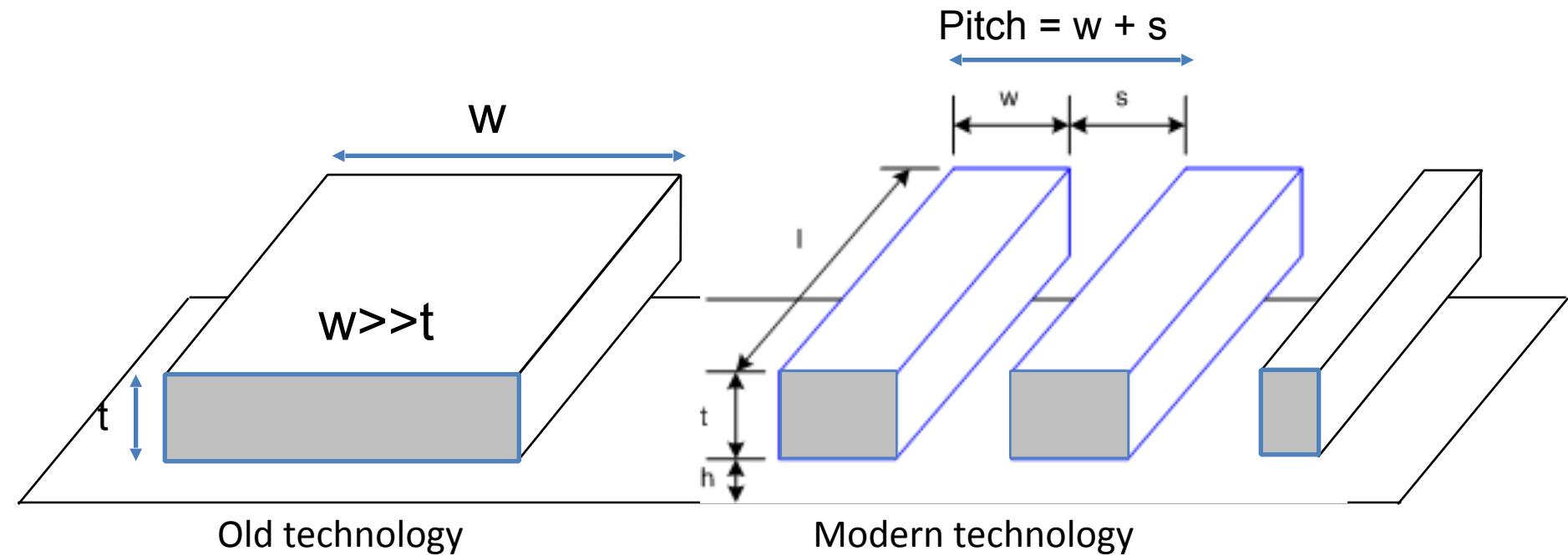

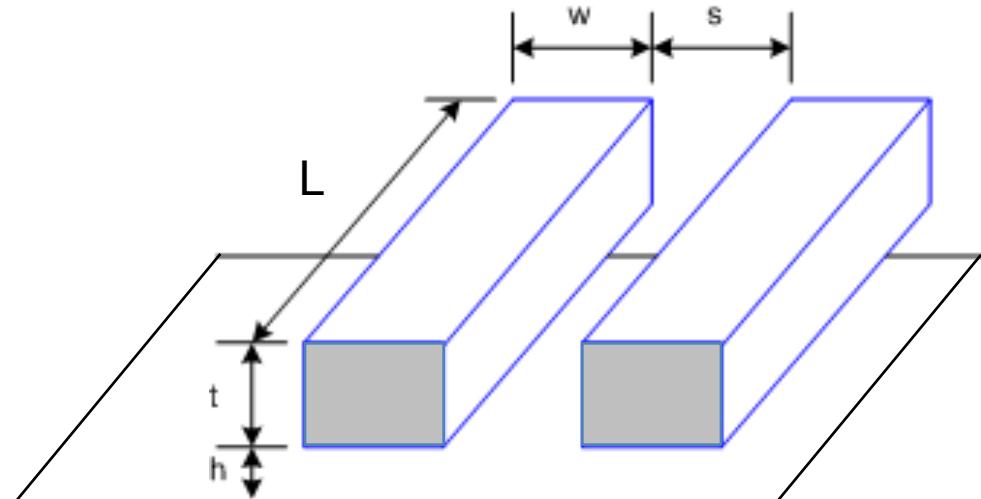

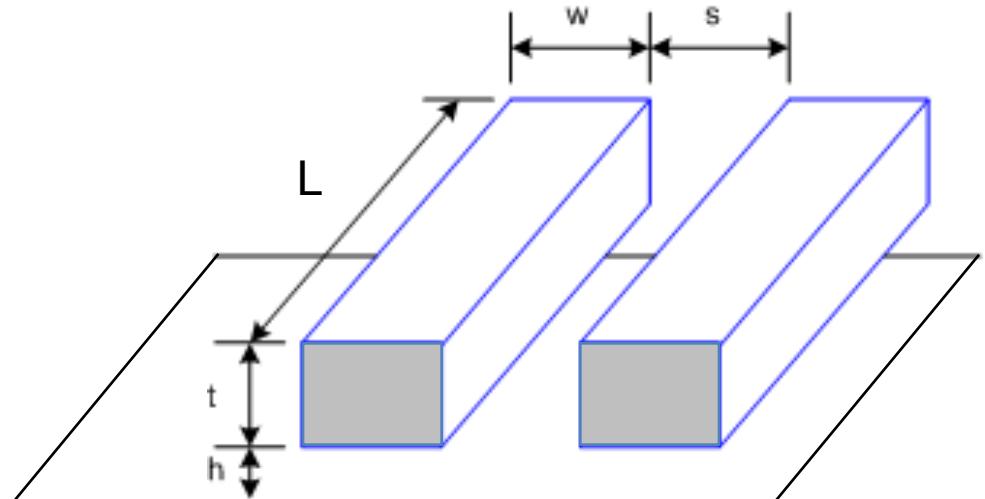

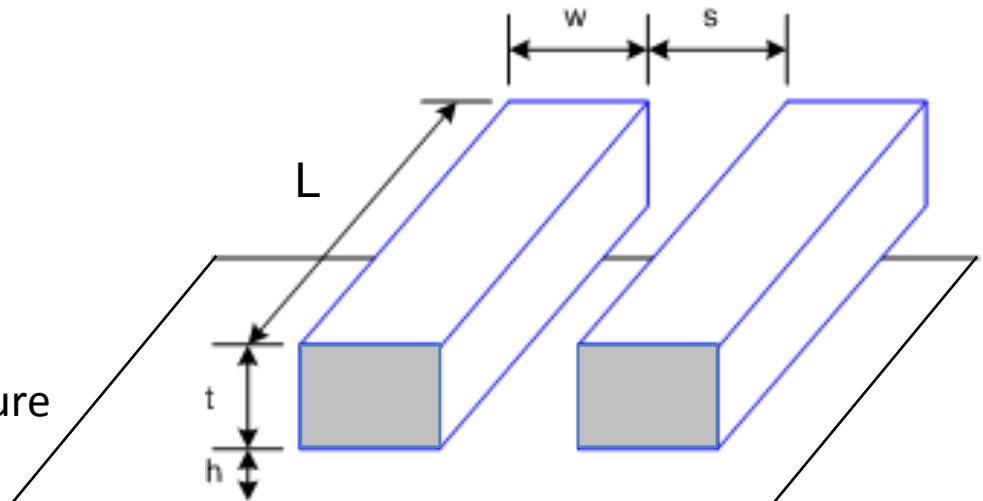

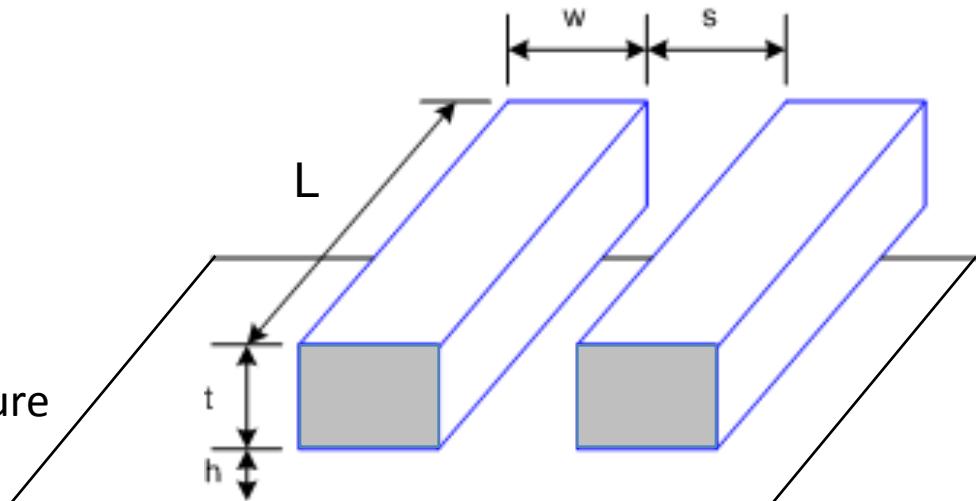

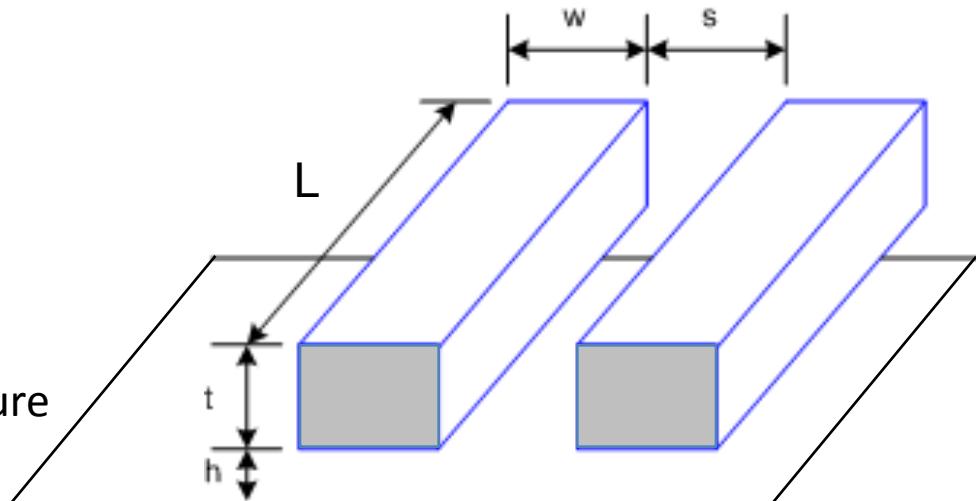

# Wire geometry

Today: pack in many skinny wires!

For long skinny wires resistance cannot be neglected since cross sectional area shrinks with feature size, wire length stays the same or increases.

Hence: wire resistances can no longer be neglected!

# Wire geometry

- Long skinny wires

- wire resistance cannot be neglected

- Wire length is increasing with large chips

- Wire cross sectional area shrinks with feature size

- Wires can no longer be modeled as capacitances alone

- We need improved wire models that consider wire resistance along with wire capacitance!

- Model must be distributed between at least two circuit nodes!

$$R = \rho \frac{L}{A} = rL$$

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

$$\text{Area} = w \times t \Rightarrow R = \rho \frac{L}{w \times t}$$

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

$$\text{Area} = w \times t \Rightarrow R = \rho \frac{L}{w \times t}$$

All wires in certain layer has the same thickness,  $t$ , hence sheet resistivity is a convenient measure

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

$$\text{Area} = w \times t \Rightarrow R = \rho \frac{L}{w \times t}$$

All wires in certain layer has the same thickness,  $t$ , hence sheet resistivity is a convenient measure

$$R_s = \frac{\rho}{t} \quad \text{in ohms per square, } \Omega/\square$$

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

$$\text{Area} = w \times t \Rightarrow R = \rho \frac{L}{w \times t}$$

All wires in certain layer has the same thickness,  $t$ , hence sheet resistivity is a convenient measure

$$R_s = \frac{\rho}{t} \quad \text{in ohms per square, } \Omega/\square$$

The "number of squares" in the direction of current flow is  $L/W$

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

$$\text{Area} = w \times t \Rightarrow R = \rho \frac{L}{w \times t}$$

All wires in certain layer has the same thickness,  $t$ , hence sheet resistivity is a convenient measure

$$R_s = \frac{\rho}{t} \quad \text{in ohms per square, } \Omega/\square$$

The "number of squares" in the direction of current flow is  $L/W$

# Wire resistance

$$R = \rho \frac{L}{A} = rL$$

$$\text{Area} = w \times t \Rightarrow R = \rho \frac{L}{w \times t}$$

All wires in certain layer has the same thickness,  $t$ , hence sheet resistivity is a convenient measure

$$R_s = \frac{\rho}{t} \quad \text{in ohms per square, } \Omega/\square$$

The "number of squares" in the direction of current flow is  $L/W$

If we assign a certain width,  $W_0$ , to all wires in certain layer they will all have the same resistance per unit length,  $r = R_s/W_0$

# Example

- Estimate the sheet resistance of a 220 nm thick copper wire if the resistivity of the thin copper film is  $22 \text{ n}\Omega\cdot\text{m}$ .

$$R_S =$$

# Example

- Estimate the sheet resistance of a 220 nm thick copper wire if the resistivity of the thin copper film is 22 nΩ·m.

$$R_s = \frac{\rho}{t} = \frac{22 \text{ n} \cdot \text{m}}{220 \text{ nm}} = 0.10 \text{ } \Omega/\square$$

# Example

- Estimate the sheet resistance of a 220 nm thick copper wire if the resistivity of the thin copper film is 22 nΩ·m.

$$R_s = \frac{\rho}{t} = \frac{22 \text{ n} \cdot \text{m}}{220 \text{ nm}} = 0.10 \text{ } \Omega/\square$$

- Find the total resistance if the wire is 0.125 μm wide and 1 mm long. (Ignore the barrier layer)

$$R =$$

# Example

- Estimate the sheet resistance of a 220 nm thick copper wire if the resistivity of the thin copper film is 22 nΩ·m.

$$R_s = \frac{\rho}{t} = \frac{22 \text{ n} \cdot \text{m}}{220 \text{ nm}} = 0.10 \text{ } \Omega/\square$$

- Find the total resistance if the wire is 0.125 μm wide and 1 mm long. (Ignore the barrier layer)

$$R = \underbrace{0.10 \text{ } \Omega}_{R_s} \times \underbrace{\frac{1000 \text{ } \mu\text{m}}{0.125 \text{ } \mu\text{m}}}_{L/W=8000 \text{ "squares"}} = \text{ } \Omega$$

# Example

- Estimate the sheet resistance of a 220 nm thick copper wire if the resistivity of the thin copper film is 22 nΩ·m.

$$R_s = \frac{\rho}{t} = \frac{22 \text{ n} \cdot \text{m}}{220 \text{ nm}} = 0.10 \text{ } \Omega/\square$$

- Find the total resistance if the wire is 0.125 μm wide and 1 mm long. (Ignore the barrier layer)

$$R = \underbrace{0.10 \text{ } \Omega}_{R_s} \times \underbrace{\frac{1000 \text{ } \mu\text{m}}{0.125 \text{ } \mu\text{m}}}_{L/W=8000 \text{ "squares"}} = \text{ } \Omega$$

- Wires 125 nm wide have a resistivity per unit length of 800 Ω/mm

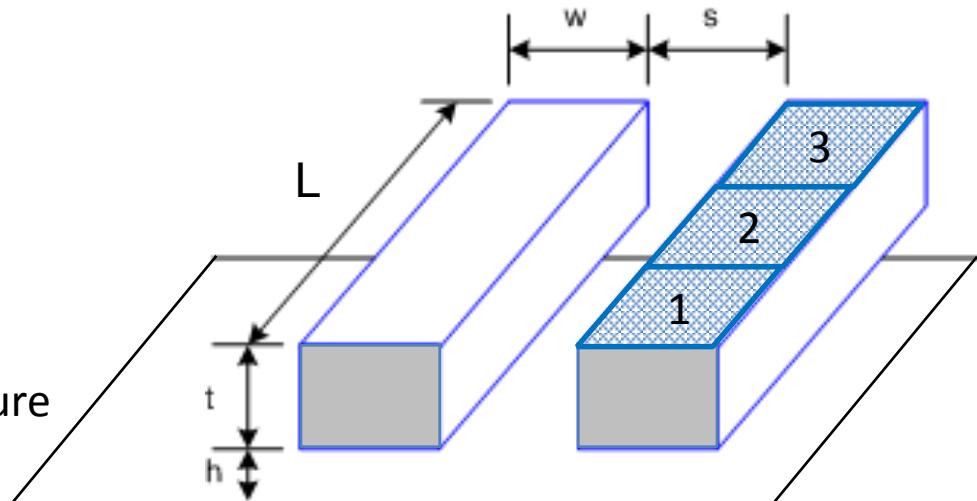

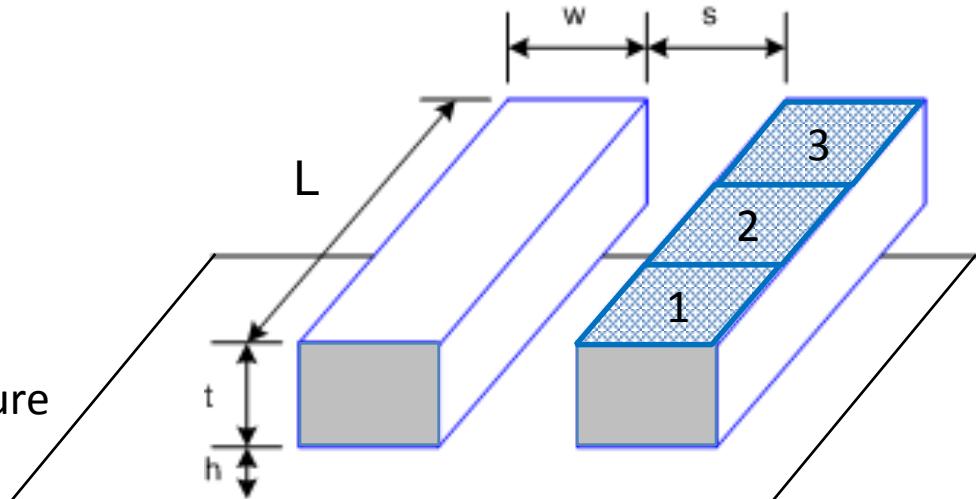

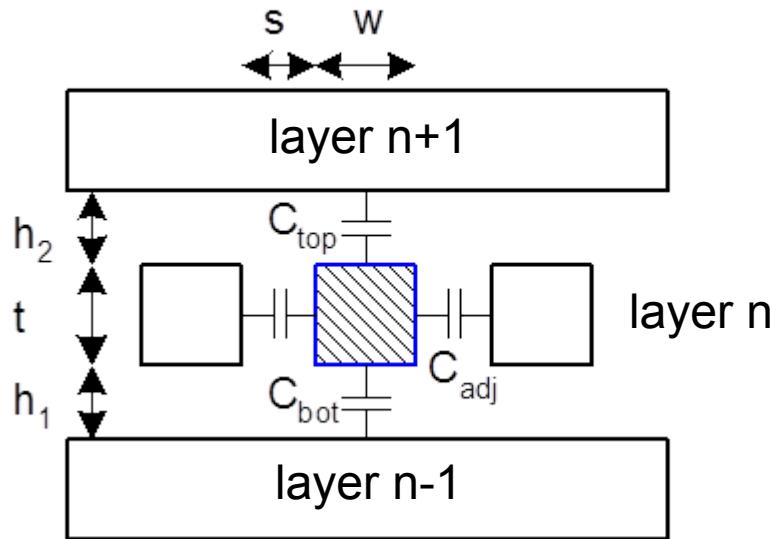

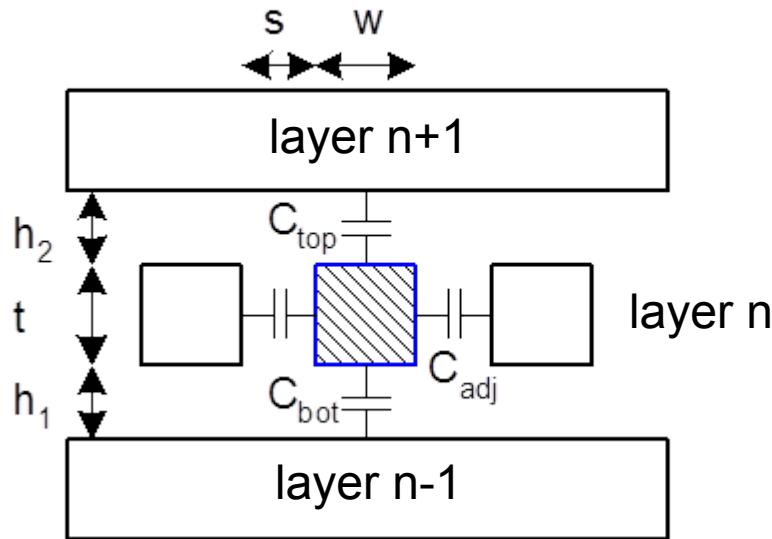

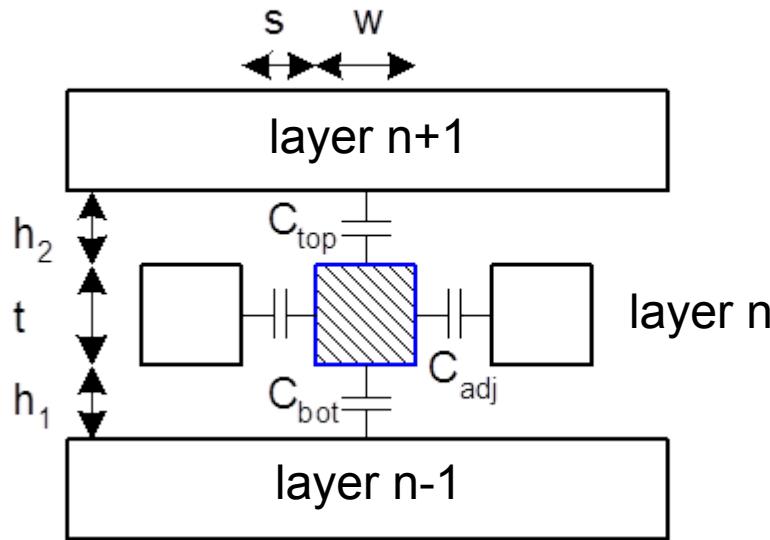

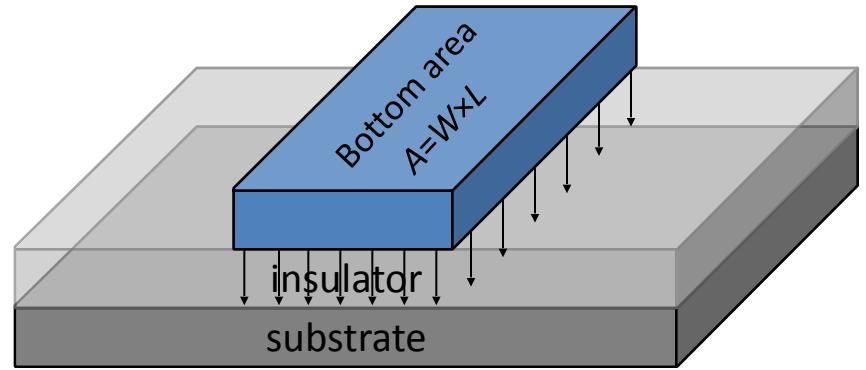

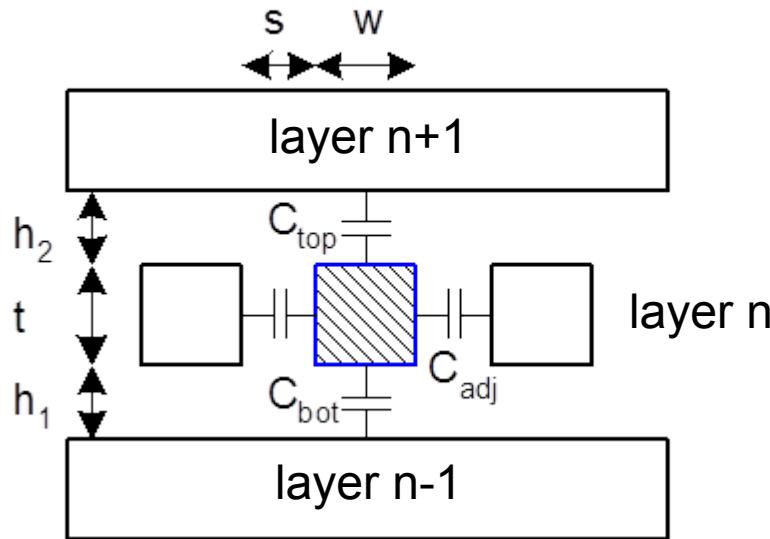

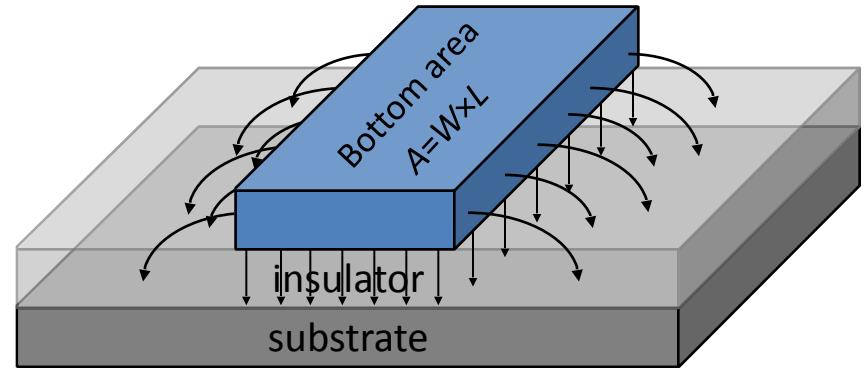

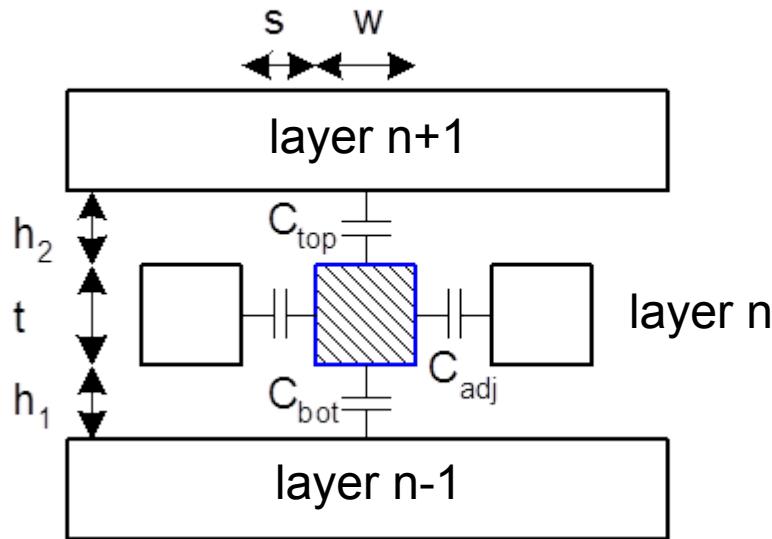

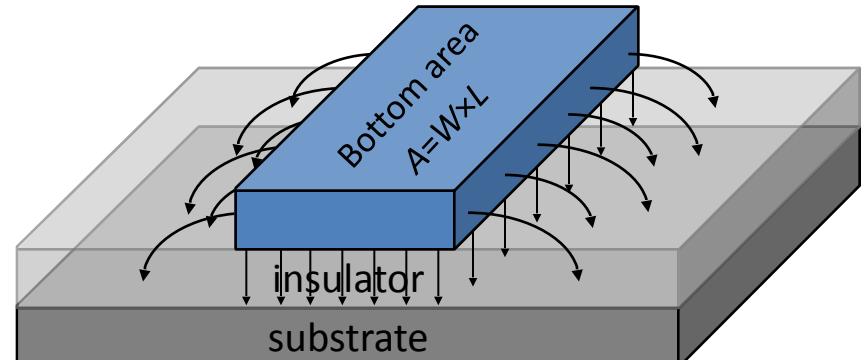

# Wire capacitance

Wires have a capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

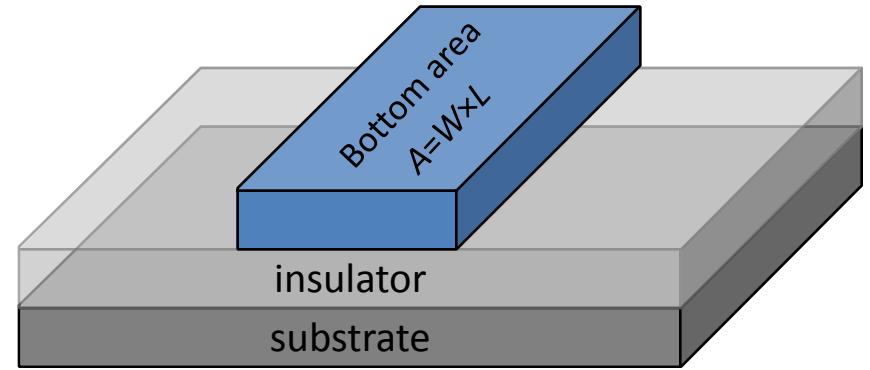

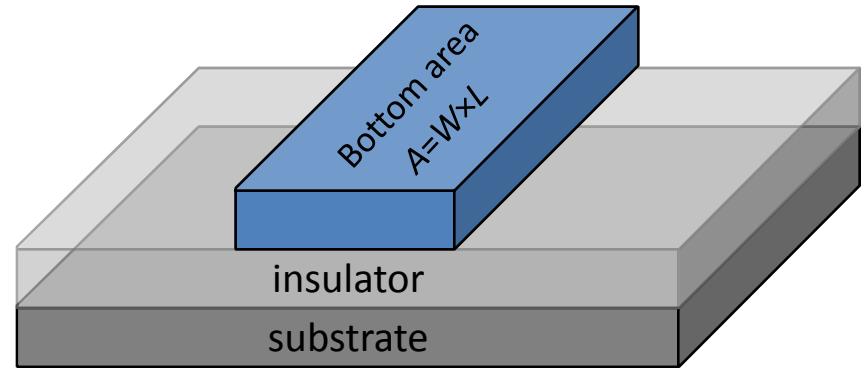

# Wire capacitance

Wires have a capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

Parallel-plate capacitance equation

- $C_{pp} = \epsilon A/h$ , where top/bottom area  $A=W\times L$

- $\epsilon = \kappa \epsilon_0$ ,  $\epsilon_0 = 8.85 \cdot 10^{-12} \text{ F/m}$  in vacuum

- $\text{SiO}_2$  permittivity is  $\kappa \approx 4$

- low-kappa materials have  $\kappa < 3$

# Wire capacitance

Parallel plate capacitance

Wires have a capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

Parallel-plate capacitance equation

- $C_{pp} = \epsilon A/h$ , where top/bottom area  $A=W \times L$

- $\epsilon = \kappa \epsilon_0$ ,  $\epsilon_0 = 8.85 \cdot 10^{-12} \text{ F/m}$  in vacuum

- $\text{SiO}_2$  permittivity is  $\kappa \approx 4$

- low-kappa materials have  $\kappa < 3$

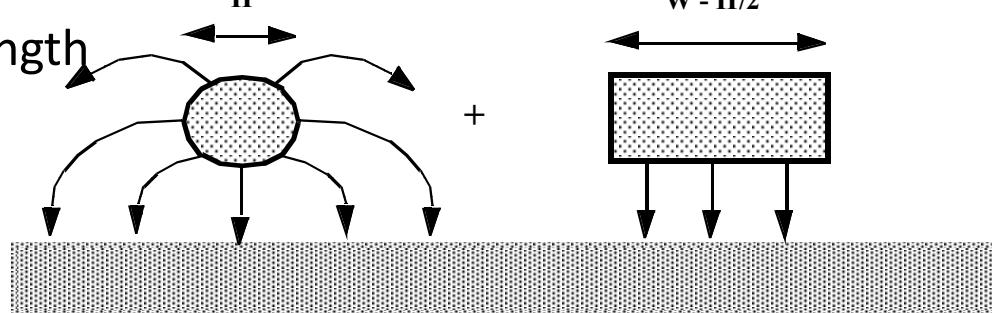

# Wire capacitance

Parallel plate capacitance

and fringing-field capacitance

Wires have a capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

Parallel-plate capacitance equation

- $C_{pp} = \epsilon A/h$ , where top/bottom area  $A=W \times L$

- $\epsilon = \kappa \epsilon_0$ ,  $\epsilon_0 = 8.85 \cdot 10^{-12} \text{ F/m}$  in vacuum

- $\text{SiO}_2$  permittivity is  $\kappa \approx 4$

- low-kappa materials have  $\kappa < 3$

# Wire capacitance

Wires have a capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

Parallel-plate capacitance equation

- $C_{pp} = \epsilon A/h$ , where top/bottom area  $A=W \times L$

- $\epsilon = \kappa \epsilon_0$ ,  $\epsilon_0 = 8.85 \cdot 10^{-12} \text{ F/m}$  in vacuum

- $\text{SiO}_2$  permittivity is  $\kappa \approx 4$

- low-kappa materials have  $\kappa < 3$

Parallel plate capacitance

and fringing-field capacitance

$$c_{wire} = c_{pp} + c_{fringe} = \frac{w \epsilon_{di}}{t_{di}} + \frac{2\pi \epsilon_{di}}{\log(t_{di}/H)}$$

Note: Cap is per unit length

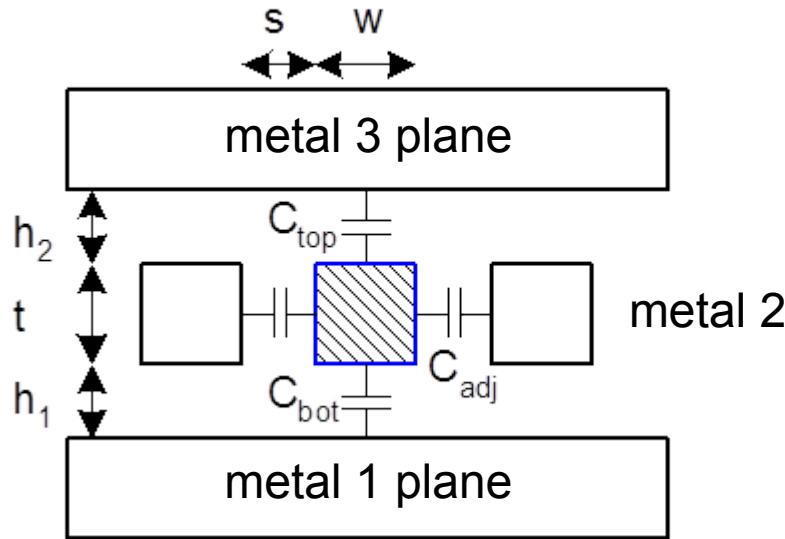

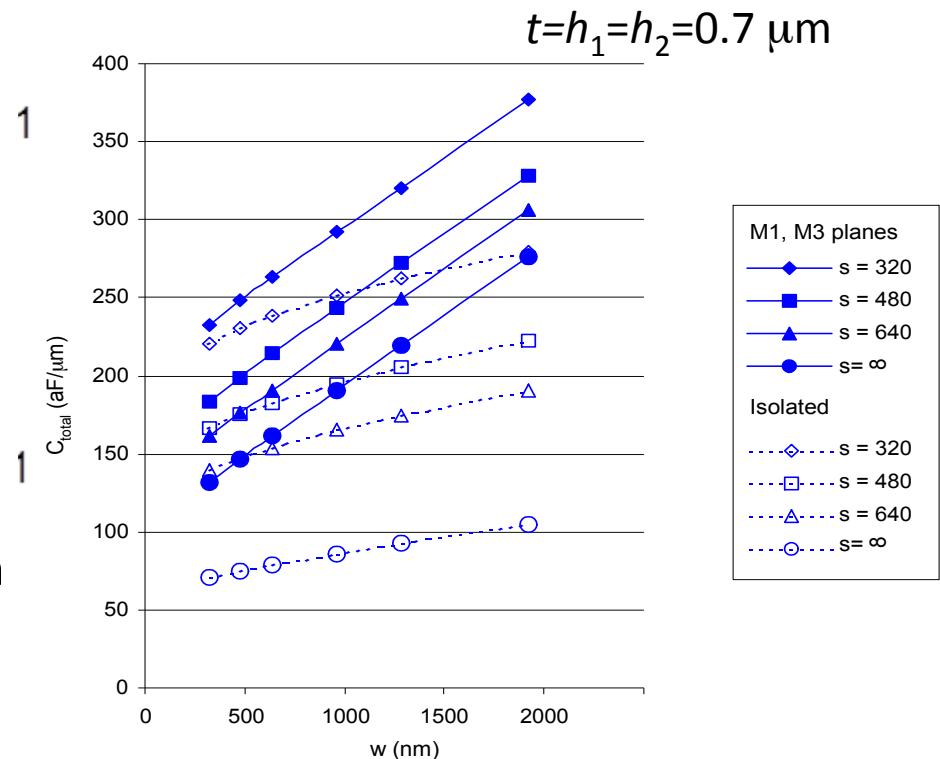

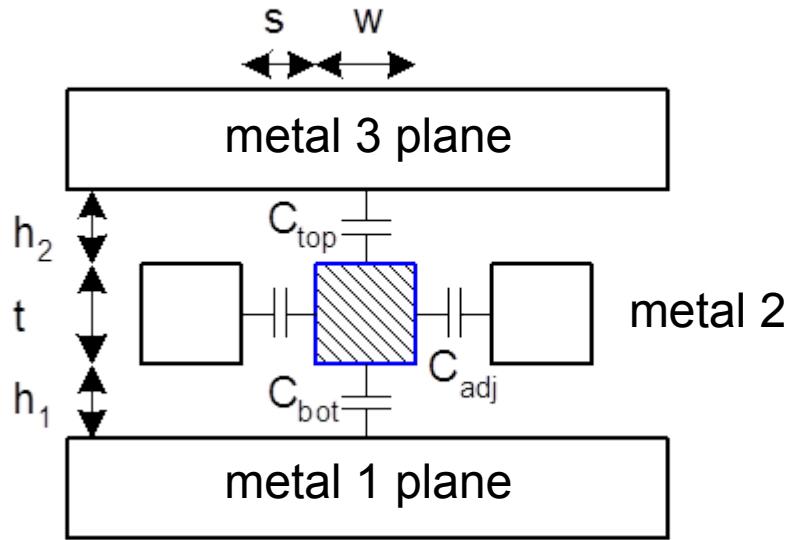

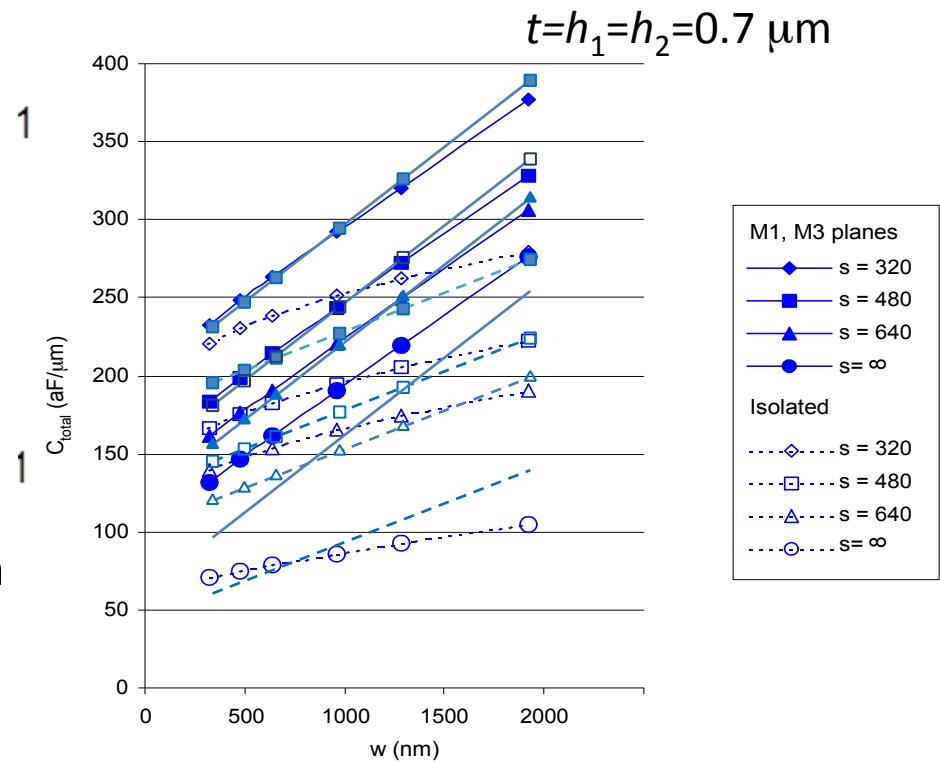

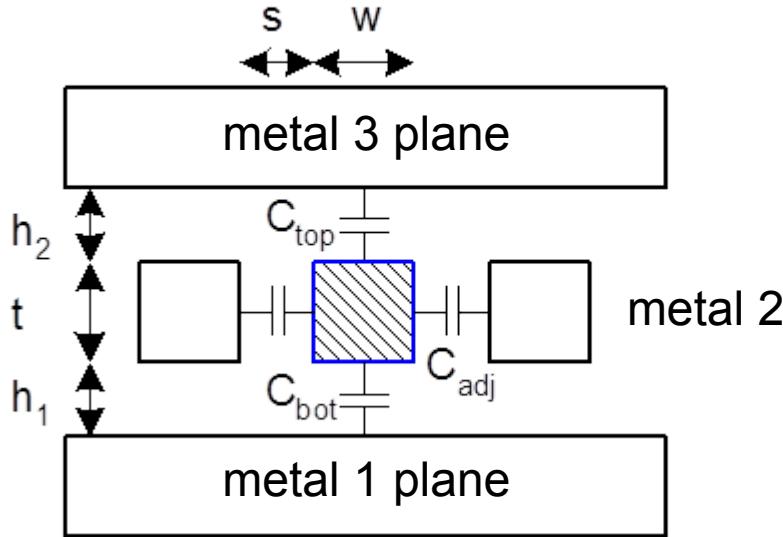

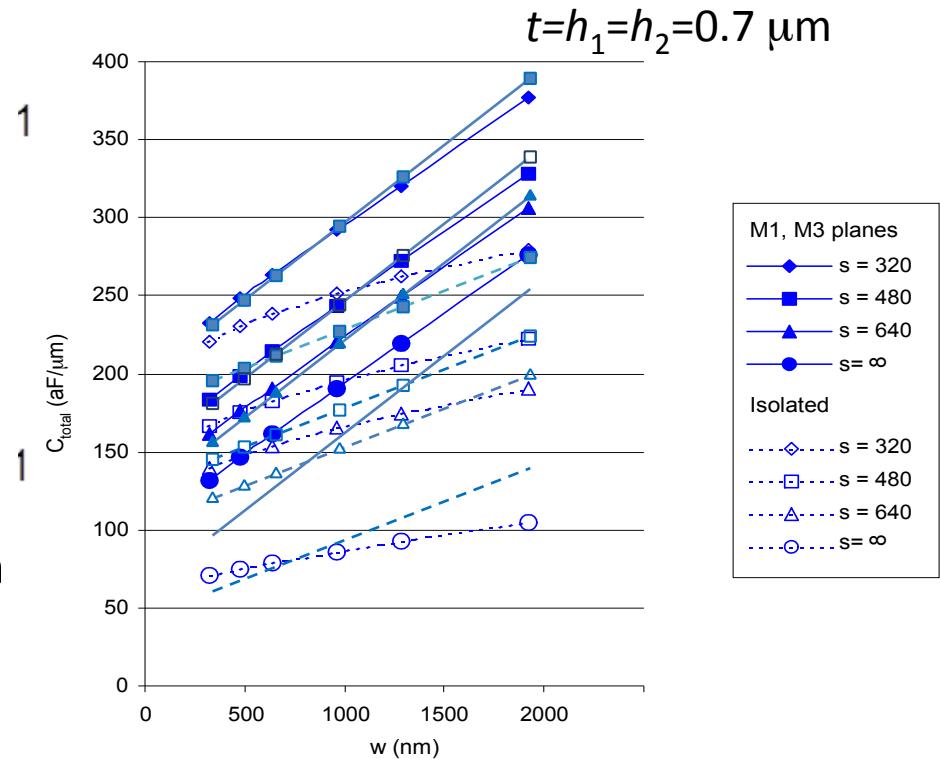

# Metal2 Capacitance Data

Wire has capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

# Metal2 Capacitance Data

Wire has capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

# Metal2 Capacitance Data

Wire has capacitance  $c$  per unit length

- to neighbors in the same layer

- to layers above and below

- Wires typically have capacitances about  $\sim 0.2 \text{ fF}/\mu\text{m}$ , i. e.  $200 \text{ fF}/\text{mm}$

- Compare with the  $1.2 \text{ fF}/\mu\text{m}$  for the MOSFET gate capacitances

# Wire RC delay

- Wire RC product increases as  $L^2$  with wire length  $L$

- For our 1 mm example wire, the  $RC$  product was 160 ps

- $r$  is wire resistance per unit length  $\sim 800 \Omega/\text{mm}$  ( $0.8 \text{ k}\Omega/\text{mm}$ )

- $c$  is wire capacitance per unit length  $\sim 200 \text{ fF/mm}$

- In comparison, the  $RC$  time constant of an inverter with a FO4 was previously found to be 36 ps ( $5 \times 7.2 \text{ ps}$ )

- FO4 delay =  $0.7 \times 36 = 25 \text{ ps}$

$$RC = rcl^2$$

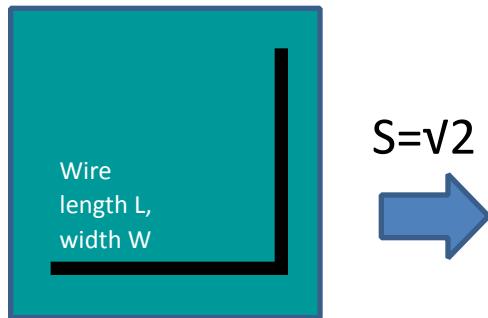

# Modern interconnect

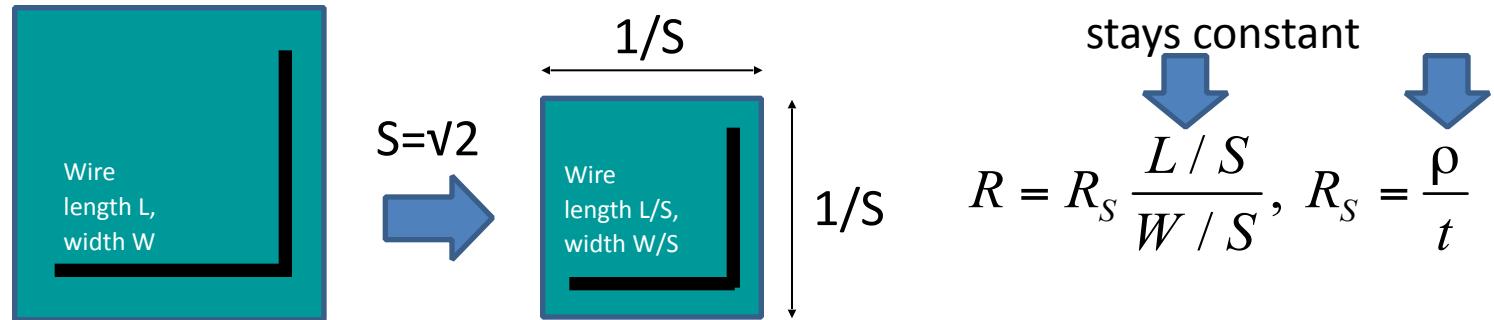

# Wire delay scaling – Local wires

- For local wires crossing the same amount of circuitry

- Resistance stays roughly constant

- Aspect ratio does not change

- Sheet resistivity does not change if wire height stays large and/or change material to copper

- Capacitance decreases by scaling factor

- Cap/unit length stays constant, while length decreases

- Hence, wire delay tracks gate delay  $\sim 1/S$

From Mark Horowitz at Design Automation Conference 2000

# Wire delay scaling – Global wires

$S = \sqrt{2}$

stays constant

$$R = R_S \frac{L}{W / S} \sim S$$

- For global wires crossing the whole chip

- Resistance grows linearly (with scaling factor)

- Capacitance stays fixed

- Cap/unit length stays constant, as does wire length

- Two opposite trends:

- Wire delay increases ( $\sim S$ ) - gate delay decreases ( $\sim 1/S$ )

stays constant

$$C = (WC_{ox})L$$

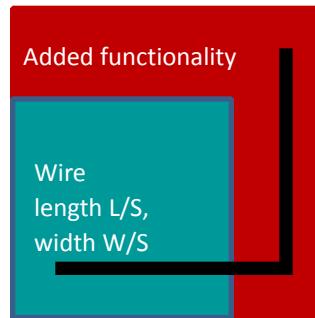

# Modern Interconnect

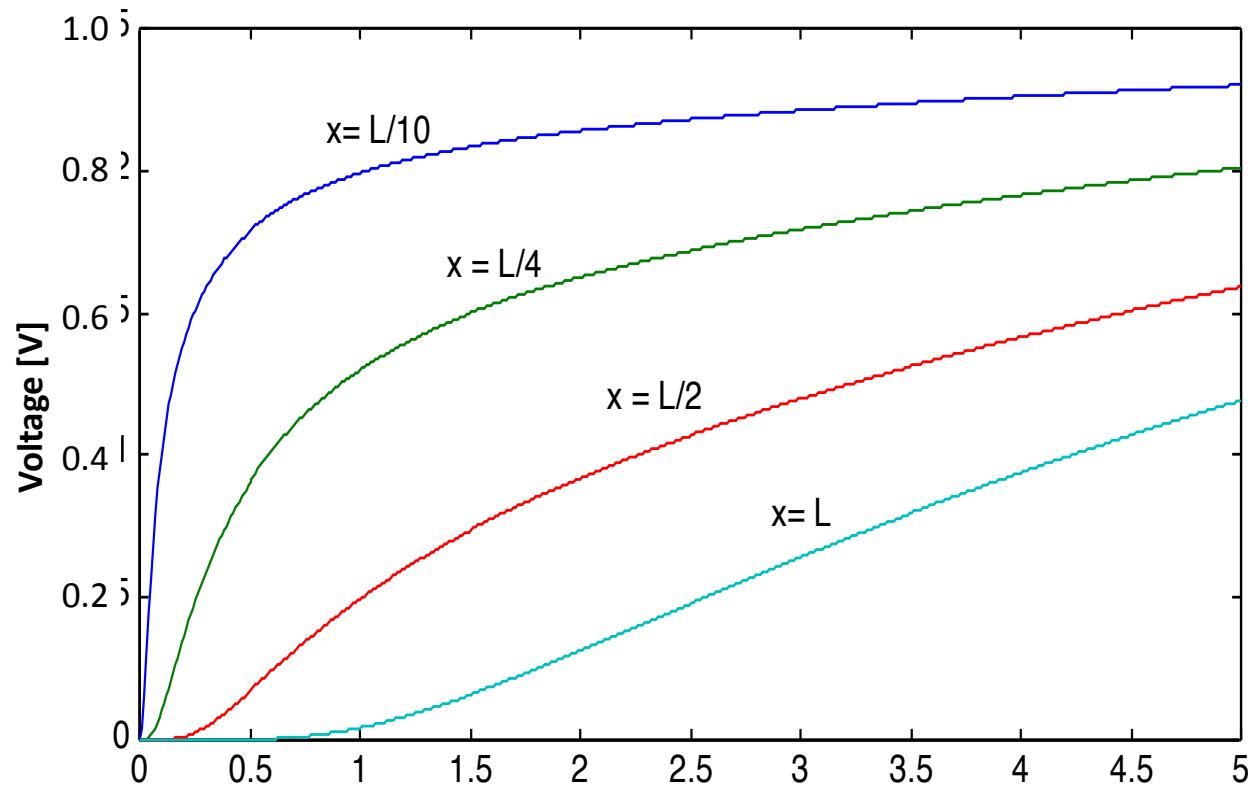

# Step-response to a rising input voltage along an RC wire as a function of time and wire length

# Summary

We have

- discussed the importance of accurate wire modeling considering not only wire capacitance but also wire resistance as wires get longer and skinnier

- defined the concept of sheet resistance in ohms per square

- had a look at typical on-chip wire length distributions

- had a look at wire capacitance dependence on the surrounding wiring on top, below, and along sidewalls

# Introduction to on-chip interconnect

Wire delay modeling and repeater insertion

Lecture 7 continued

Tuesday October 2, 2018

# Outline

- Introduction

- Introduce a distributed RC  $\pi$ -model for delay estimates

- Wire resistance per unit length  $L, r$

- Wire capacitance per unit length  $L, c$

- Distributed wire delay  $\sim \frac{1}{2}rcL^2$

- For simplicity, assume the existence of a dominant RC time constant for describing the output signal at the wire end

- We will show how repeaters can be inserted to keep wire lengths short

- Find the optimal number of repeaters for any wire length

- Find the critical wire length for repeater insertion

- Introduce the concept of wire effort

- Conclusions

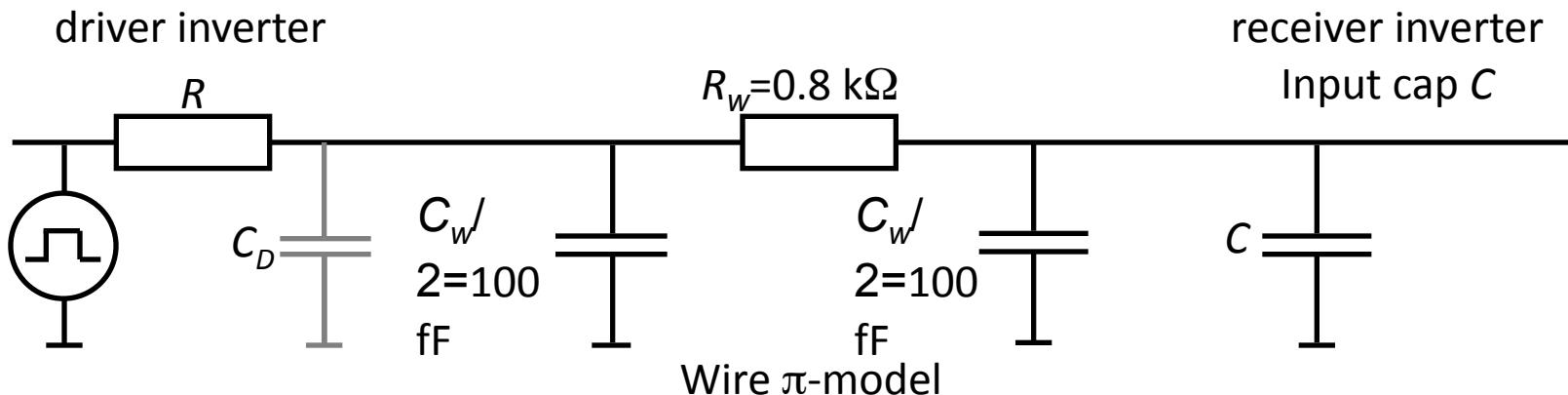

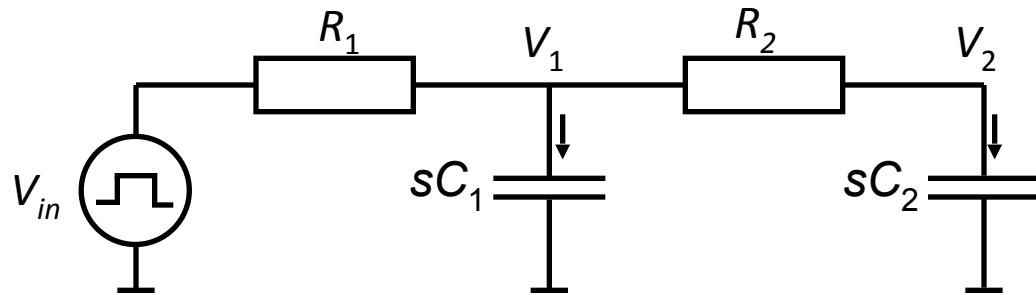

# Wire delay example

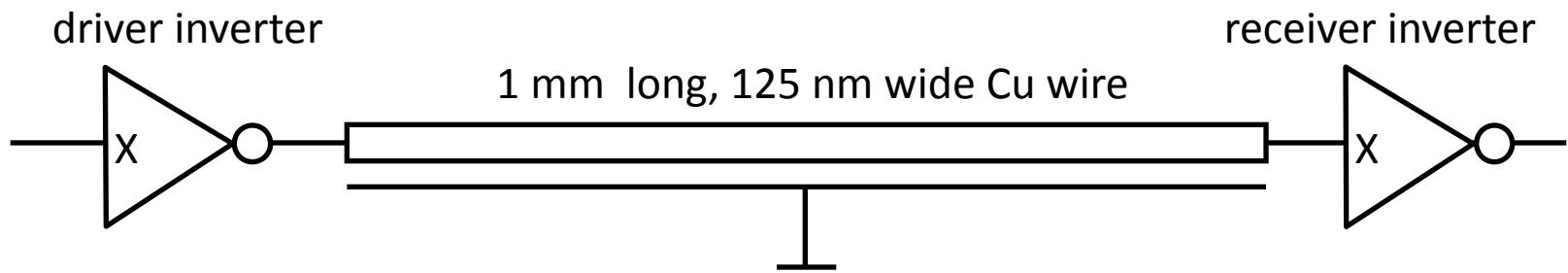

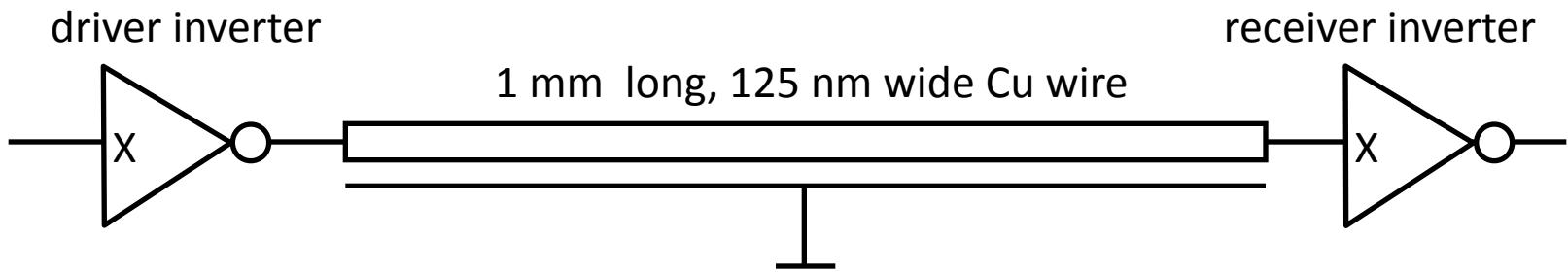

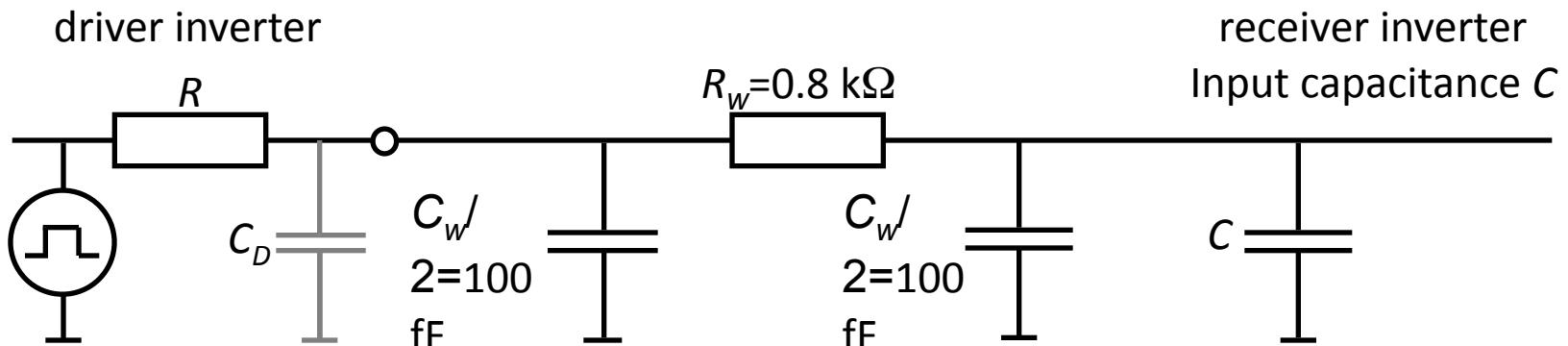

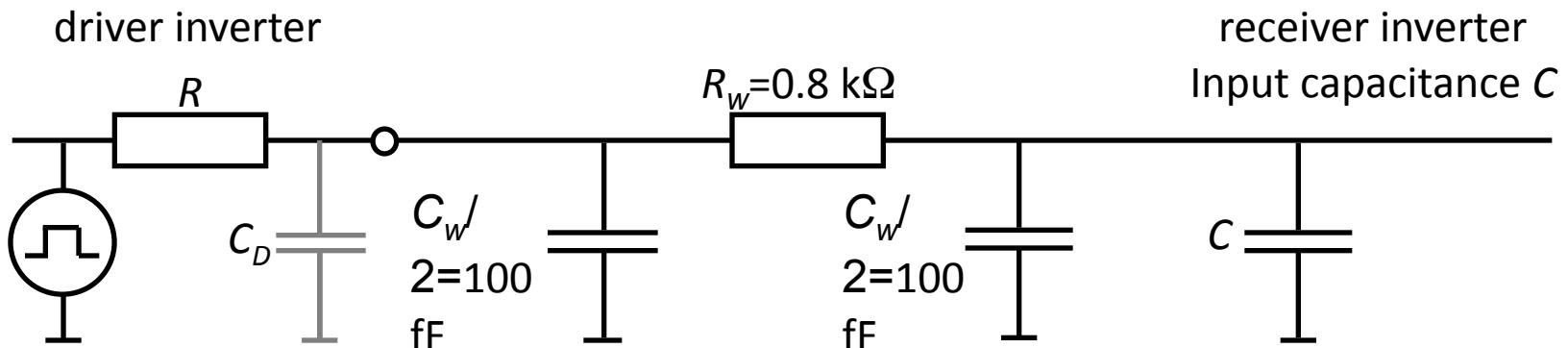

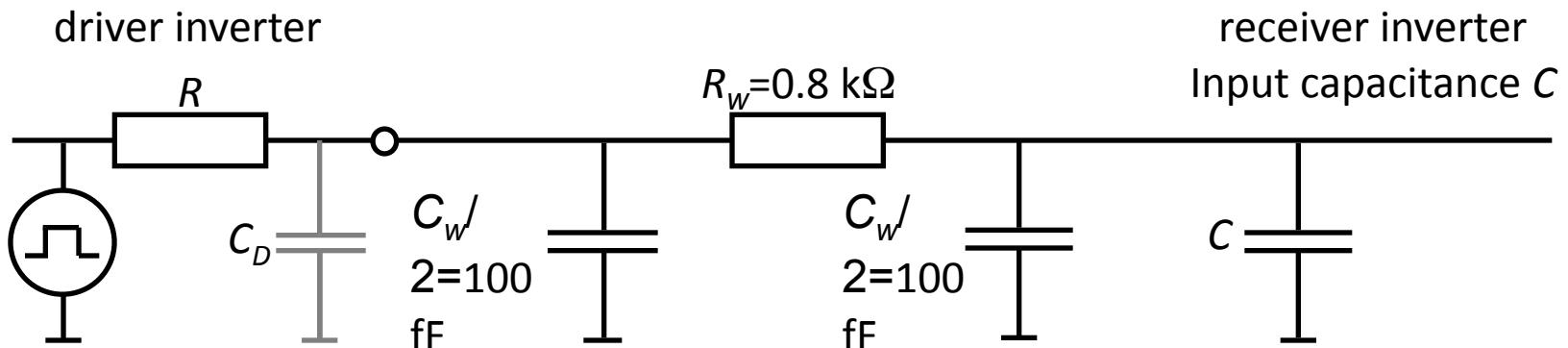

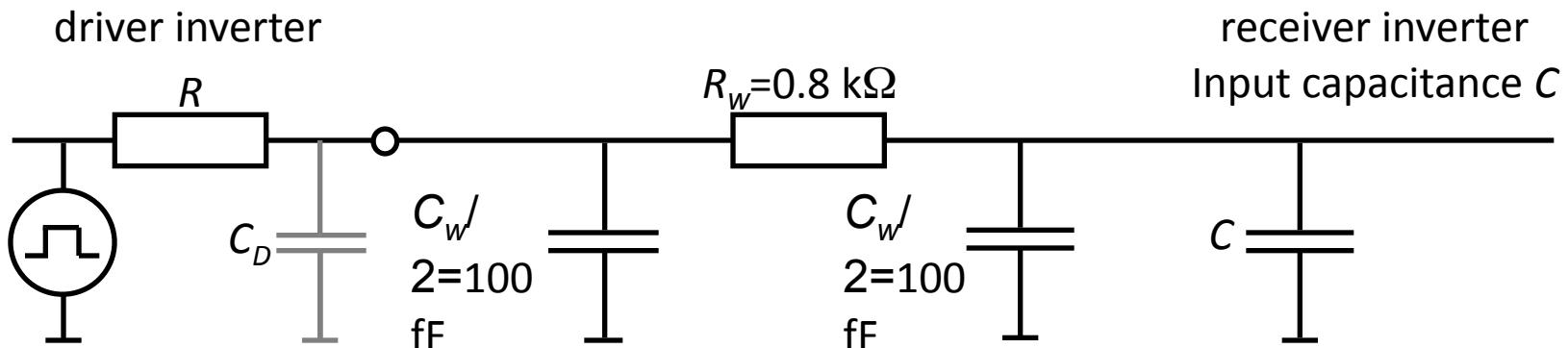

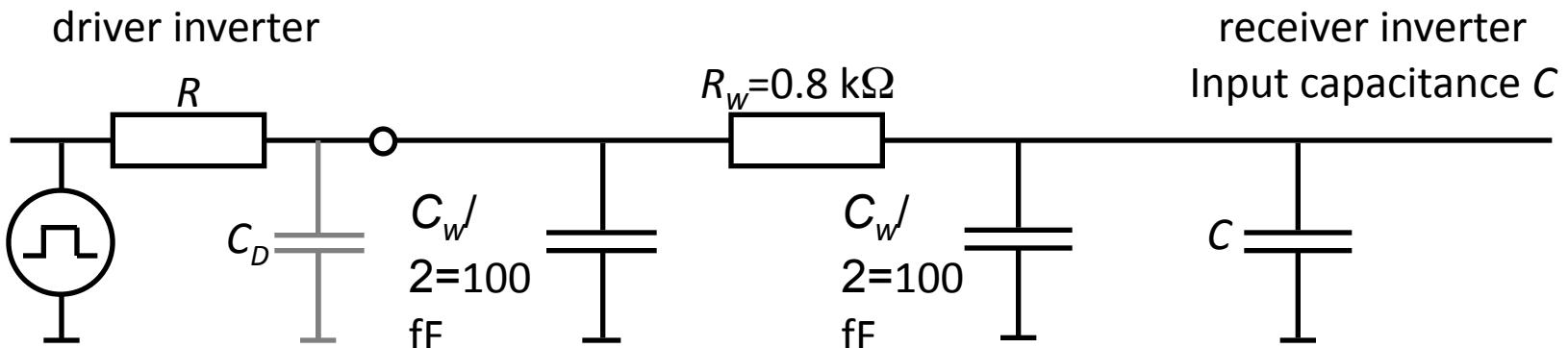

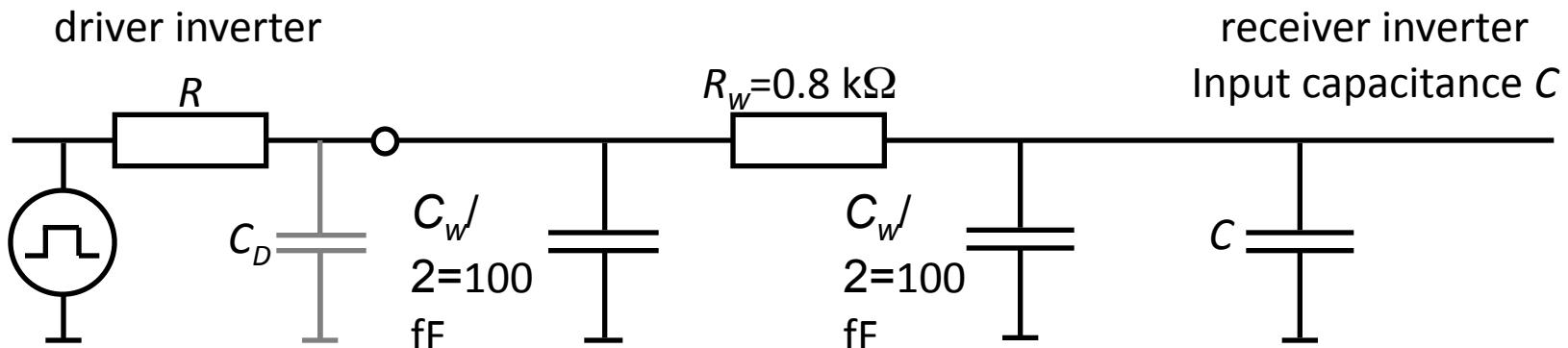

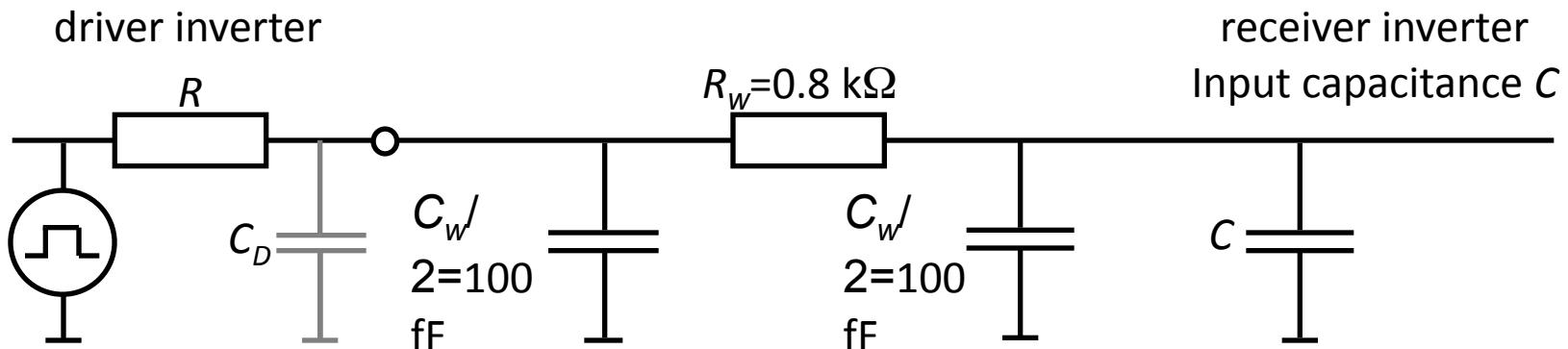

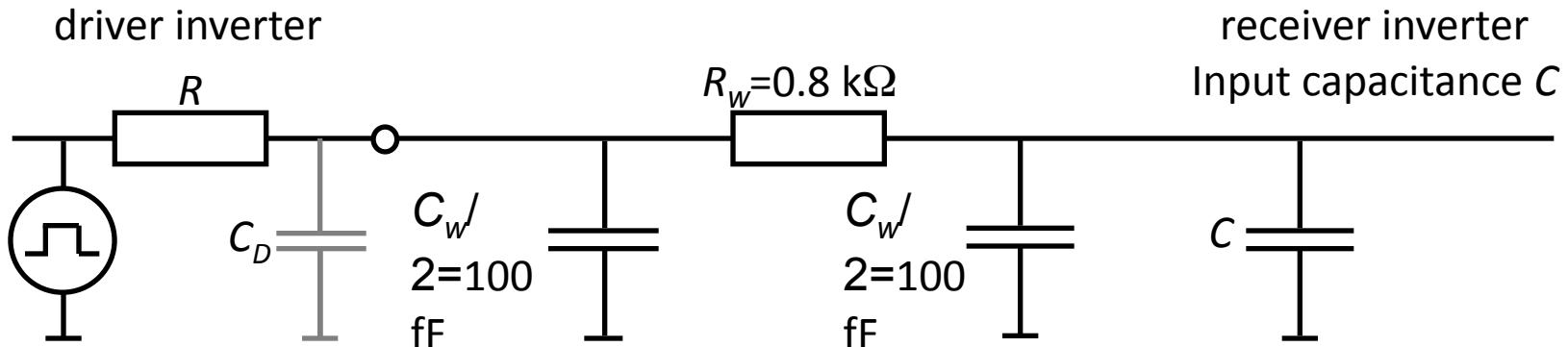

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

---

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

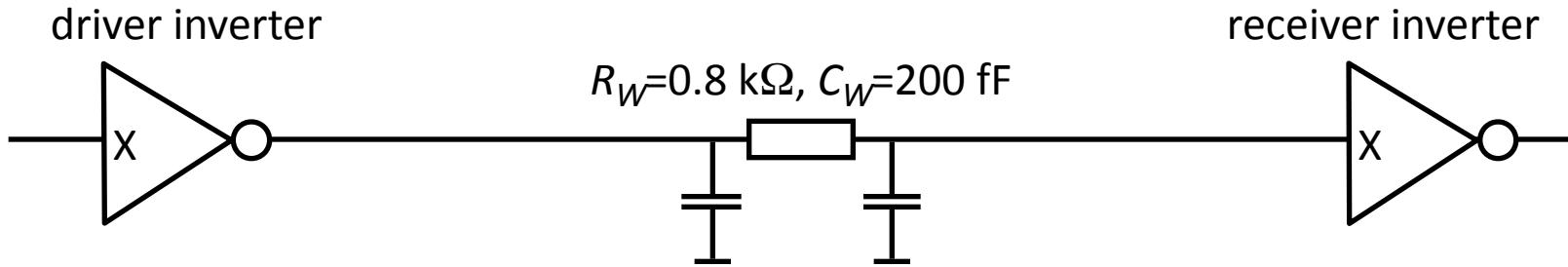

The given parameters yield a wire resistance of  $800 \Omega$  and a wire cap is  $200 \text{ fF}$ .

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Hence, wire  $R_W C_W$  product is 160 ps

The contribution to the system time constant from the distributed wire is  $\frac{1}{2} R_W C_W = 80 \text{ ps}$

Increasing the time constant from the 14.4 ps with no or a short wire to almost 95 ps.

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

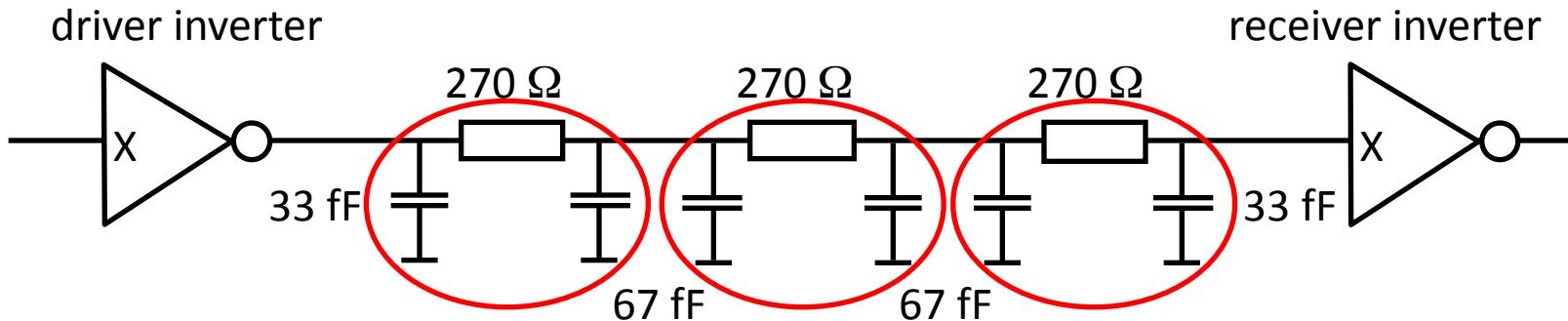

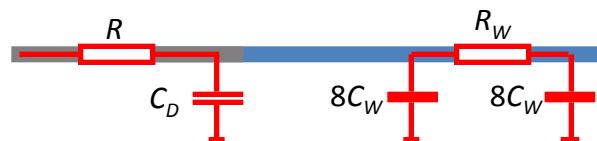

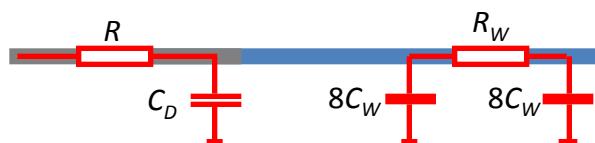

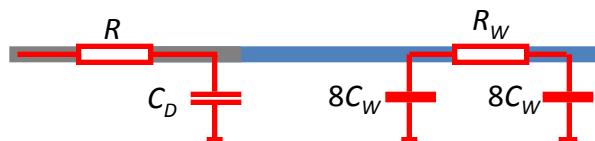

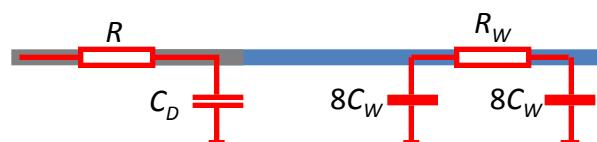

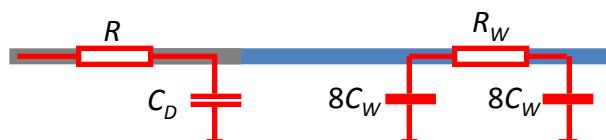

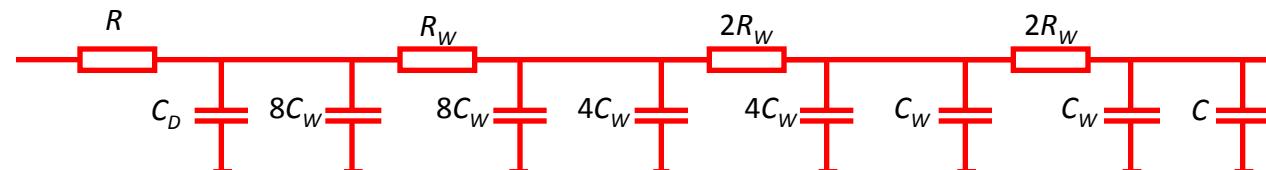

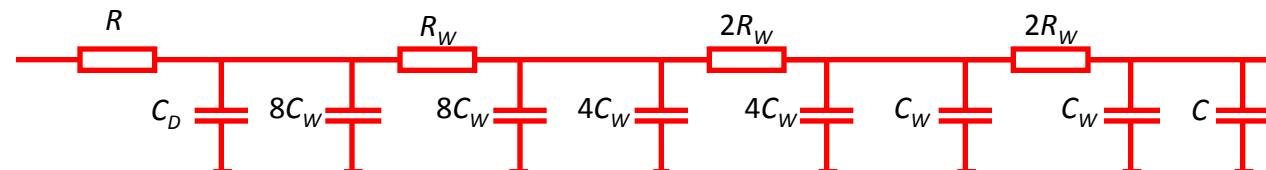

Wire resistance is distributed along the wire which must be modeled by segments

In Spice circuit simulations a 3-segment  $\pi$ -model is accurate to within 3%

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Wire resistance is distributed along the wire which must be modeled by segments

In Spice circuit simulations a 3-segment  $\pi$ -model is accurate to within 3%

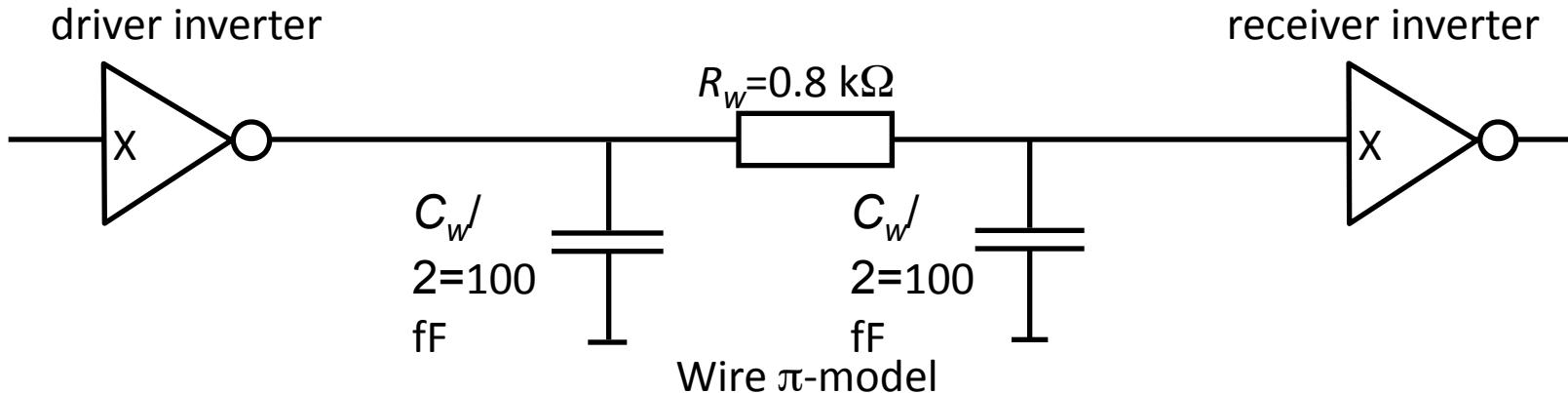

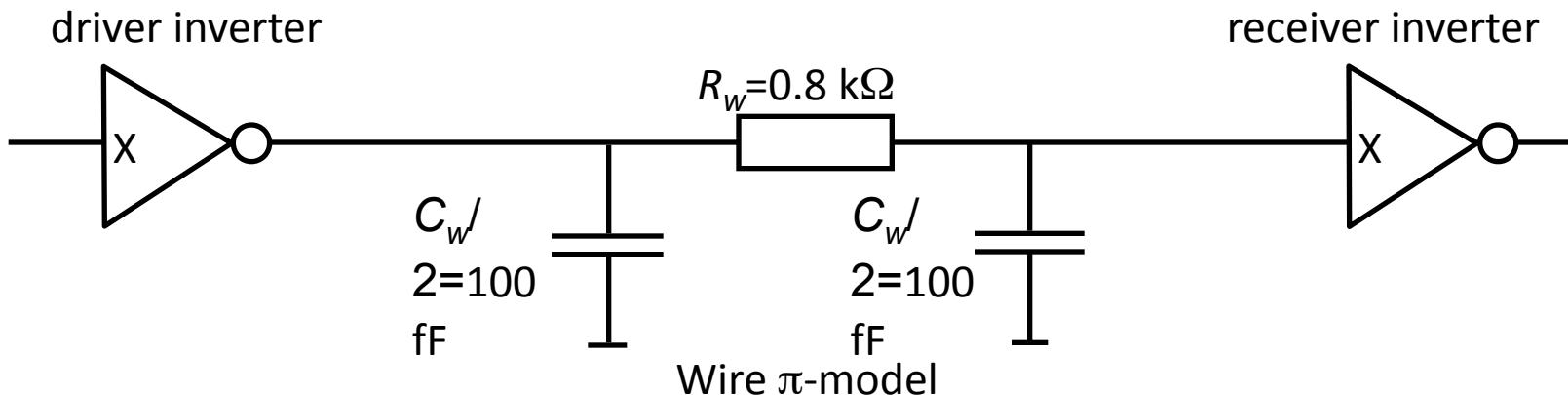

However, for simple analytical estimate: use single segment  $\pi$ -model.

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

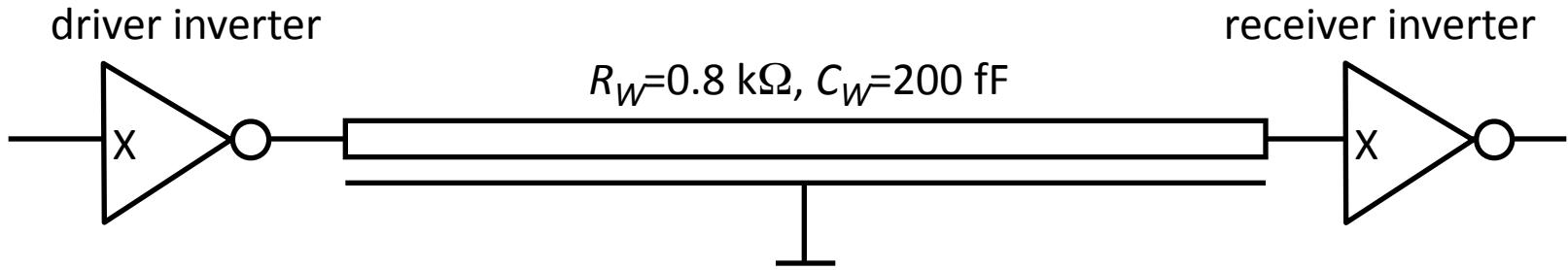

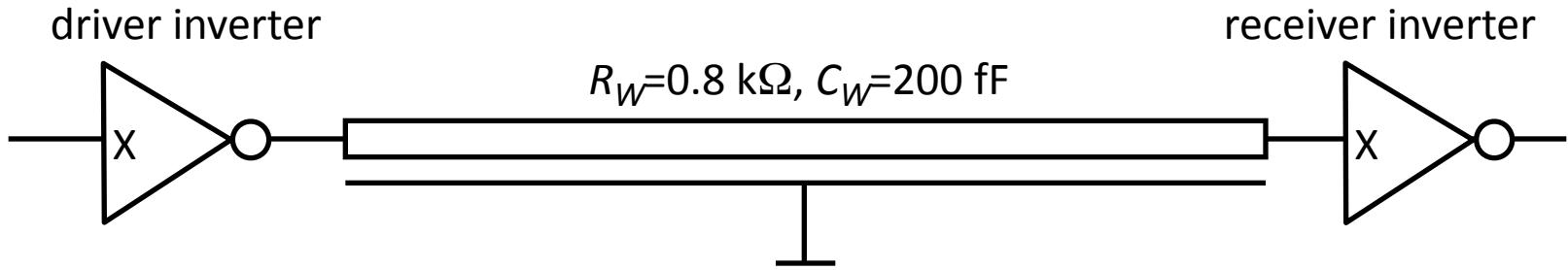

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_W C_W$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

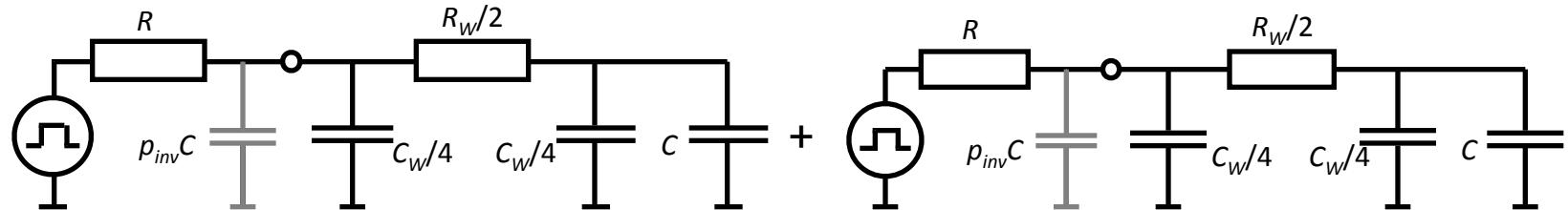

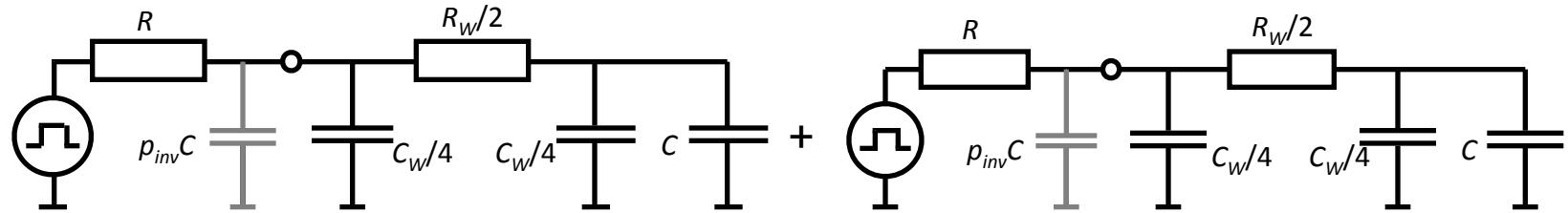

Introduce electrical inverter models

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_w C_w$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Introduce electrical inverter models

# Wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c=200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if the wire  $R_w C_w$  product is larger than the reference  $RC$  product of the inverter  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Introduce electrical inverter models

What is the delay of this two-stage RC circuit?

Can be found analytically from second-order differential equation!

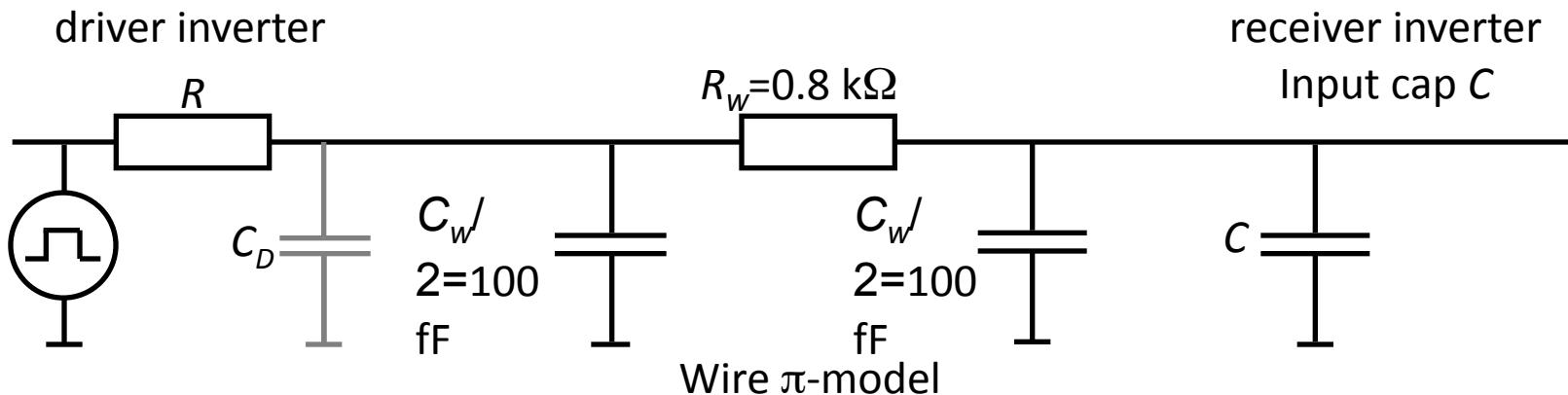

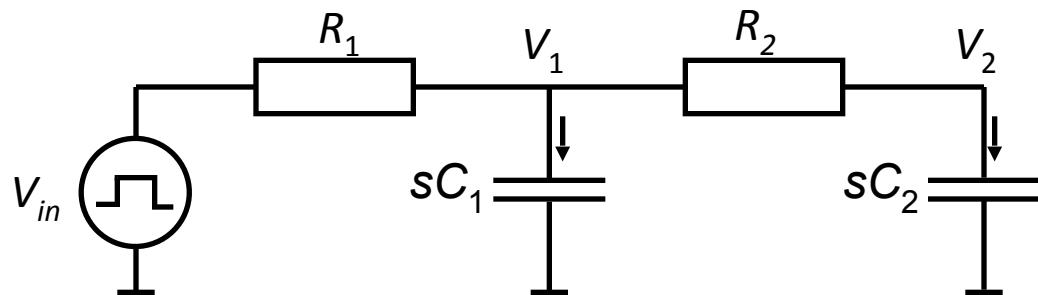

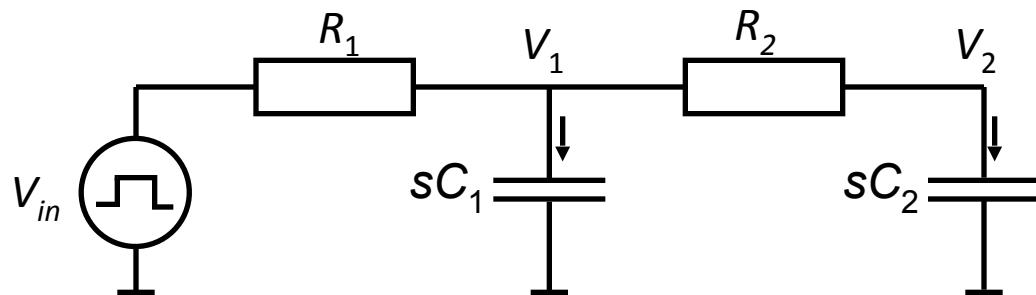

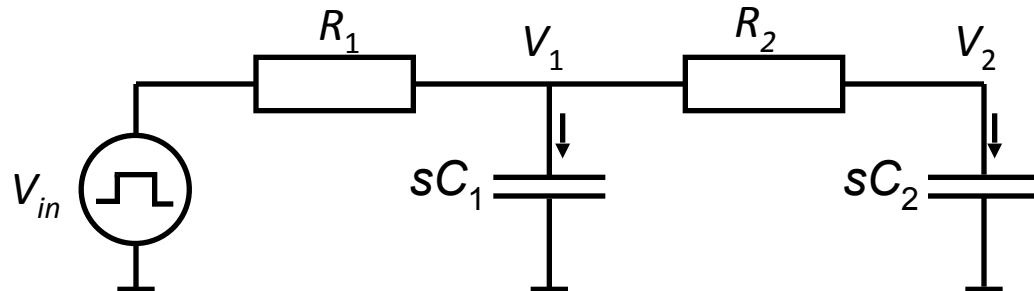

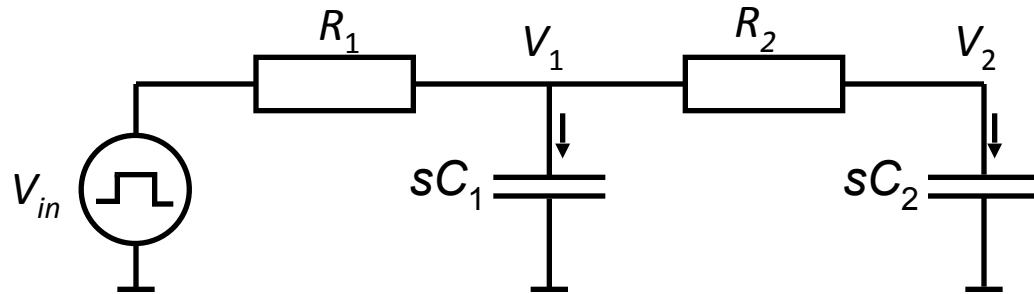

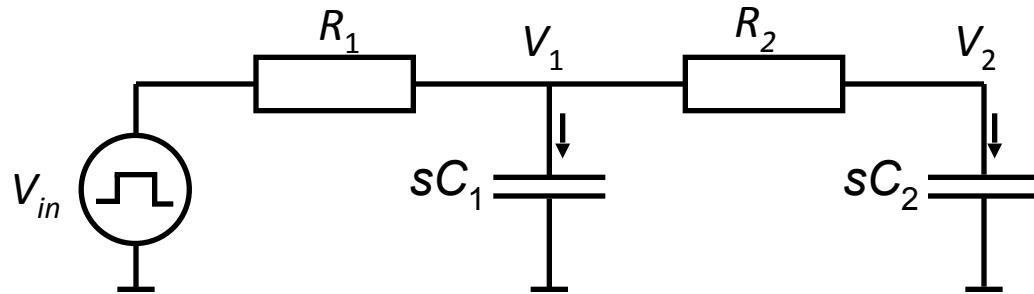

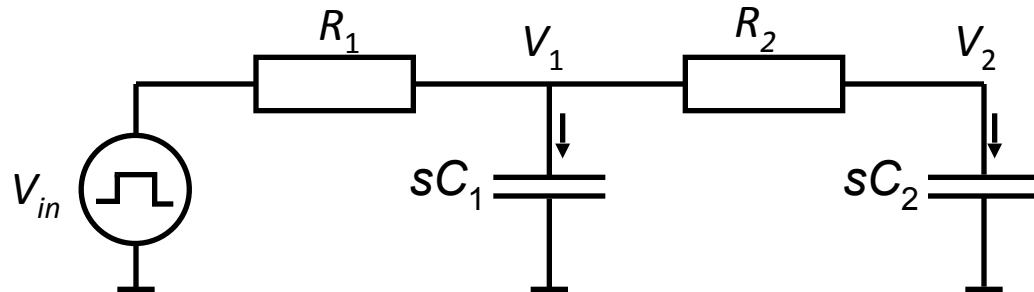

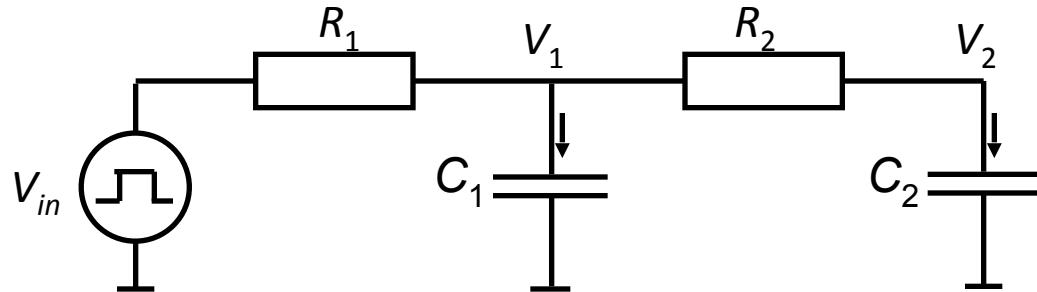

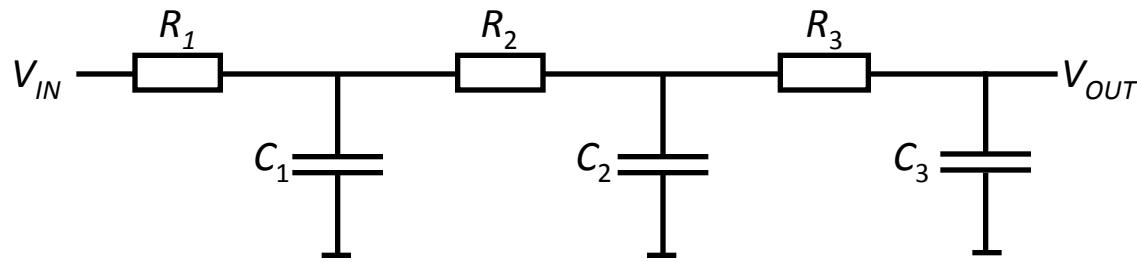

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

---

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2) s + 1}$$

Second order linear differential equation

$$R_1 R_2 C_1 C_2 V_2^{(2)} + (R_1 (C_1 + C_2) + R_2 C_2) V_2' + V_2 = 0$$

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1(C_1 + C_2) + R_2 C_2)s + 1}$$

Characteristic eq. yields exponential time constants

$$R_1 R_2 C_1 C_2 s^2 + (R_1(C_1 + C_2) + R_2 C_2)s + 1 = 0$$

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

Let's denote the two solutions to the characteristic equation  $s_1$  and  $s_2$ , respectively.

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2)s + 1}$$

Characteristic eq. yields exponential time constants

$$R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2)s + 1 = 0$$

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1(C_1 + C_2) + R_2 C_2)s + 1}$$

Characteristic eq. yields exponential time constants

$$R_1 R_2 C_1 C_2 s^2 + (R_1(C_1 + C_2) + R_2 C_2)s + 1 = 0$$

Let's denote the two solutions to the characteristic equation  $s_1$  and  $s_2$ , respectively. For the case of a falling output the solution is:

$$V_2(t) = V_{21} e^{s_1 t} + V_{22} e^{s_2 t}$$

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2)s + 1}$$

Characteristic eq. yields exponential time constants

$$R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2)s + 1 = 0$$

Let's denote the two solutions to the characteristic equation  $s_1$  and  $s_2$ , respectively. For the case of a falling output the solution is:

$$V_2(t) = V_{21} e^{s_1 t} + V_{22} e^{s_2 t}$$

Characteristic eq. also yields sum of the two time constants

$$\tau_E = \underbrace{(-\frac{1}{s_1})}_{\tau_1} + \underbrace{(-\frac{1}{s_2})}_{\tau_2} = R_1 (C_1 + C_2) + R_2 C_2$$

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2) s + 1}$$

Most often one time constant is dominant, for the case of a falling output voltage resulting in

$$V_2(t) \approx V_{DD} \cdot e^{-t/\tau_E}$$

Let's denote the two solutions to the characteristic equation  $s_1$  and  $s_2$ , respectively.

For the case of a falling output the solution is:

$$V_2(t) = V_{21} e^{s_1 t} + V_{22} e^{s_2 t}$$

Characteristic eq. also yields sum of the two time constants

$$\tau_E = \underbrace{(-\frac{1}{s_1})}_{\tau_1} + \underbrace{(-\frac{1}{s_2})}_{\tau_2} = R_1 (C_1 + C_2) + R_2 C_2$$

# Simplify wire circuit to find solution

Redraw the wire circuit as a two-stage RC circuit, where

Stage 1: resistance  $R_1$  and capacitance  $C_1$

Stage 2: resistance  $R_2$  and capacitance  $C_2$

- Get transfer function, or 2<sup>nd</sup> order linear differential equation

$$H(s) = \frac{1}{R_1 R_2 C_1 C_2 s^2 + (R_1 (C_1 + C_2) + R_2 C_2) s + 1}$$

Most often one time constant is dominant, for the case of a falling output voltage resulting in  $V_2(t) \approx V_{DD} \cdot e^{-t/\tau_E}$

Let's denote the two solutions to the characteristic equation  $s_1$  and  $s_2$ , respectively. For the case of a falling output the solution is:

$$V_2(t) = V_{21} e^{s_1 t} + V_{22} e^{s_2 t}$$

Characteristic eq. also yields sum of the two time constants  $\tau_E = \underbrace{(-\frac{1}{s_1})}_{\tau_1} + \underbrace{(-\frac{1}{s_2})}_{\tau_2} = R_1 (C_1 + C_2) + R_2 C_2$

Propagation delay:  $t_D = 0.7 \times \tau_E$

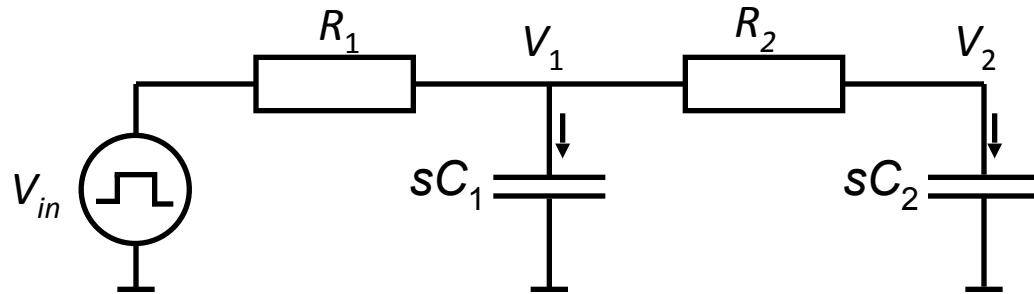

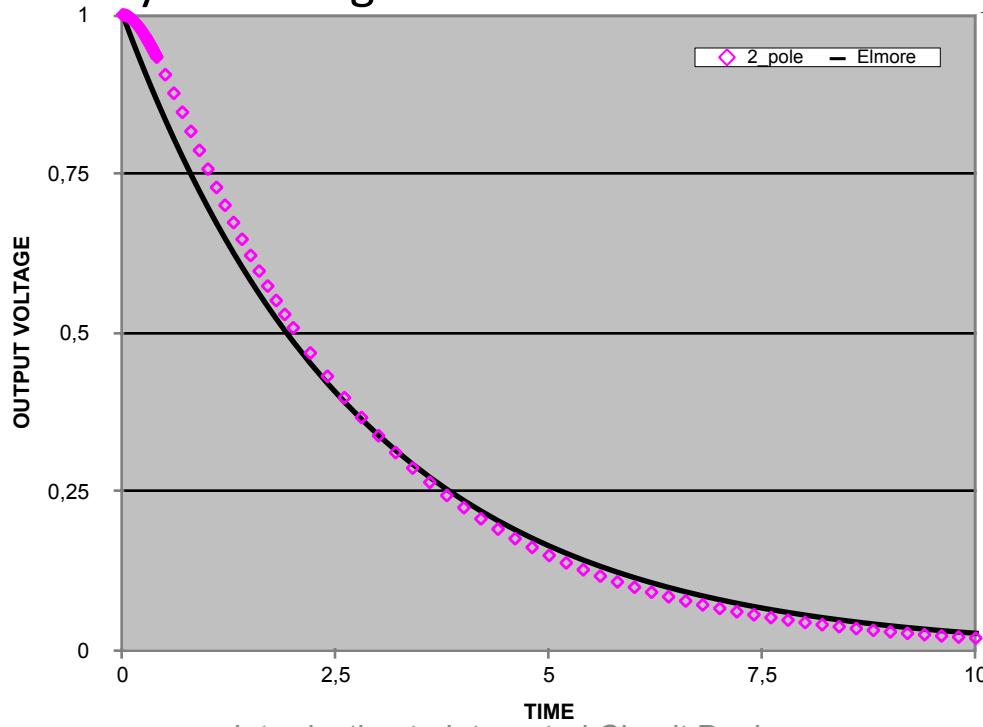

# Approximative solution

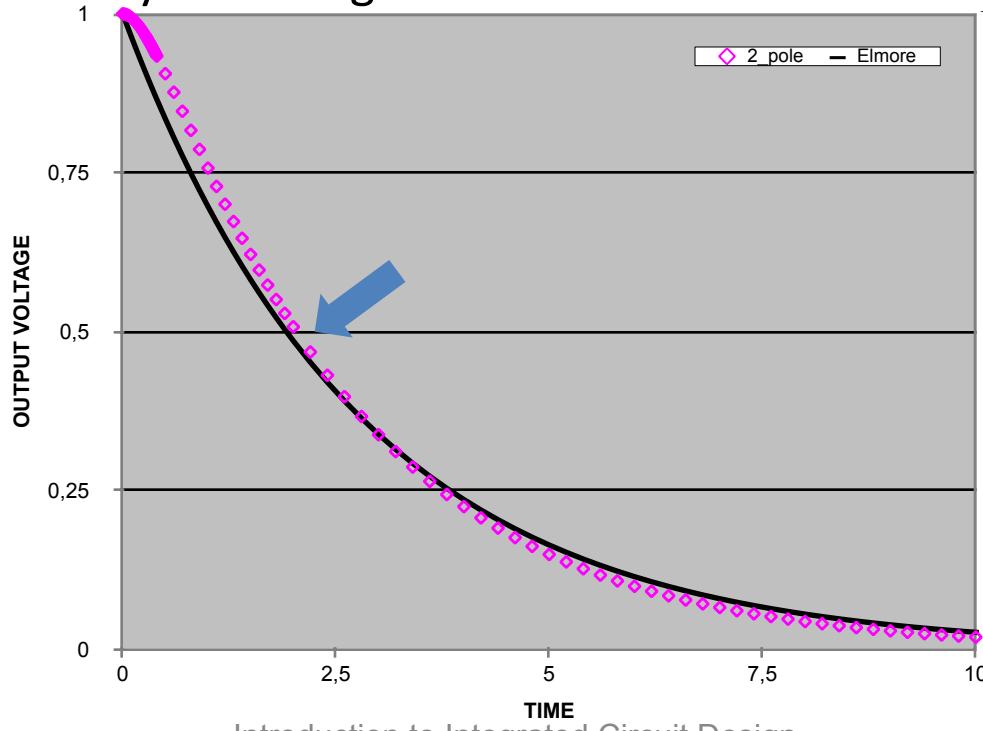

Let's have a look at a circuit example where  $R_1=0.8R_2$ ,  $C_1=1.2C_2$ . Already for these 20% differences between  $R_1$  and  $R_2$ ,  $C_1$  and  $C_2$ , respectively, one of the time constants become dominant, i. e.  $\tau_1=2.45$ ,  $\tau_2=0.3$ . This graph compares the exact two-pole solution with the approximative exponential decay assuming a dominant time constant  $\tau_E=\tau_1+\tau_2=2.75$ .

# Approximative solution

Let's have a look at a circuit example where  $R_1=0.8R_2$ ,  $C_1=1.2C_2$ . Already for these 20% differences between  $R_1$  and  $R_2$ ,  $C_1$  and  $C_2$ , respectively, one of the time constants become dominant, i. e.  $\tau_1=2.45$ ,  $\tau_2=0.3$ . This graph compares the exact two-pole solution with the approximative exponential decay assuming a dominant time constant  $\tau_E=\tau_1+\tau_2=2.75$ .

# Approximative solution

Let's have a look at a circuit example where  $R_1=0.8R_2$ ,  $C_1=1.2C_2$ . Already for these 20% differences between  $R_1$  and  $R_2$ ,  $C_1$  and  $C_2$ , respectively, one of the time constants become dominant, i. e.  $\tau_1=2.45$ ,  $\tau_2=0.3$ . This graph compares the exact two-pole solution with the approximative exponential decay assuming a dominant time constant  $\tau_E=\tau_1+\tau_2=2.75$ .

# How to remember delay formula?

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

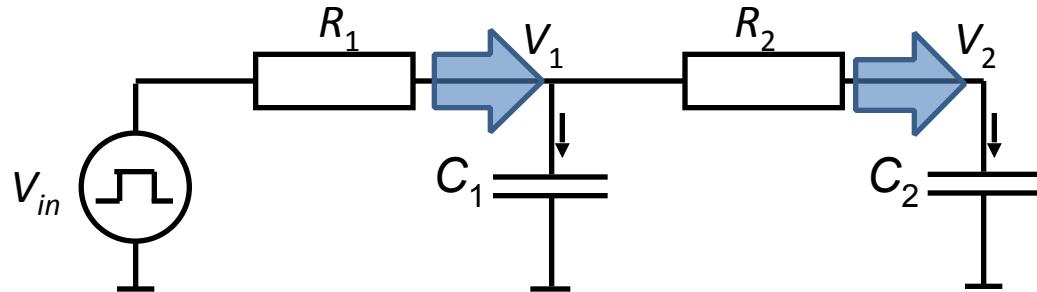

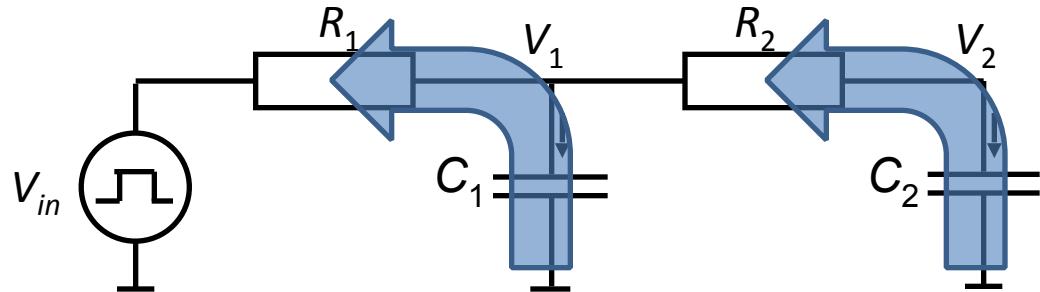

- Now, let us return to the simplified two-stage RC circuit

- How to remember how to get the dominant time constant?

# How to remember delay formula?

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

- Now, let us return to the simplified two-stage RC circuit

- How to remember how to get the dominant time constant?

Each resistance is multiplied by its downstream capacitance!

$$T_E = R_1(C_1 + C_2) + R_2C_2$$

# How to remember delay formula?

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

- Now, let us return to the simplified two-stage RC circuit

- How to remember how to get the dominant time constant?

Or: Each capacitance is multiplied by its upstream resistance!

$$T_E = R_1 C_1 + (R_1 + R_2) C_2$$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Dominating delay time constant becomes:  $T_E = R(C_D + C + C_w) + R_w \left( C + \frac{C_w}{2} \right)$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Dominating delay time constant becomes:  $T_E = R(C_D + C + C_w) + R_w \left( C + \frac{C_w}{2} \right)$

$$T_E = \underbrace{R(C_D + C)}_{=2 \times 7.2 \text{ ps if } p_{inv}=1} + \underbrace{R C_w}_{R \text{ is unknown}} + \underbrace{R_w C}_{C \text{ is unknown}} + \underbrace{\frac{R_w C_w}{2}}_{80 \text{ ps}} \geq 94.4 \text{ ps}$$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_W C_W$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Dominating time constant  $T_E$  can be normalized wrt technology time constant  $RC$ !

$$d = \underbrace{\frac{T_E}{RC}}_{inverter} = p_{inv} + 1 + \frac{R_w C_w}{RC} \frac{R}{R_w} + \frac{R_w}{R} + \frac{R_w C_w}{2RC}$$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{\text{eff}} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

At this point, I have found it convenient to introduce the wire effort  $W_E$ :  $W_E = \frac{R_w C_w}{RC}$

$$d = \underbrace{\frac{T_E}{RC}}_{\text{inverter}} = p_{\text{inv}} + 1 + \frac{R_w C_w}{RC} \frac{R}{R_w} + \frac{R_w}{R} + \frac{R_w C_w}{2RC}$$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c=200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{\text{eff}} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

At this point, I have found it convenient to introduce the wire effort  $W_E$ :  $W_E = \frac{R_w C_w}{RC}$

In our example,  $W_E = 160/7.2 \approx 22$

$$d = \underbrace{\frac{T_E}{RC}}_{\text{inverter}} = p_{\text{inv}} + 1 + \frac{R_w C_w}{RC} \frac{R}{R_w} + \frac{R_w}{R} + \frac{R_w C_w}{2RC}$$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c=200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{\text{eff}} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

At this point, I have found it convenient to introduce the wire effort  $W_E$ :  $W_E = \frac{R_w C_w}{RC}$

In our example,  $W_E = 160/7.2 \approx 22$

and the normalized delay can be written  $d = p_{\text{inv}} + 1 + W_E \frac{R}{R_w} + \frac{R_w}{R} + \frac{W_E}{2}$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Having developed a delay model based on the assumption of a dominating time constant, let's apply the model for finding the size of the inverter minimizing the delay!

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Having developed a delay model based on the assumption of a dominating time constant, let's apply the model for finding the size of the inverter minimizing the delay!

$$\frac{\partial d}{\partial R} = \frac{W_E}{R_W} - \frac{R_W}{R^2} = 0 \rightarrow R_{optimal} = \frac{R_W}{\sqrt{W_E}}; R_W = 0.8 \text{ k} \quad W_E = \quad \rightarrow R_{optimal} =$$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_W C_W$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Having defined inverter size  $10X$  for inverters with  $R=2 \text{ k}\Omega$ ,  $120X$  is the inverter size with  $R_{eff}=170 \Omega$  minimizing the delay caused by the wire.

Assuming  $p_{inv} = 1$ , and having  $W_E=22$ , we obtain  $d_{min} = \underbrace{2}_{p_{inv}=1} + 2\sqrt{W_E} + \frac{W_E}{2} = 22.5$

# Return to wire delay example

Estimate the delay of an inverter driving an identical inverter at the end of the 1 mm wire!  $W_P=2W_N$ .

Assume wire cap  $c= 200 \text{ fF/mm}$ ,  $r=800 \Omega/\text{mm}$  (from previous examples)

The wire will affect the propagation delay if wire RC product  $R_w C_w$  is larger than the well-known inverter RC product  $R_{eff} C_G = 2 \text{ k}\Omega \times 3.6 \text{ fF} = 7.2 \text{ ps}$ .

Having defined inverter size  $10X$  for inverters with  $R=2 \text{ k}\Omega$ ,  $120X$  is the inverter size with  $R_{eff}=170 \Omega$  minimizing the delay caused by the wire.

Total delay becomes 22.5 multiples of the basic 5 ps that we have defined for the 65 nm CMOS process, i.e. 112.5 ps, a value to be compared to the 10 ps with no wire.

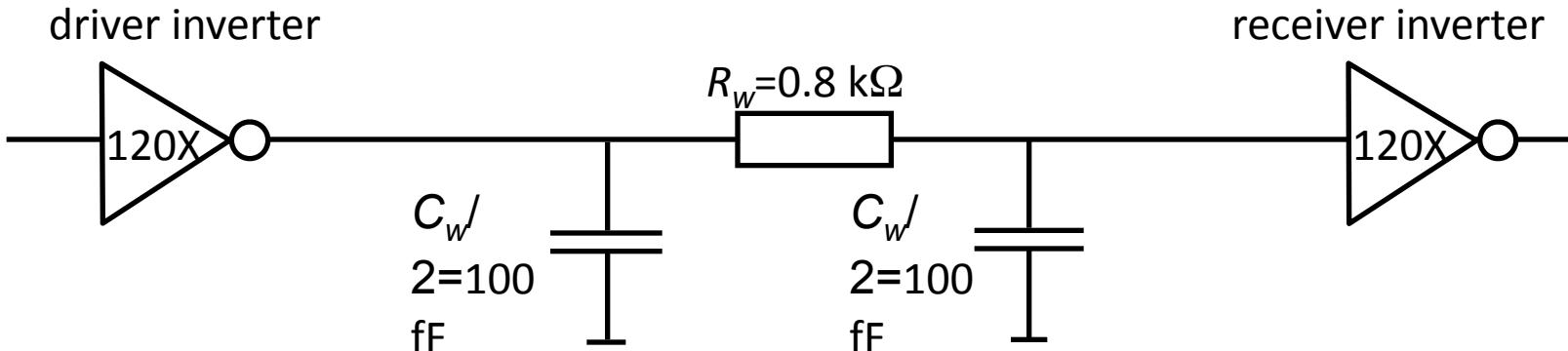

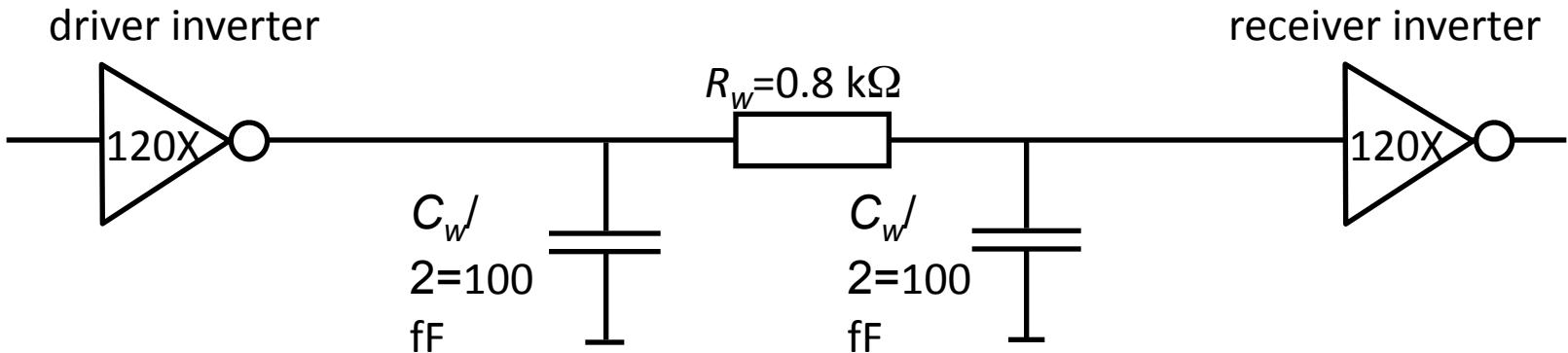

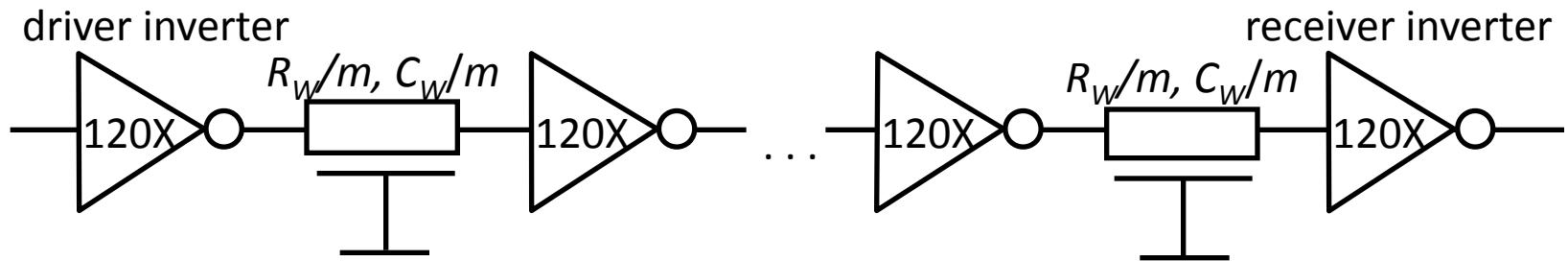

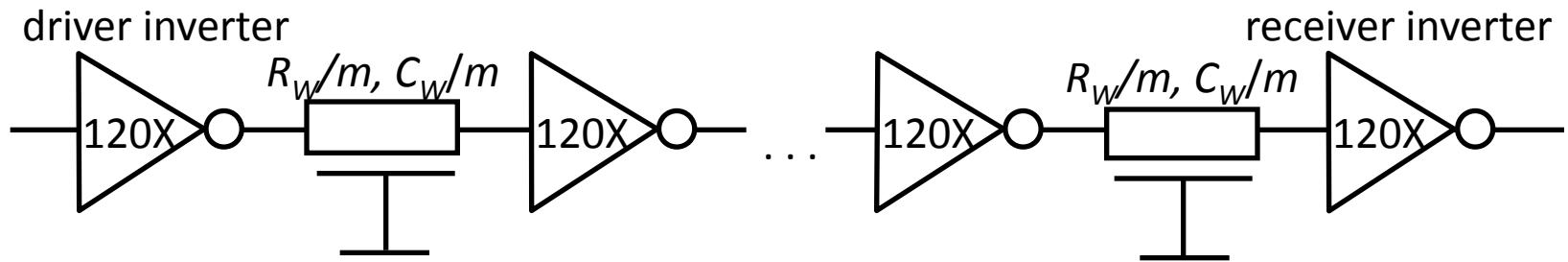

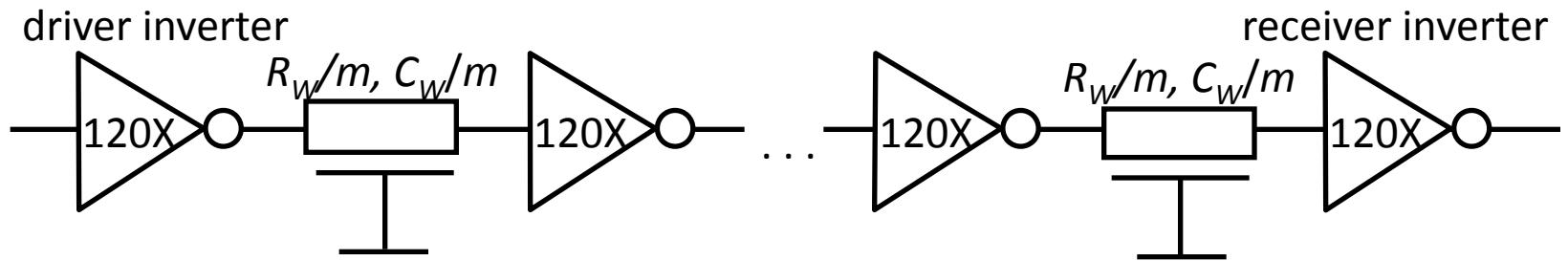

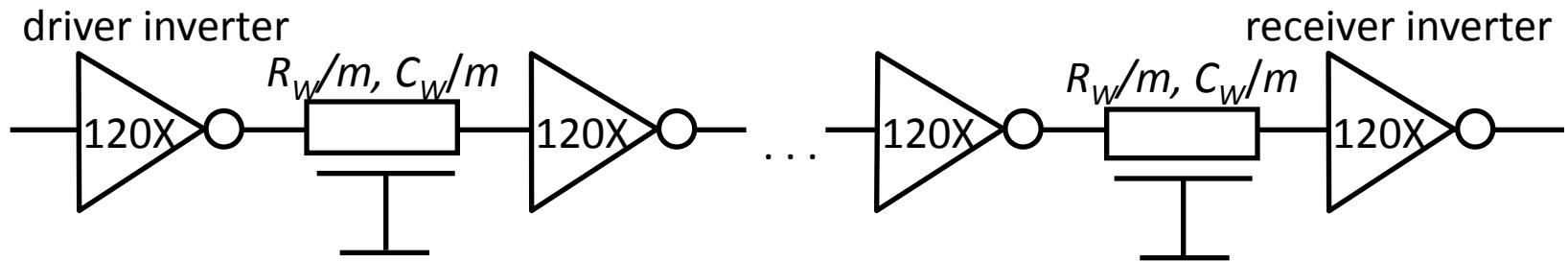

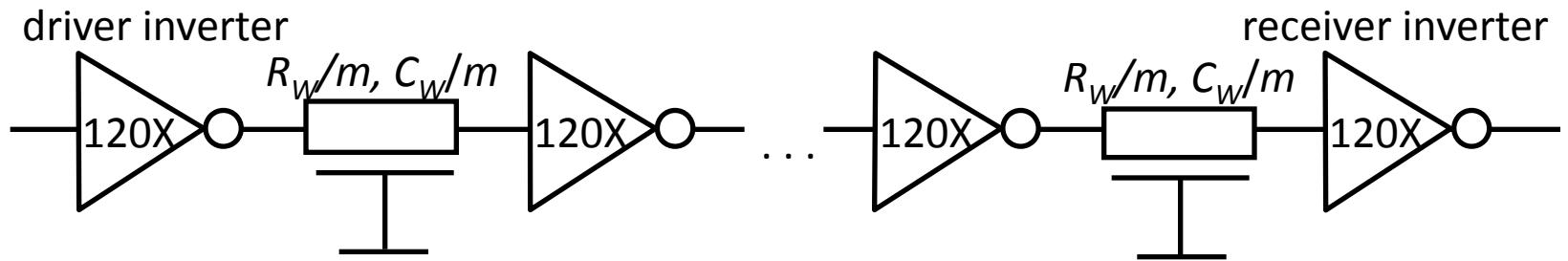

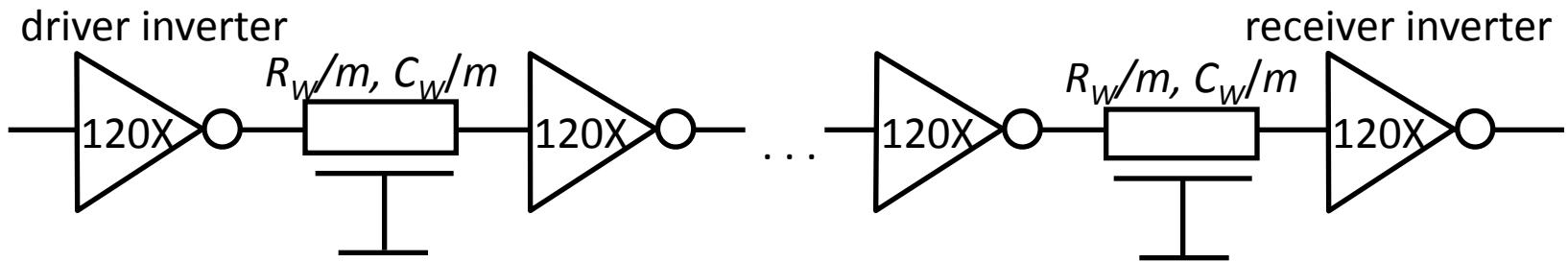

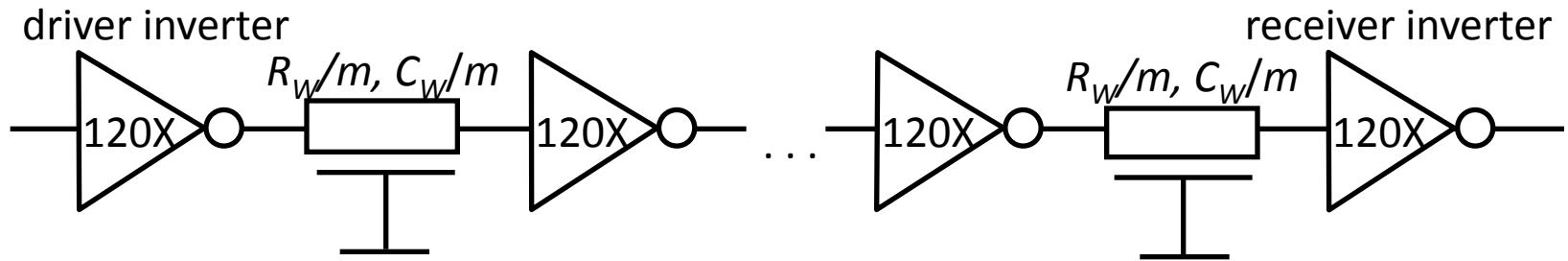

# Keeping wires short using repeaters

For keeping wires short, what if we divide the wire in the example into 2 segments by inserting a repeater in the middle?

A repeater is just an identical inverter that we call repeater!

To estimate the propagation delay, just add the two segment delays!

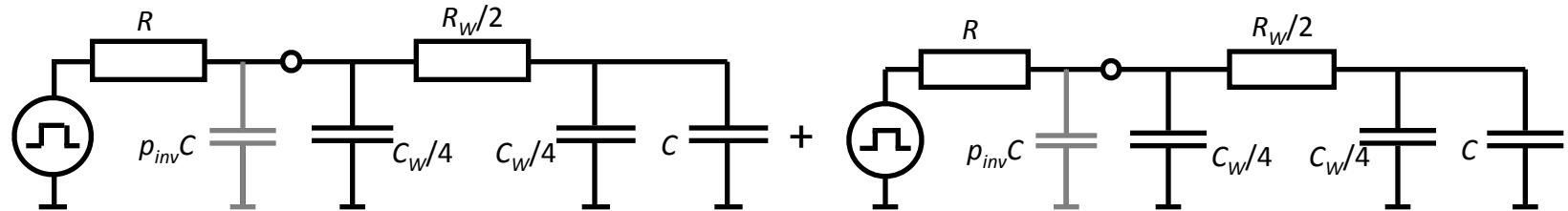

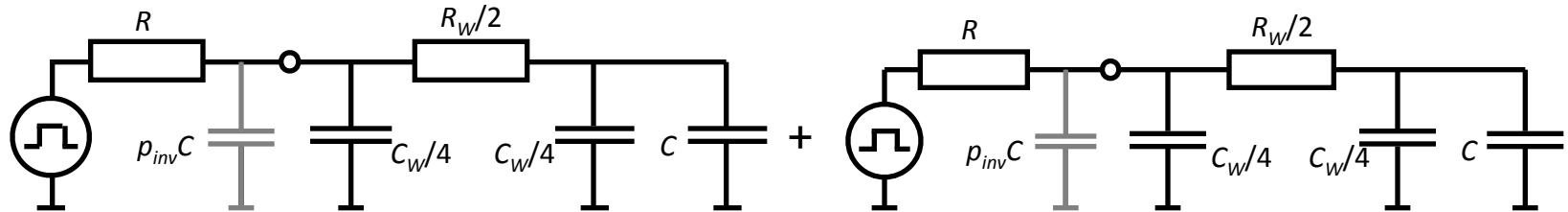

# Keeping wires short using repeaters

For keeping wires short, what if we divide the example wire into 2 segments and insert a repeater?

A repeater is just an identical inverter that we call repeater!

To estimate the propagation delay, just add the two segment delays!

# Keeping wires short using repeaters

For keeping wires short, what if we divide the example wire into 2 segments and insert a repeater?

A repeater is just an identical inverter that we call repeater!

To estimate the propagation delay, just add the two segment delays!

If we keep the total wire effort  $W_E=22$ , the sum of the two stage delays is

$$d = 2 \times \left( \underbrace{p_{inv} + 1}_{4} + \frac{W_E}{4} \frac{R}{R_w/2} + \frac{R_w/2}{R} + \frac{W_E/4}{2} \right) \quad (\text{Using delay Eq. on slide 27})$$

# Keeping wires short using repeaters

For keeping wires short, what if we divide the example wire into 2 segments and insert a repeater?

A repeater is just an identical inverter that we call repeater!

To estimate the propagation delay, just add the two segment delays!

If we keep the total wire effort  $W_E=22$ , the sum of the two stage delays is

$$d = 2 \times \left( \underbrace{p_{inv} + 1}_{\text{Stage 1 delay}} + \frac{W_E}{4} \frac{R}{R_w/2} + \frac{R_w/2}{R} + \frac{W_E/4}{2} \right) \quad (\text{Using delay Eq. on slide 27})$$

Keeping  $R_{eff} = R_{opt} = \frac{R_w}{\sqrt{W_E}}$   $\rightarrow d_{min} = 2 \times \left( 2 + \sqrt{W_E} + \frac{W_E}{8} \right) = 2 \times (2 + 2.35 + 2.35 + 2.8) = 19$

# Keeping wires short using repeaters

For keeping wires short, what if we divide the example wire into 2 segments and insert a repeater?

A repeater is just an identical inverter that we call repeater!

To estimate the propagation delay, just add the two segment delays!

If we keep the total wire effort  $W_E=22$ , the sum of the two stage delays is

$$d = 2 \times \left( \underbrace{p_{inv} + 1}_{\text{Stage 1}} + \frac{W_E}{4} \frac{R}{R_w/2} + \frac{R_w/2}{R} + \frac{W_E/4}{2} \right) \quad (\text{Using delay Eq. on slide 27})$$

$$\text{Keeping } R_{eff} = R_{opt} = \frac{R_w}{\sqrt{W_E}} \rightarrow d_{min} = 2 \times \left( 2 + \sqrt{W_E} + \frac{W_E}{8} \right) = 2 \times (2 + 2.35 + 2.35 + 2.8) = 19$$

Just a small decrease of the wire delay (from 22.5 to 19)! But still . . .

# Keeping wires short using repeaters

But what if the wire is much longer, say 10-15 mm?

What would be the optimal number of segments,  $m$ , into which the wire should be split by inserting  $m-1$  identical repeaters for minimizing the delay?

# Keeping wires short using repeaters

But what if the wire is much longer, say 10-15 mm?

What would be the optimal number of segments,  $m$ , into which the wire should be split by inserting  $m-1$  identical repeaters for minimizing the delay?

If we keep  $W_E$  as the total wire effort, the delay can be written

$$d = m \times \left( \underbrace{p_{inv}}_{+1} + \frac{W_E}{m^2} \frac{R}{R_w/m} + \frac{R_w/m}{R} + \frac{W_E}{2m^2} \right) \rightarrow m_{opt} = \sqrt{\frac{W_E}{2(p_{inv} + 1)}} = \underbrace{\frac{\sqrt{W_E}}{2}}_{p_{inv}=1}$$

# Keeping wires short using repeaters

But what if the wire is much longer, say 10-15 mm?

What would be the optimal number of segments,  $m$ , into which the wire should be split by inserting  $m-1$  identical repeaters for minimizing the delay?

If we keep  $W_E$  as the total wire effort, the delay can be written

$$d = m \times \left( \underbrace{p_{inv}}_{-} + 1 + \frac{W_E}{m^2} \frac{R}{R_w/m} + \frac{R_w/m}{R} + \frac{W_E}{2m^2} \right) \rightarrow m_{opt} = \sqrt{\frac{W_E}{2(p_{inv} + 1)}} = \frac{\sqrt{W_E}}{\underbrace{2}_{p_{inv}=1}}$$

The previous inverter sizing is still optimal, since the two middle terms yielding the relationship between  $R$  and  $R_w$  are independent of  $m$ !

# Keeping wires short using repeaters

But what if the wire is much longer, say 10-15 mm?

What would be the optimal number of segments,  $m$ , into which the wire should be split by inserting  $m-1$  identical repeaters for minimizing the delay?

What is the critical wire length for considering repeater insertion?

# Keeping wires short using repeaters

But what if the wire is much longer, say 10-15 mm?

What would be the optimal number of segments,  $m$ , into which the wire should be split by inserting  $m-1$  identical repeaters for minimizing the delay?

What is the critical wire length for considering repeater insertion?

$$L_{crit} = \frac{L}{m_{opt}} = \frac{2L}{\sqrt{W_E}} = 2\sqrt{\frac{RC}{rc}} = 2\sqrt{\frac{7.2}{160}} = 0.42 \text{ mm}$$

# Keeping wires short using repeaters

But what if the wire is much longer, say 10-15 mm?

What would be the optimal number of segments,  $m$ , into which the wire should be split by inserting  $m-1$  identical repeaters for minimizing the delay?

What is the critical wire length for considering repeater insertion?

$$L_{crit} = \frac{L}{m_{opt}} = \frac{2L}{\sqrt{W_E}} = 2\sqrt{\frac{RC}{rc}} = 2\sqrt{\frac{7.2}{160}} = 0.42 \text{ mm}$$

Hence, in the case of our 1 mm wire example, it's optimal to divide wire in two segments. However, the gain was small and the signal became inverted

# Example: 10 mm wire

But what if the wire is much longer, say 10 mm?

The critical length being 0.42 mm suggests insertion of 22 repeaters,

i.e. that we should divide the wire into 23 segments.

The wire effort is now  $W_E = 16000/7.2 \approx 2200$

Hence, minimum normalized delay is  $4\sqrt{W_E} = 188 \approx 190$ .

Summarizing the 23 stage delays gives the same result:

$$d = 23 \times 2 + 2\sqrt{W_E} + \frac{W_E}{46} = 46 + 2 \times 47 + 48 = 188 \approx 190$$

Important comment: An even number of repeaters does not invert the signal!

# Conclusion

- Introduced a distributed wire RC model, the  $\pi$ -model

- Discussed the relevance of a delay model assuming the existence of a dominant time constant

- Understood that wires should be kept short since wire delay or flight time, increases with the wire length squared!

$$W_E = \frac{rcL^2}{RC} \sim L^2 ! \text{ Therefore, keep wires short!}$$

- For long wires, delay can be minimized by inserting repeaters

- We have derived expressions for the optimal number of segments,  $m_{opt}$ , and for the critical wire length  $L_{crit}$

$$L_{crit} = \frac{L}{m_{opt}} = 2 \sqrt{\frac{(RC)_{inverter}}{(rc)_{wire}}}$$

# Introduction to on-chip interconnect

Elmore delay model

Lecture 7 continued

Tuesday October 2, 2018

# Outline

- Elmore delay model – a generalized model

- How to handle wire branches

- Conclusions

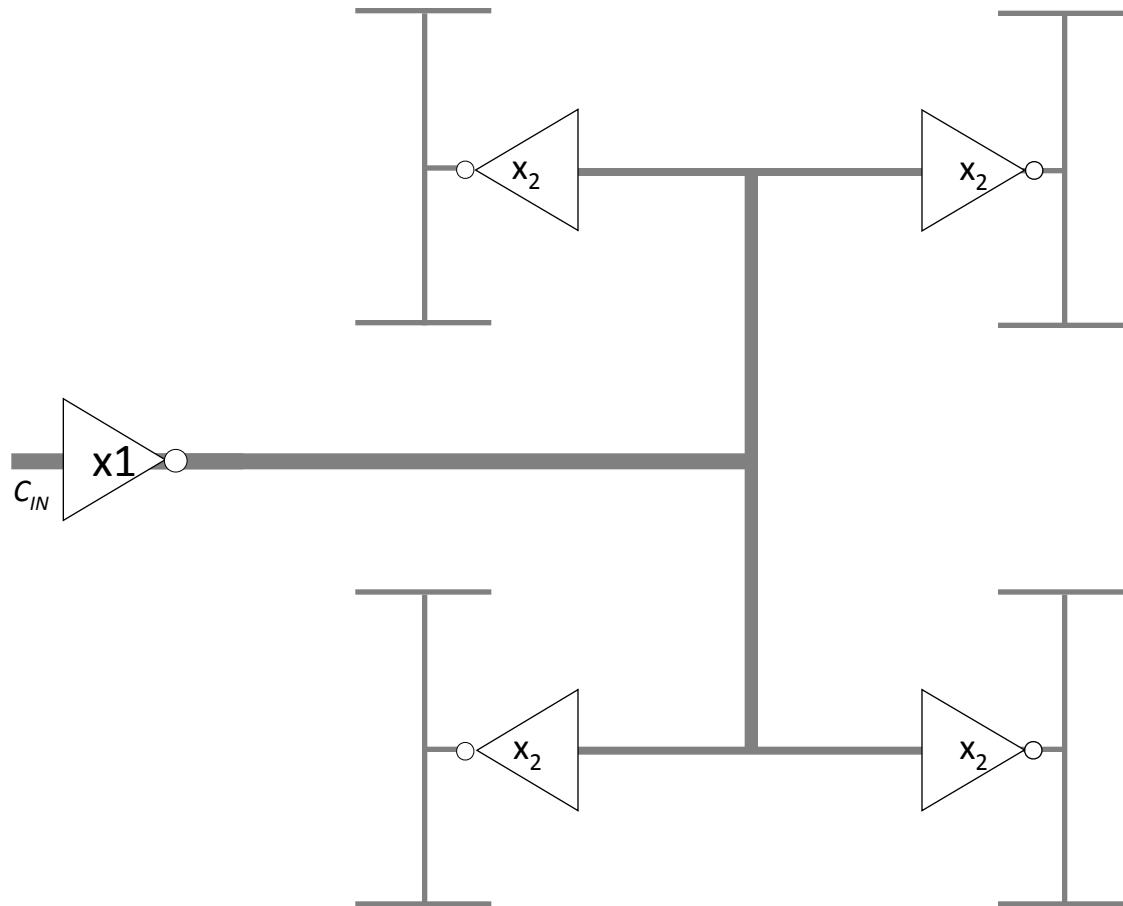

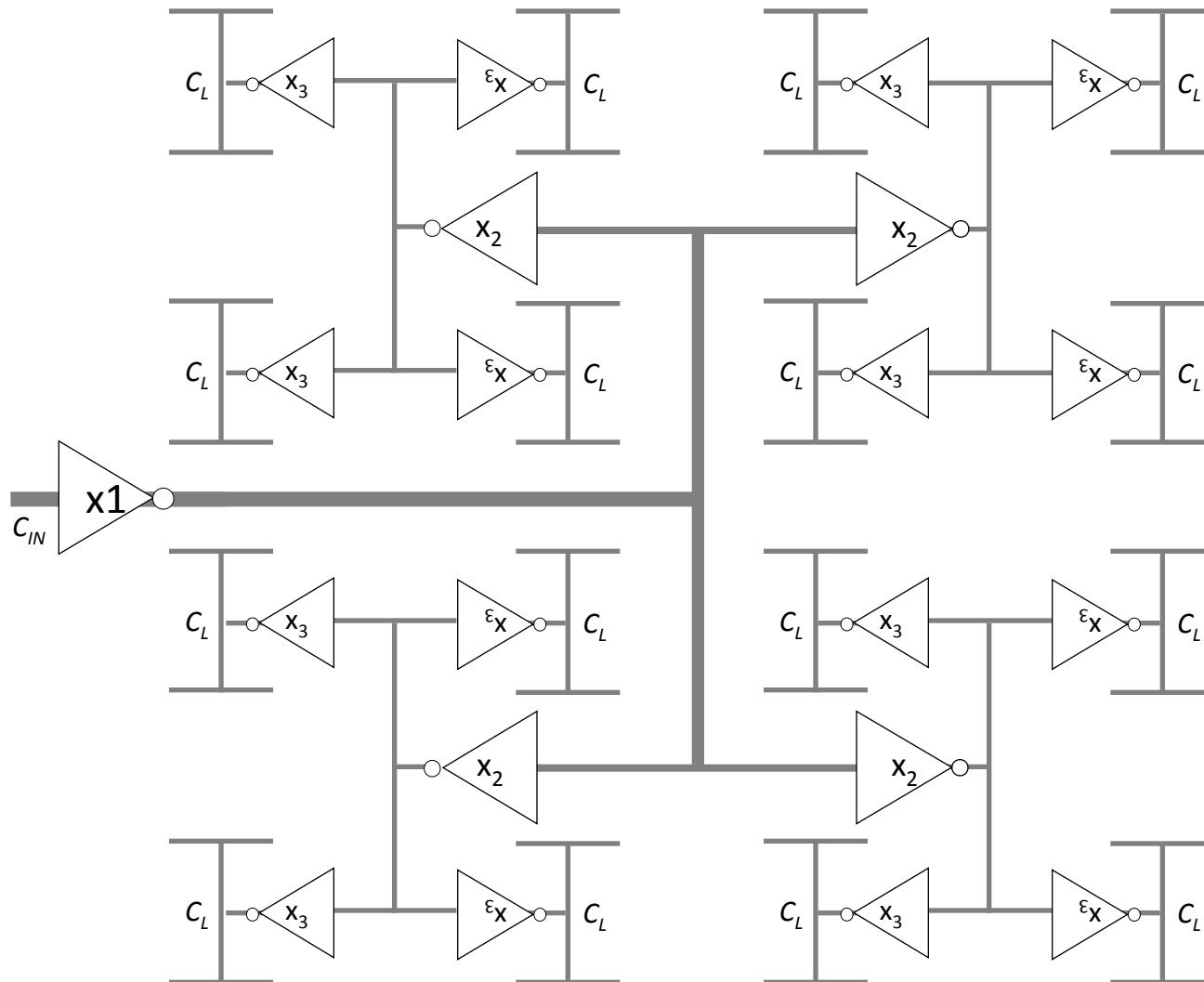

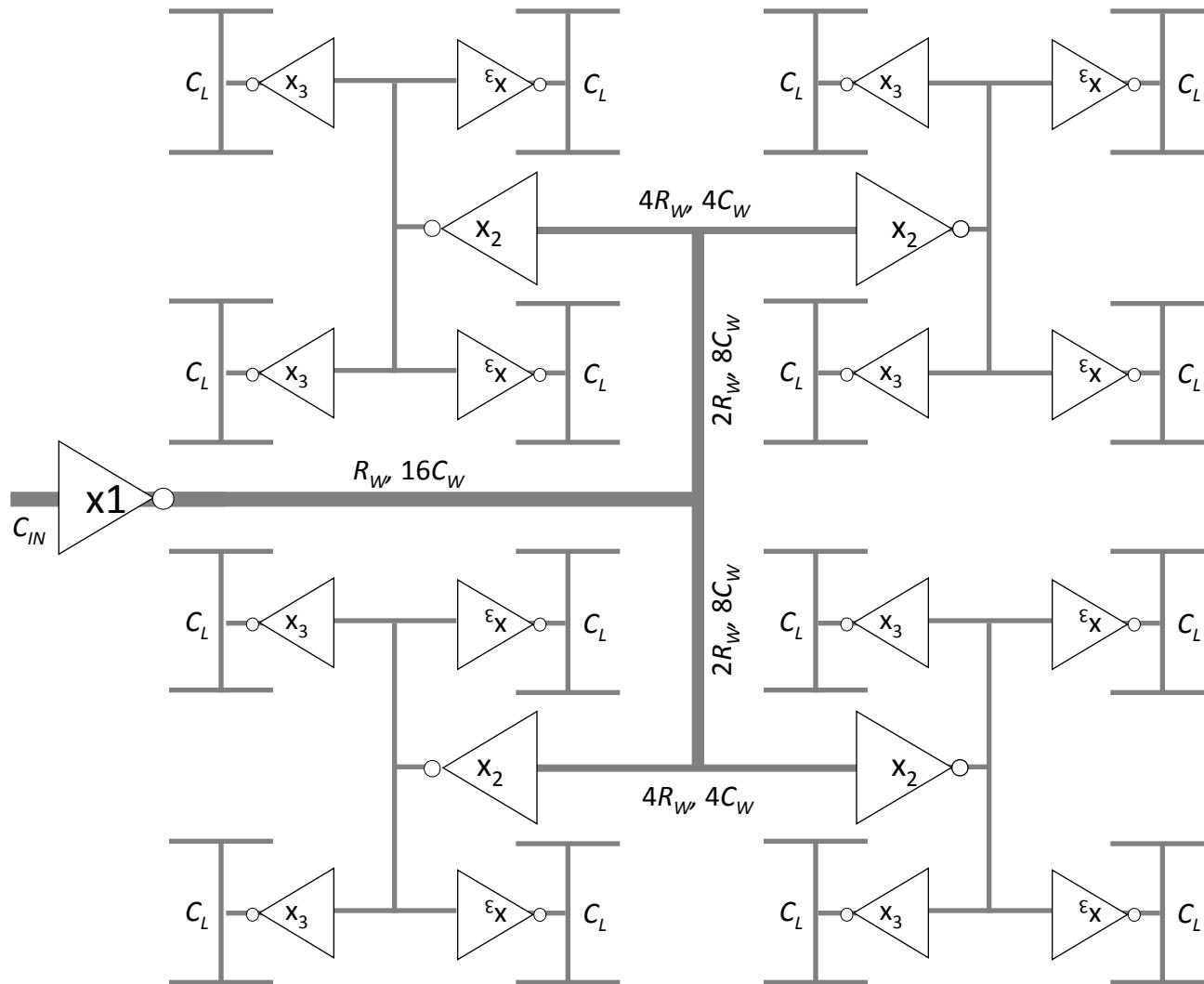

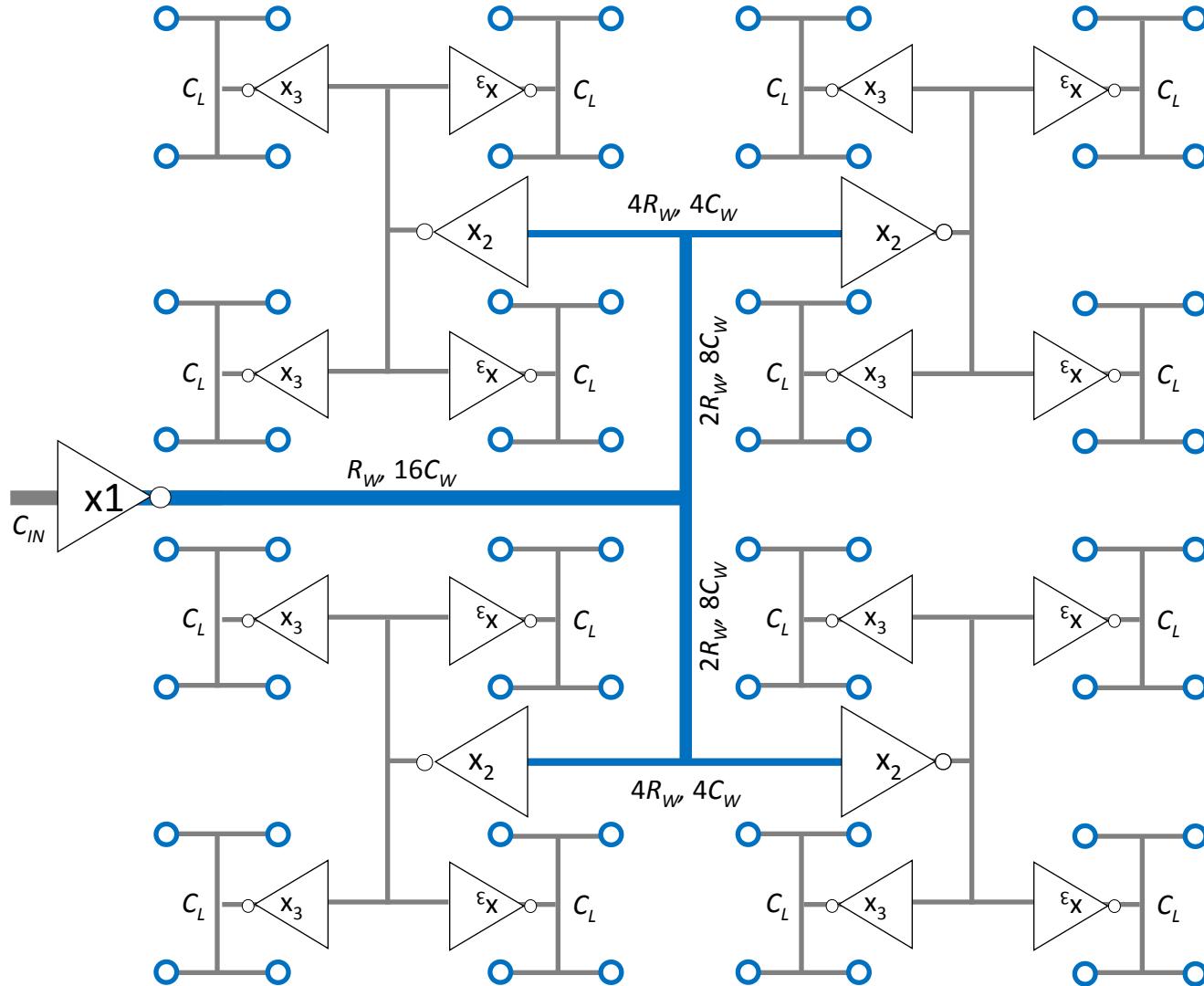

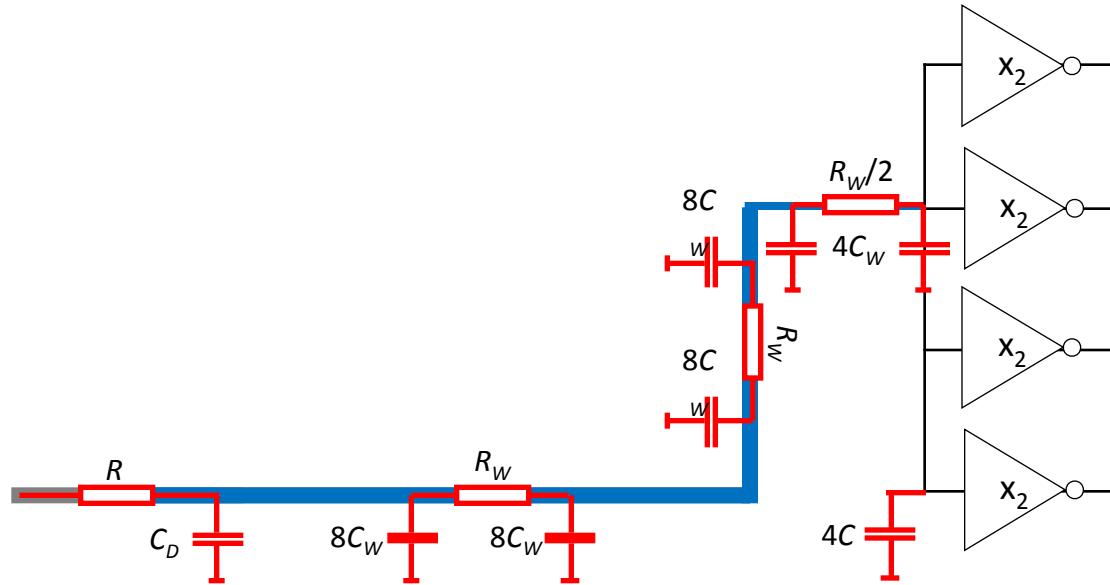

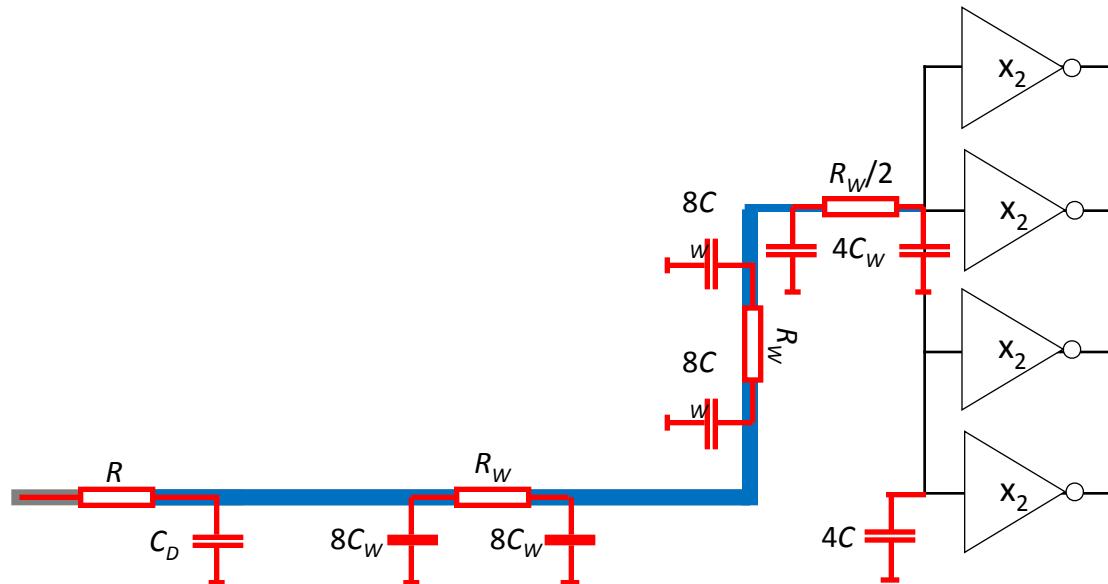

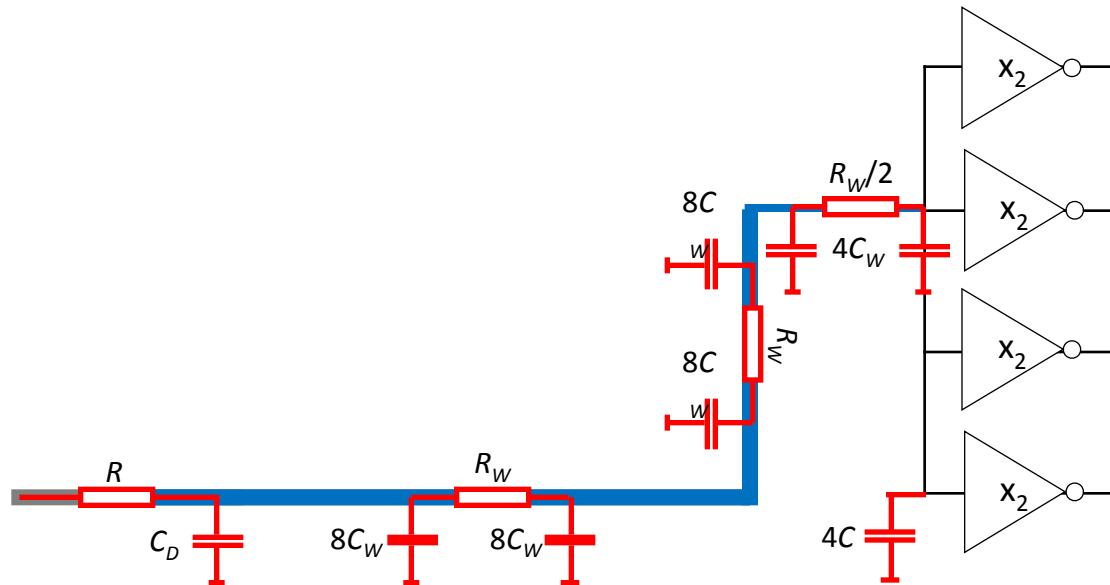

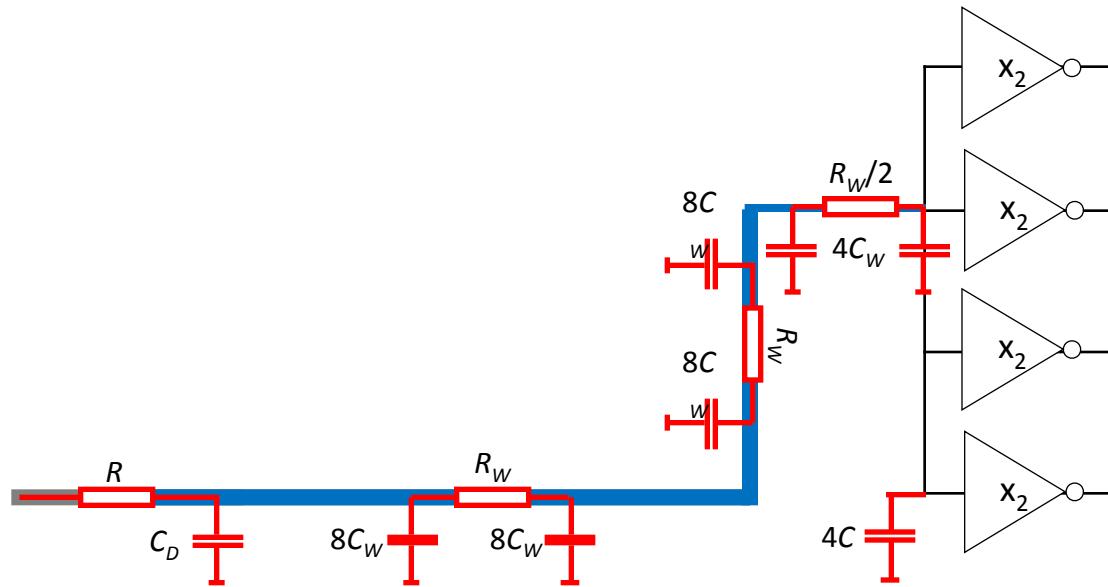

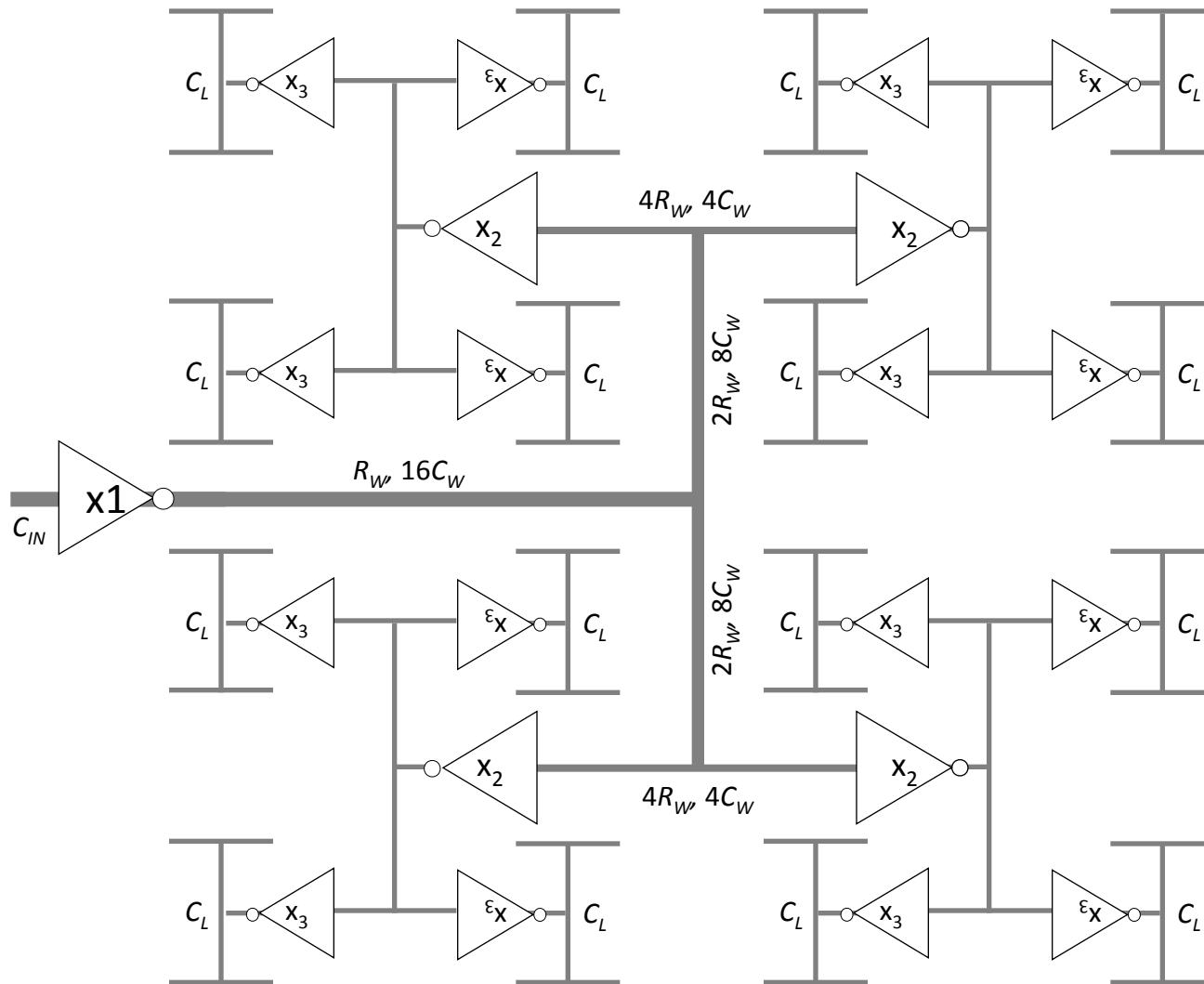

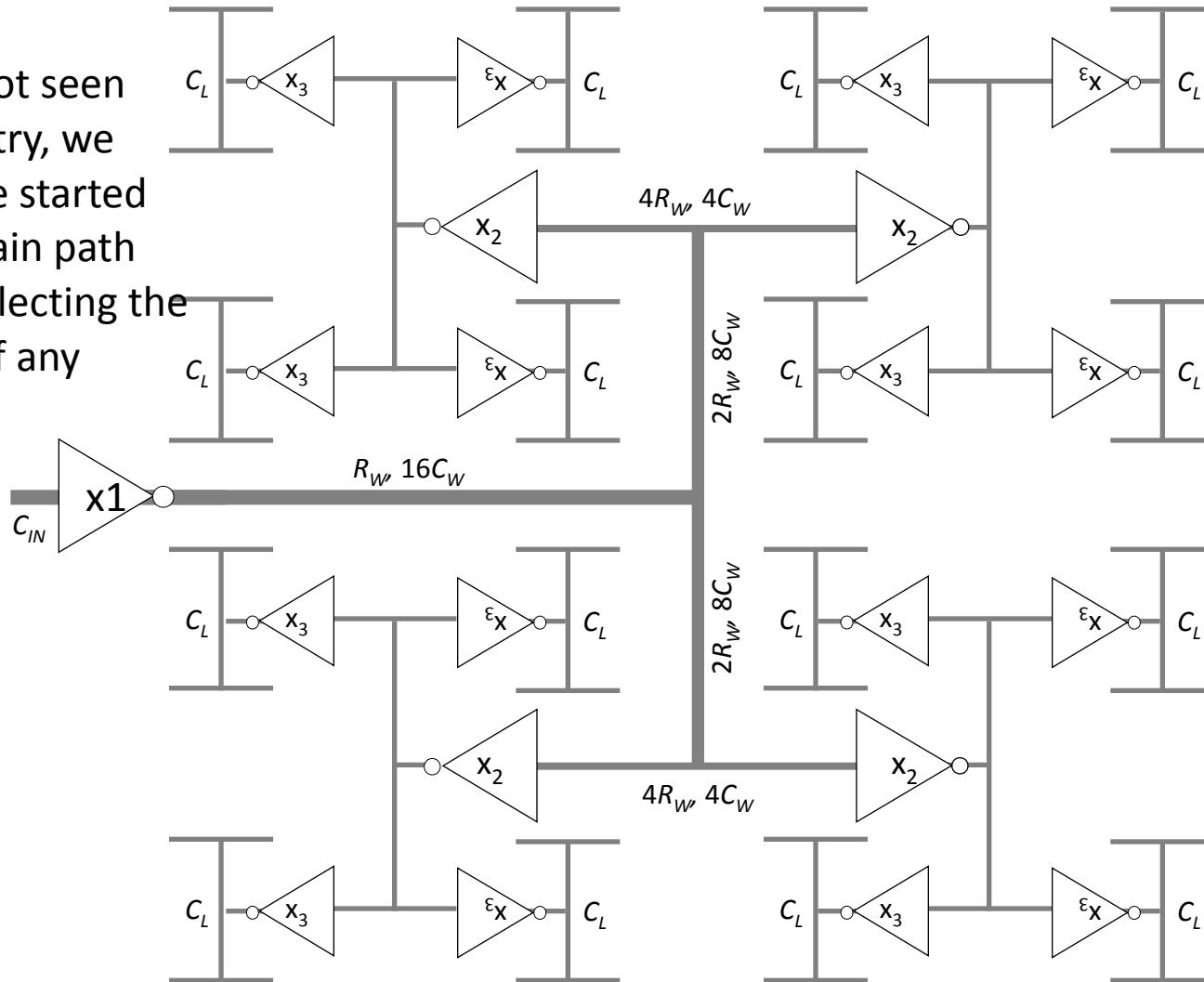

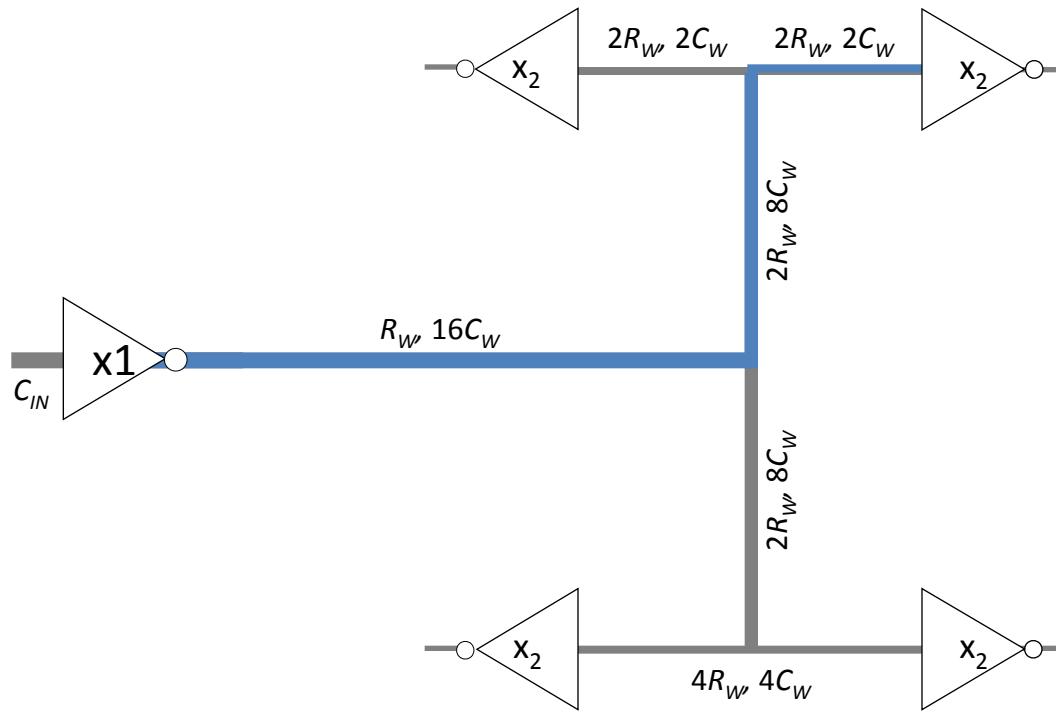

# H-tree clock distribution

# H-tree clock distribution

# H-tree clock distribution

# H-tree clock distribution

# H-tree clock distribution

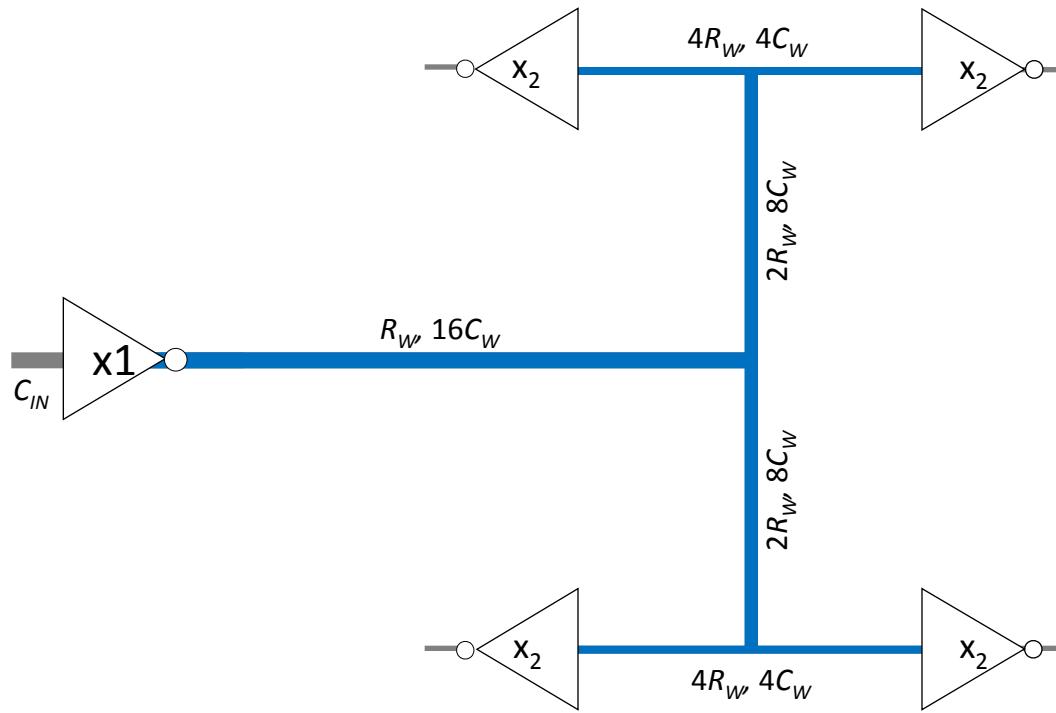

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

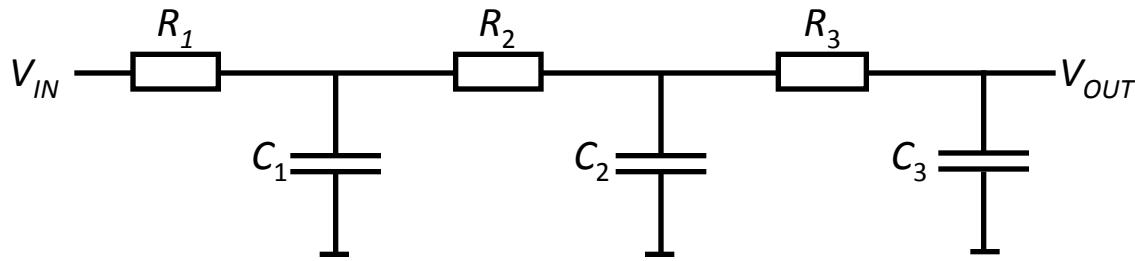

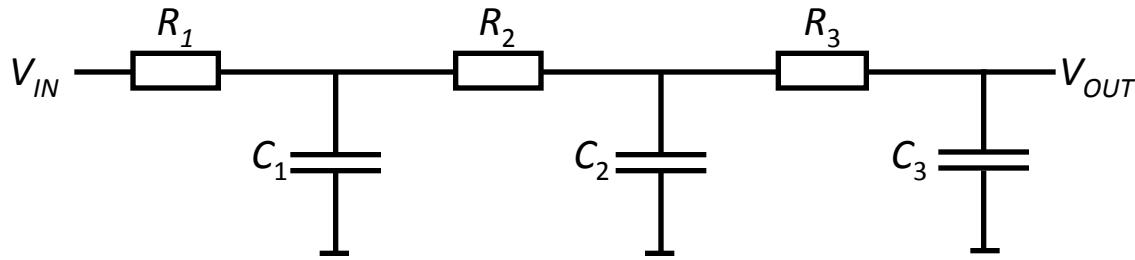

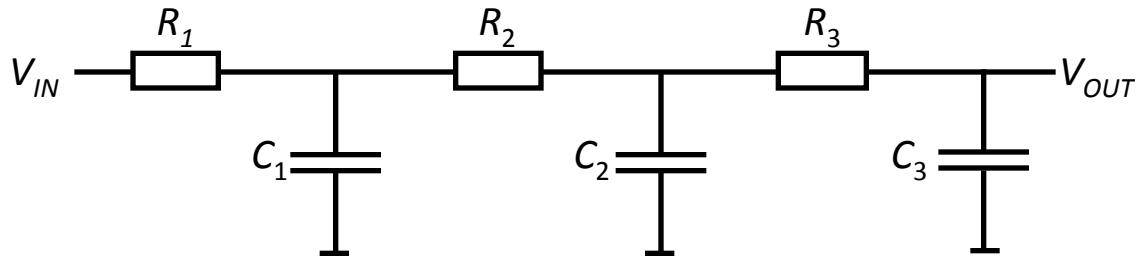

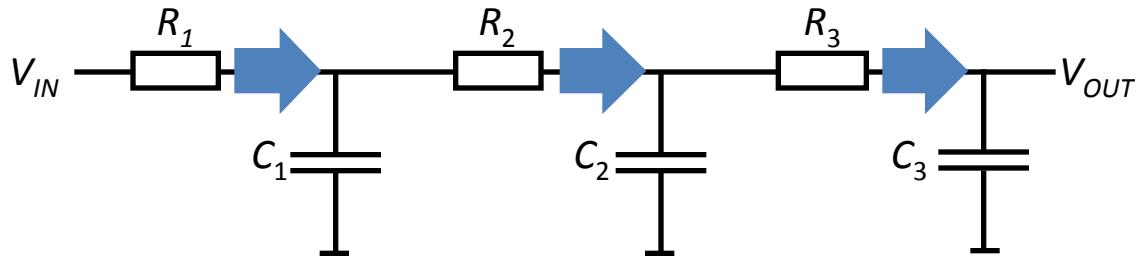

# General solution

# General solution

Transfer function

$$H(s) = \frac{1}{as^3 + bs^2 + cs + 1}$$

$$a = R_1 R_2 R_3 C_1 C_2 C_3$$

$$b = R_1 R_2 C_1 C_2 + R_1 R_2 C_1 C_3 + R_1 R_3 C_2 C_3 + R_2 R_3 C_2 C_3$$

$$c = R_1 (C_1 + C_2 + C_3) + R_2 (C_2 + C_3) + R_3 C_3$$

# General solution

Transfer function

$$H(s) = \frac{1}{as^3 + bs^2 + cs + 1}$$

$$a = R_1 R_2 R_3 C_1 C_2 C_3$$

$$b = R_1 R_2 C_1 C_2 + R_1 R_2 C_1 C_3 + R_1 R_3 C_2 C_3 + R_2 R_3 C_2 C_3$$

$$c = R_1 (C_1 + C_2 + C_3) + R_2 (C_2 + C_3) + R_3 C_3$$

This transfer function corresponds to a third order linear differential equation

The solution is a sum of three exponentials with three different time constants

We cannot solve this analytically.

But if we assume that there is a dominant time constant  $T_E$  it is given by  $c$

# General solution

Transfer function

$$H(s) = \frac{1}{as^3 + bs^2 + cs + 1}$$

$$a = R_1 R_2 R_3 C_1 C_2 C_3$$

$$b = R_1 R_2 C_1 C_2 + R_1 R_2 C_1 C_3 + R_1 R_3 C_2 C_3 + R_2 R_3 C_2 C_3$$

$$c = R_1 (C_1 + C_2 + C_3) + R_2 (C_2 + C_3) + R_3 C_3$$

This transfer function corresponds to a third order linear differential equation

The solution is a sum of three exponentials with three different time constants

We cannot solve this analytically.

But if we assume that there is a dominant time constant  $T_E$  it is given by c

$$T_E = R_1 (C_1 + C_2 + C_3) + R_2 (C_2 + C_3) + R_3 C_3$$

# General solution

Each resistance is multiplied by its downstream capacitance!

$$T_E = R_1(C_1 + C_2 + C_3) + R_2(C_2 + C_3) + R_3C_3$$

Transfer function

$$H(s) = \frac{1}{as^3 + bs^2 + cs + 1}$$

$$a = R_1 R_2 R_3 C_1 C_2 C_3$$

$$b = R_1 R_2 C_1 C_2 + R_1 R_2 C_1 C_3 + R_1 R_3 C_2 C_3 + R_2 R_3 C_2 C_3$$

$$c = R_1(C_1 + C_2 + C_3) + R_2(C_2 + C_3) + R_3 C_3$$

This transfer function corresponds to a third order linear differential equation

The solution is a sum of three exponentials with three different time constants

We cannot solve this analytically.

But if we assume that there is a dominant time constant  $T_E$  it is given by c

$$T_E = R_1(C_1 + C_2 + C_3) + R_2(C_2 + C_3) + R_3 C_3$$

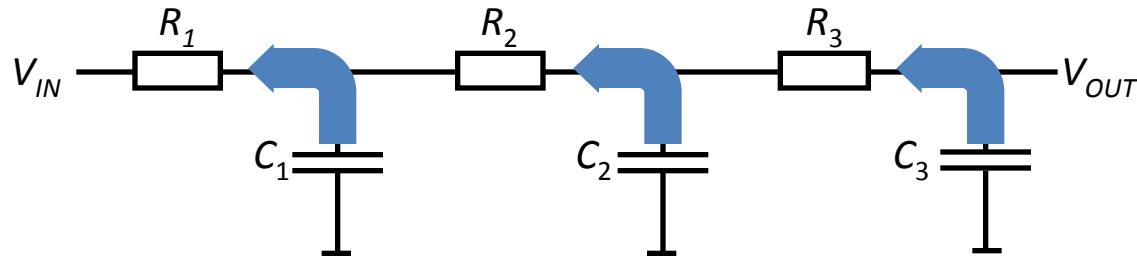

# General solution

Each capacitance is multiplied by its upstream resistance!

$$T_E = C_3(R_1 + R_2 + R_3) + C_2(R_1 + R_2) + C_1R_1$$

Transfer function

$$H(s) = \frac{1}{as^3 + bs^2 + cs + 1}$$

$$a = R_1 R_2 R_3 C_1 C_2 C_3$$

$$b = R_1 R_2 C_1 C_2 + R_1 R_2 C_1 C_3 + R_1 R_3 C_2 C_3 + R_2 R_3 C_2 C_3$$

$$c = R_1(C_1 + C_2 + C_3) + R_2(C_2 + C_3) + R_3 C_3$$

This transfer function corresponds to a third order linear differential equation

The solution is a sum of three exponentials with three different time constants

We cannot solve this analytically.

But if we assume that there is a dominant time constant  $T_E$  it is given by c

$$T_E = R_1(C_1 + C_2 + C_3) + R_2(C_2 + C_3) + R_3 C_3$$

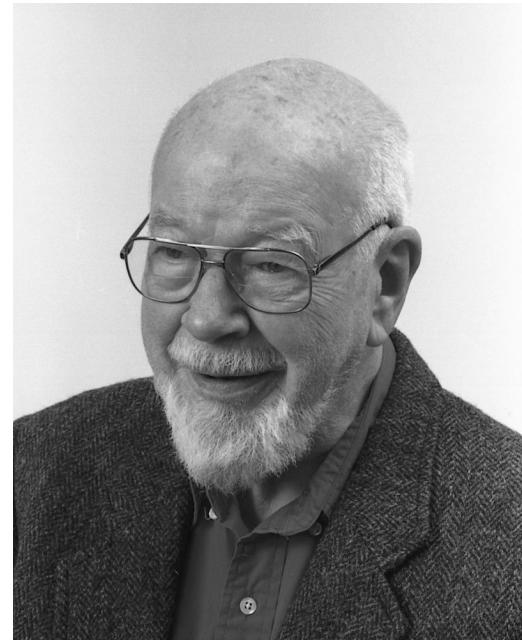

# The man behind Elmore delay

- William Cronk Elmore (1909 - 2003) was an American physicist, educator, and author.

- He is best known for his work on and related to the Manhattan project during World War II.

- Professor of Physics at Swarthmore College, Pennsylvania, from 1938 to 1974.

- Authored two influential books during his life,

- Electronics-Experimental Techniques with M. Sands

- Physics of Waves with Mark Heald.

- He is also known for deriving a simple approximation for the delay through an RC network, known as the Elmore delay.

- Despite his clear potential for advancing theoretical and experimental physics, Elmore was known for developing (and publishing) laboratory experiments that effectively taught students the fundamentals of physics.

W. C. Elmore

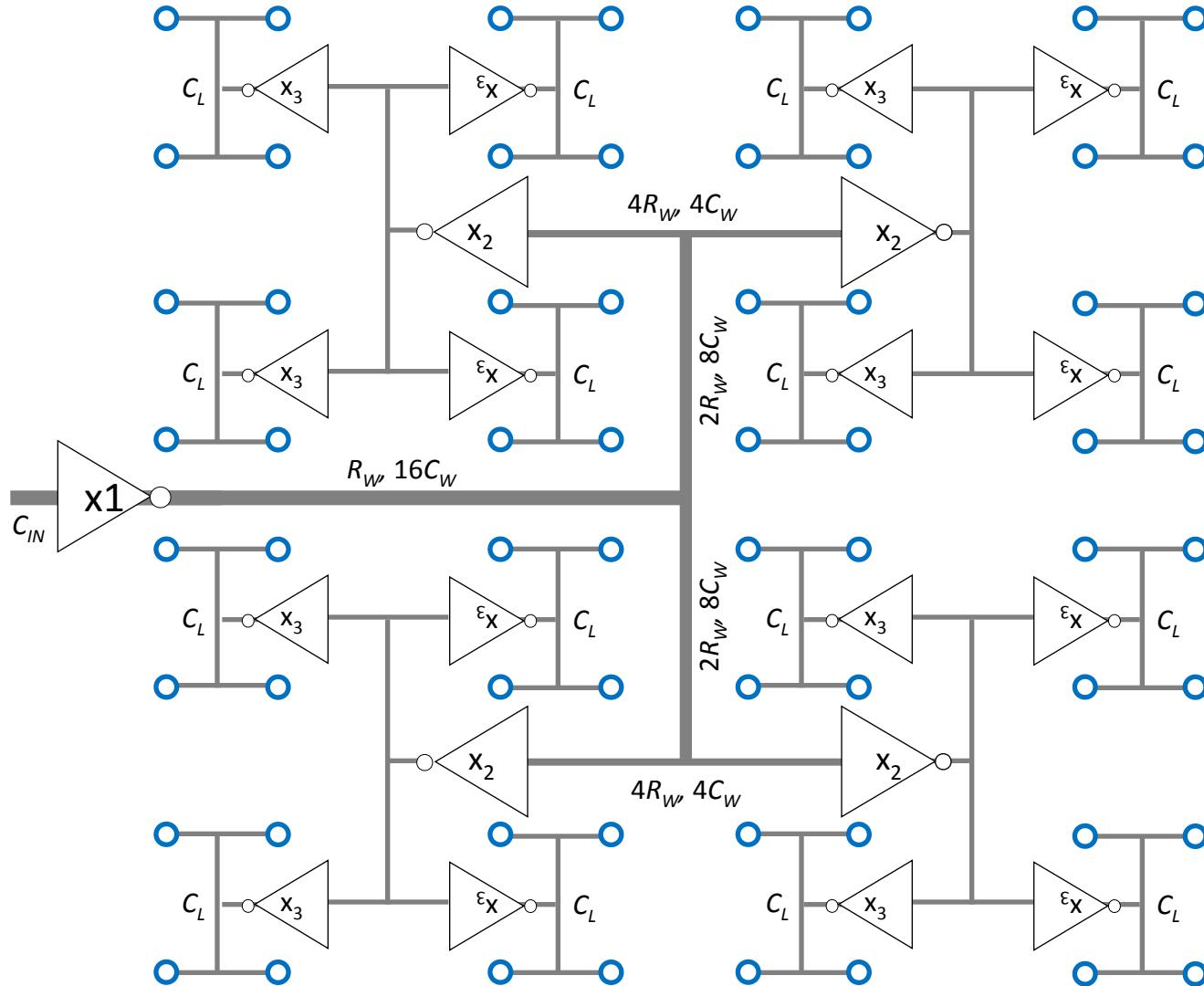

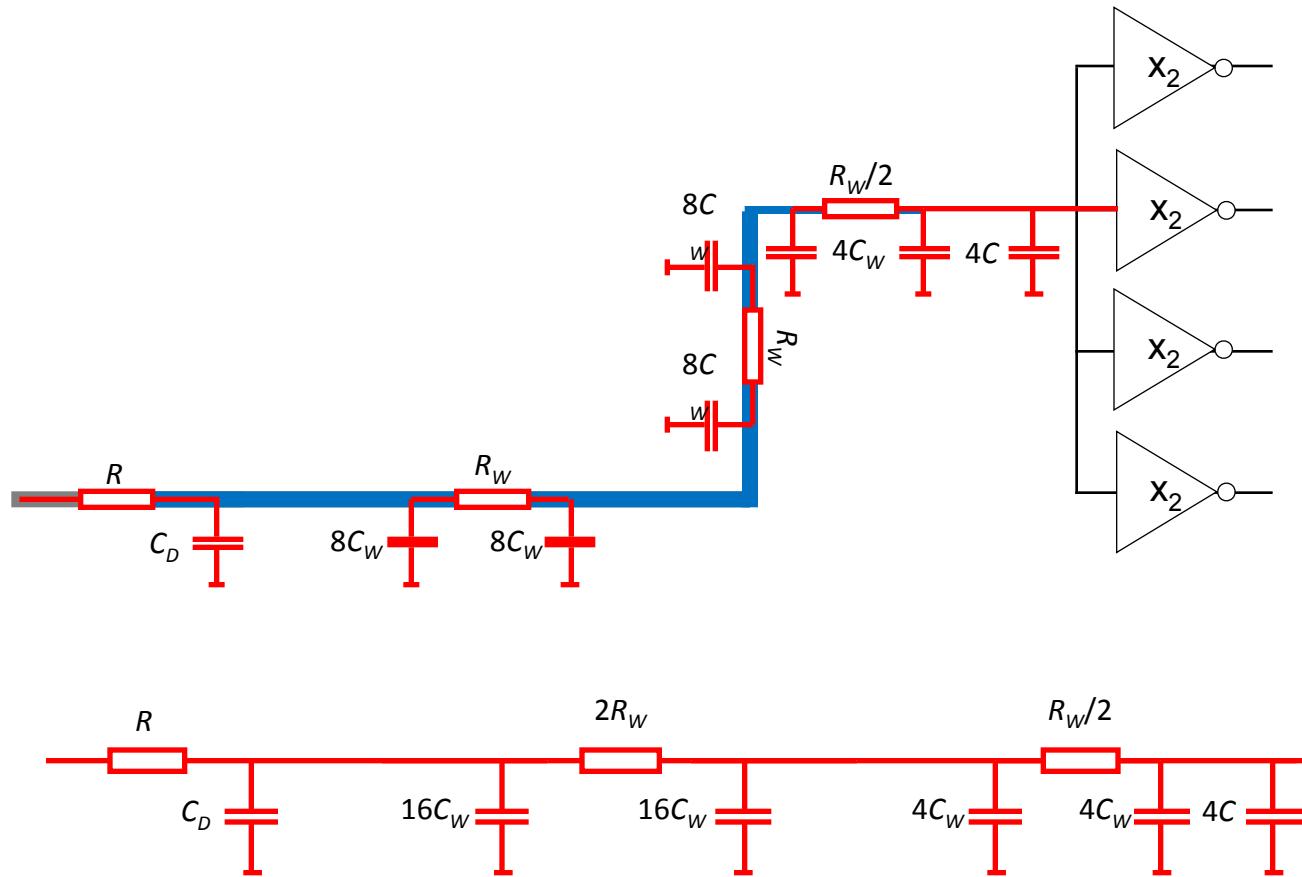

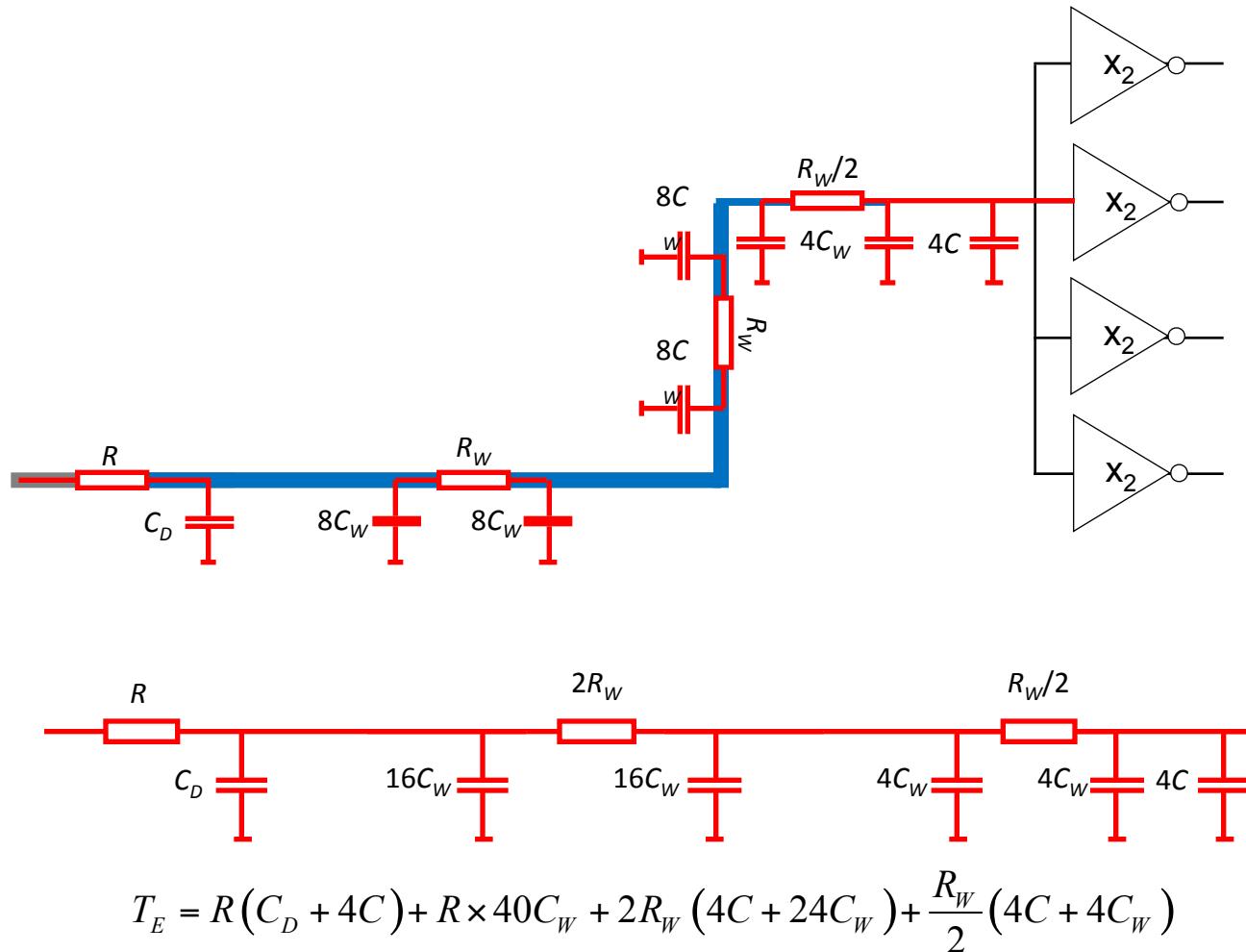

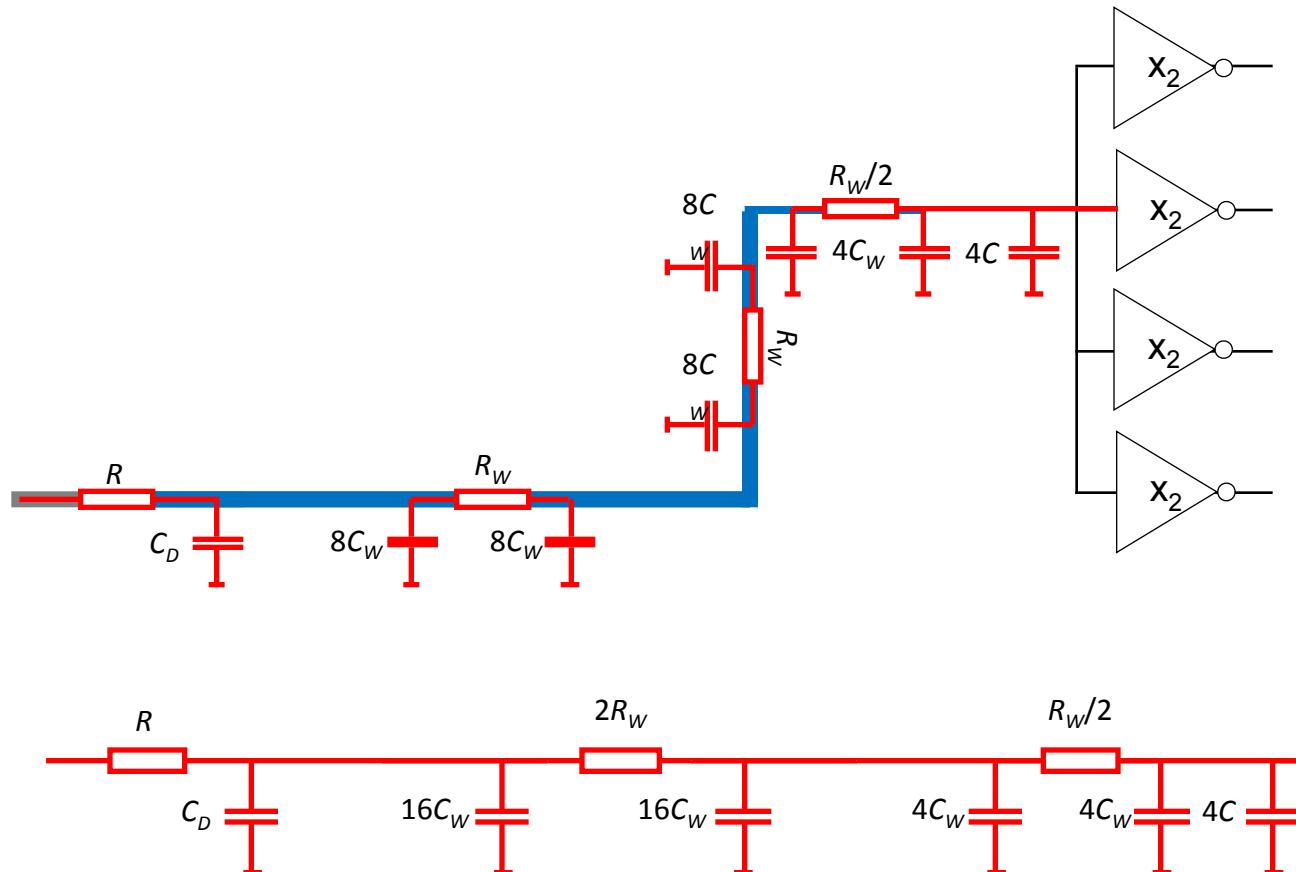

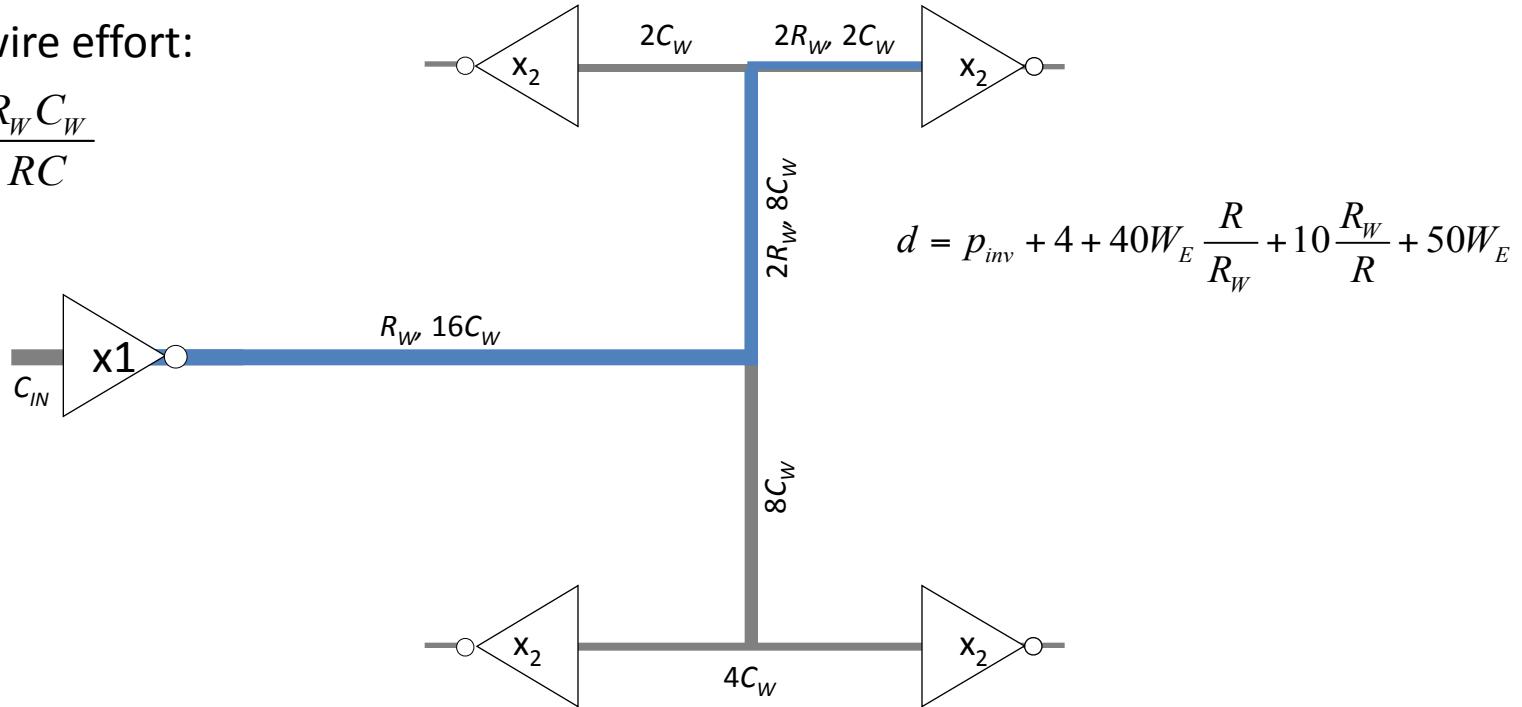

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

$$T_E = R(C_D + 4C) + R \times 40C_W + 2R_W(4C + 24C_W) + \frac{R_W}{2}(4C + 4C_W)$$

$$T_E = R(C_D + 4C) + 40RC_W + 10R_WC + 50R_WC_W$$

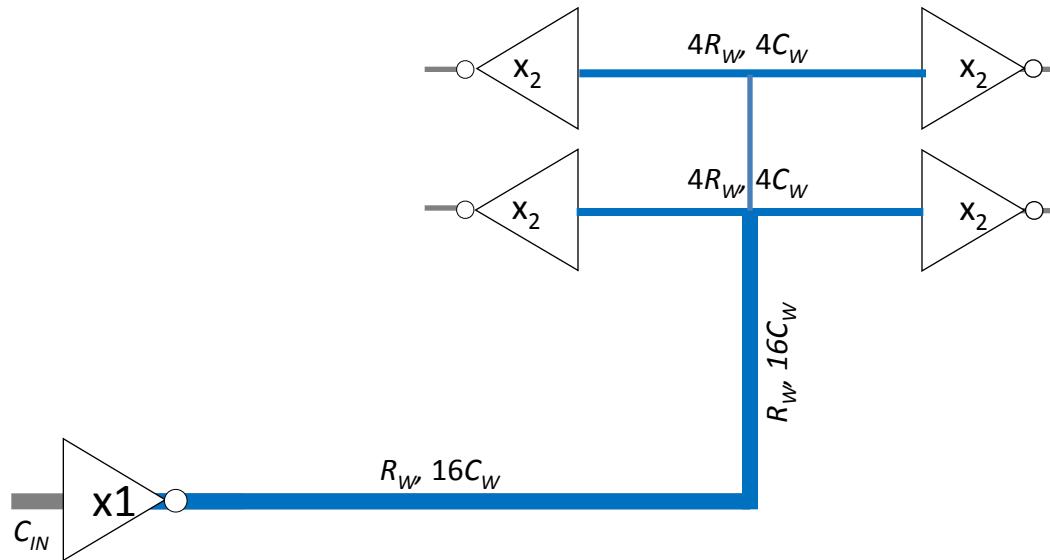

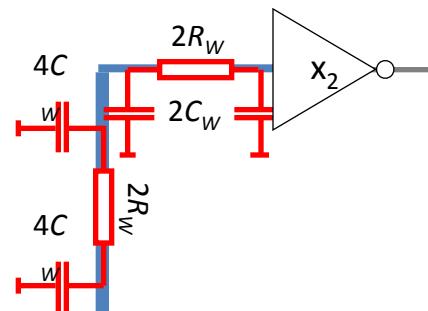

# H-tree clock distribution

# H-tree clock distribution

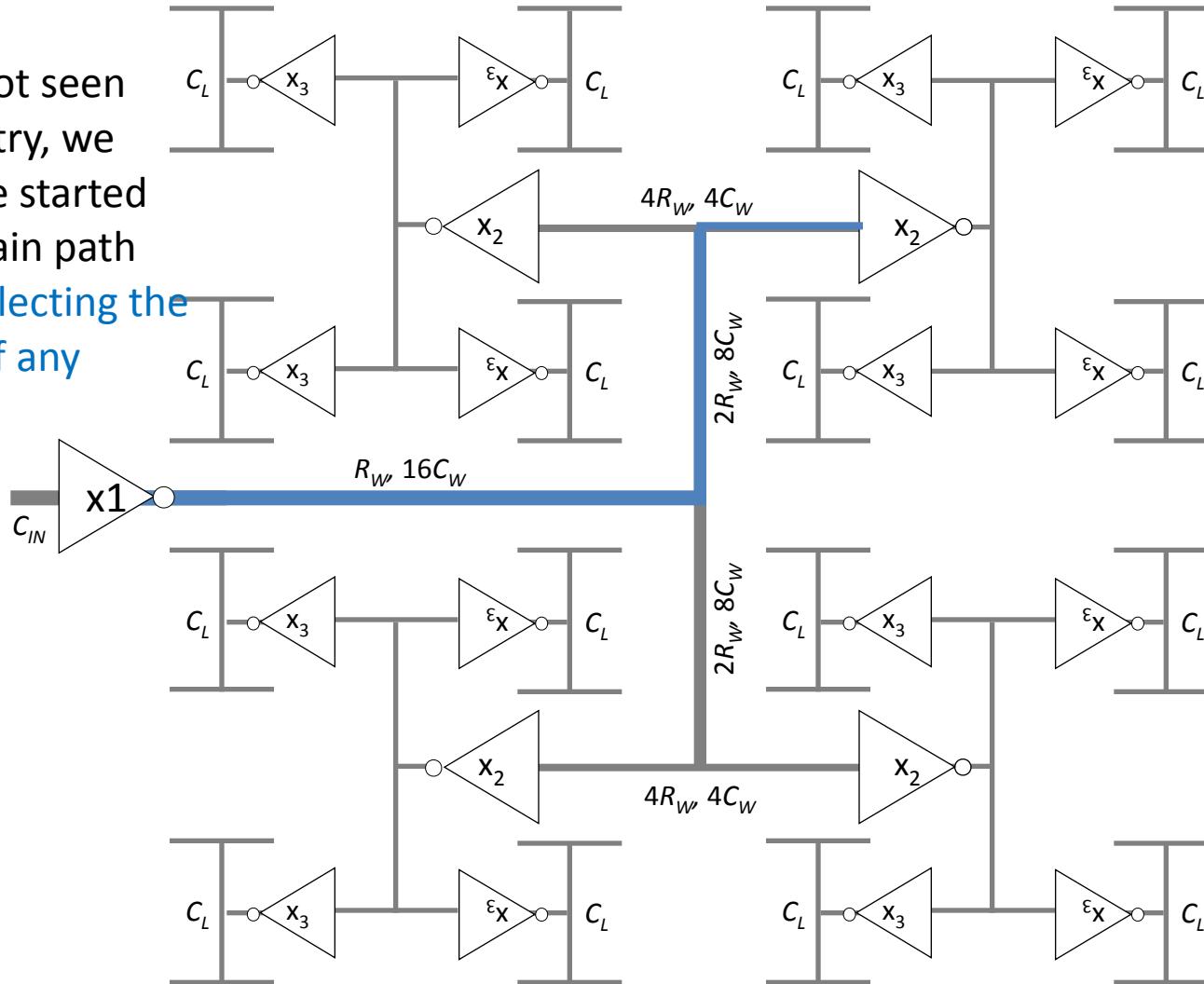

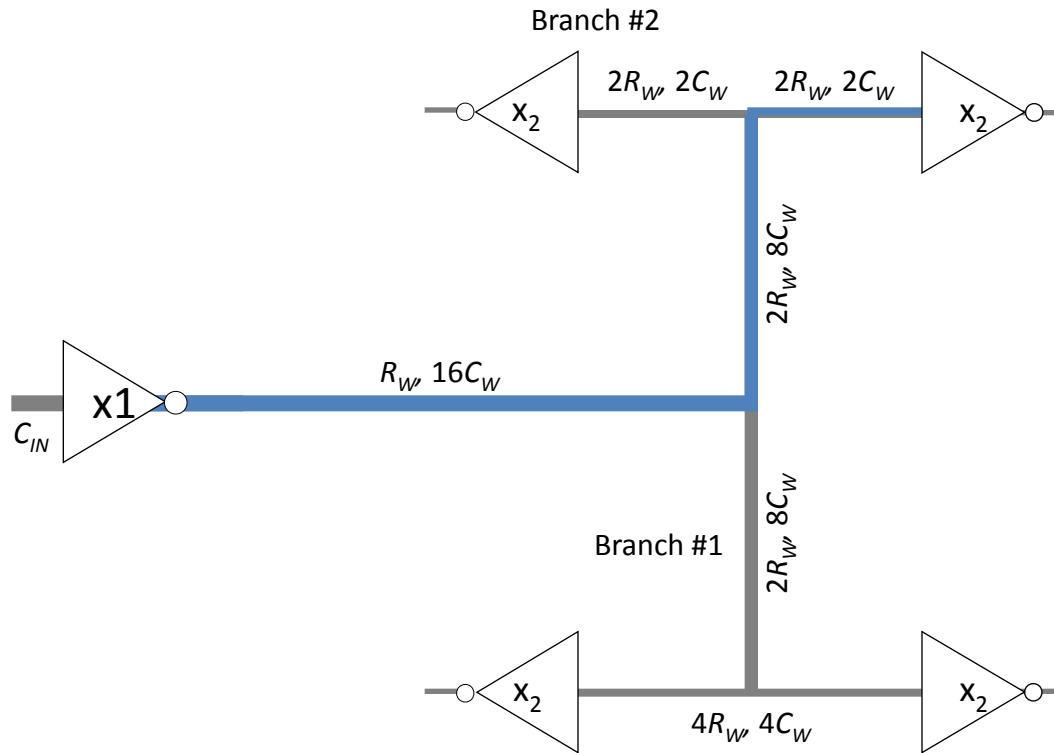

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – **neglecting the influence of any branches**

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

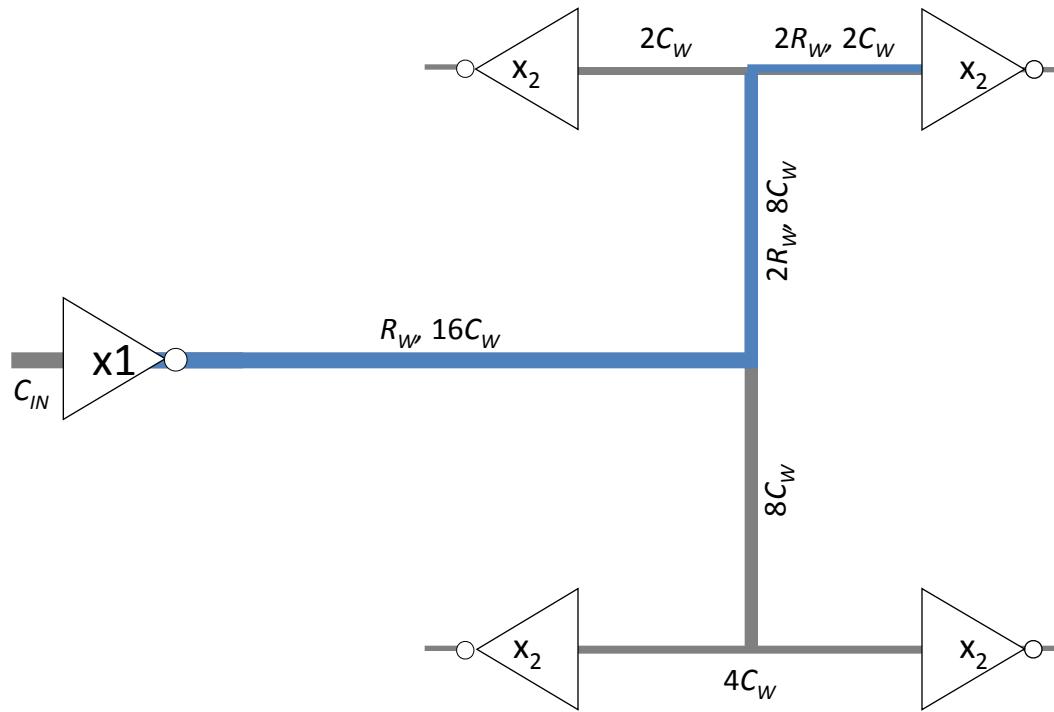

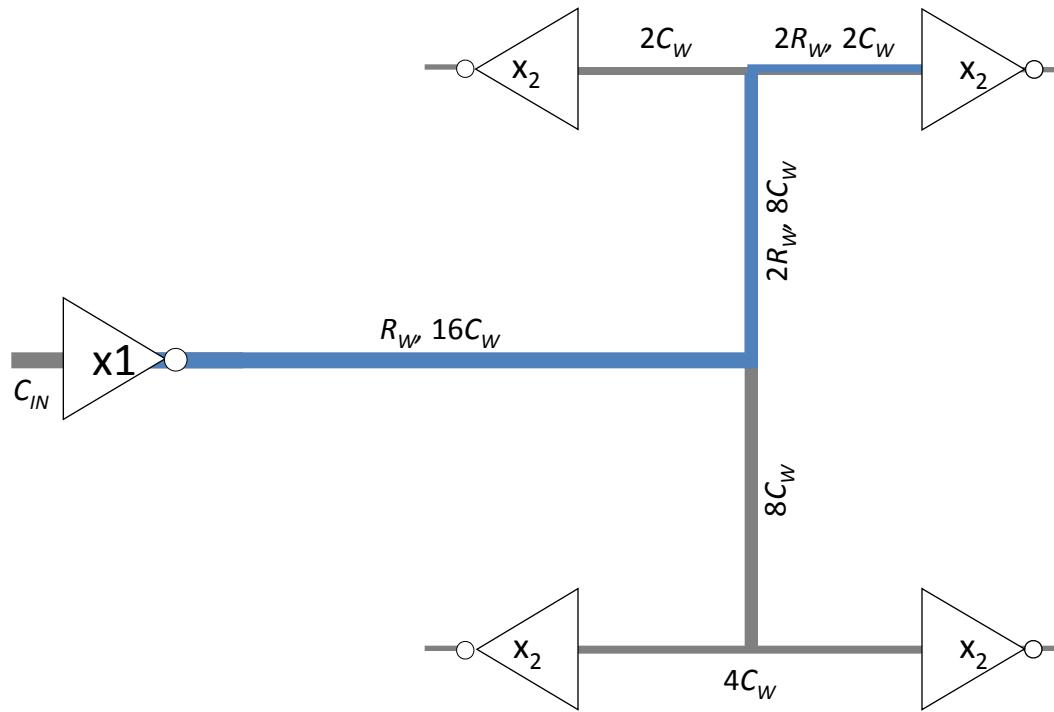

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – **neglecting the influence of any branches**

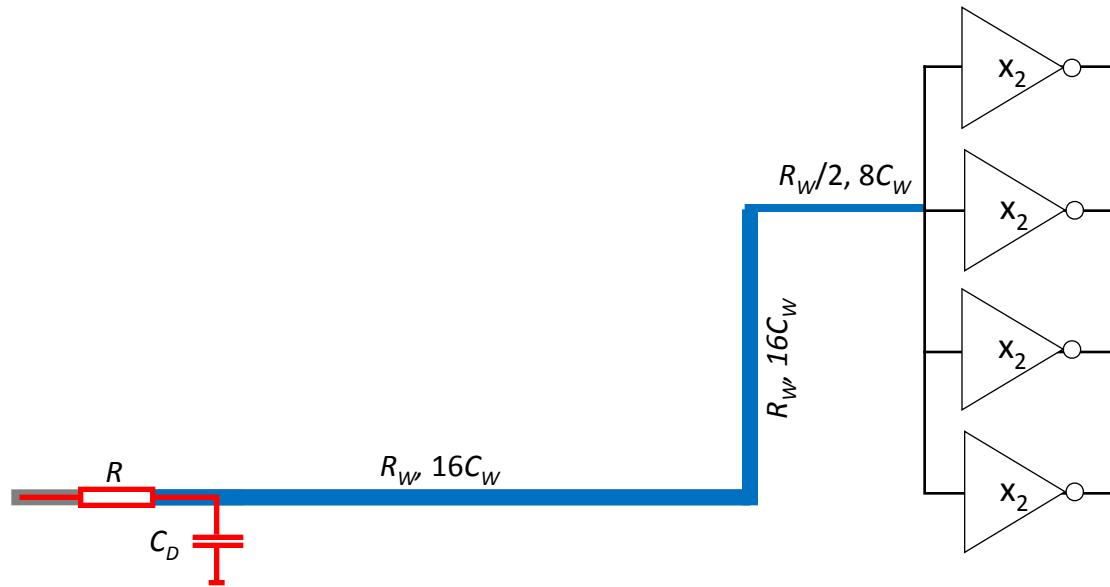

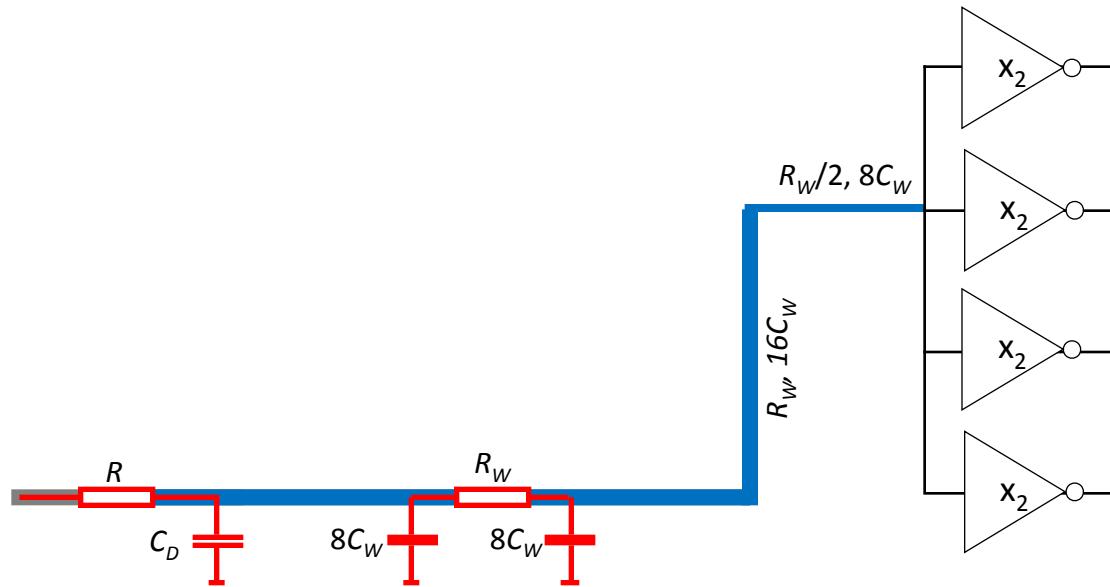

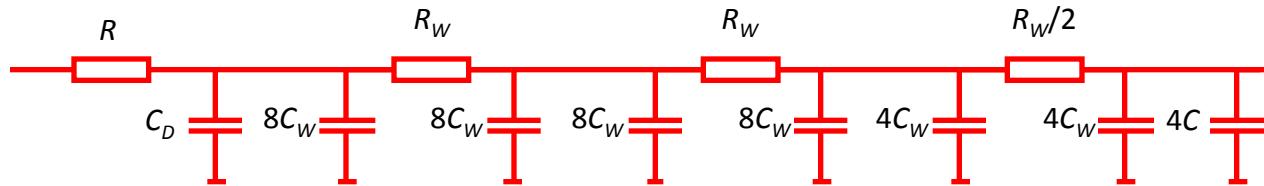

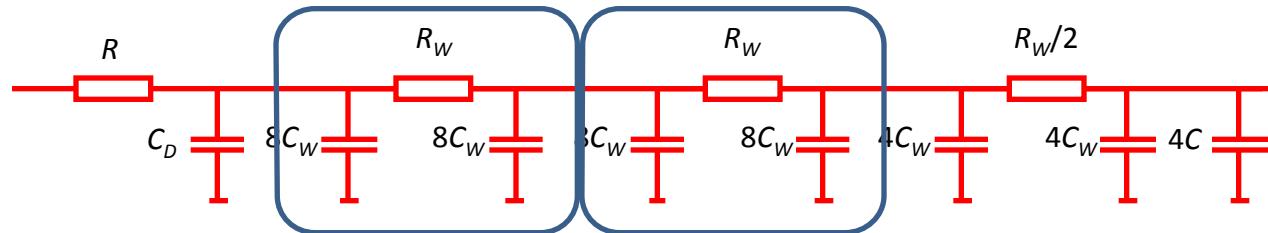

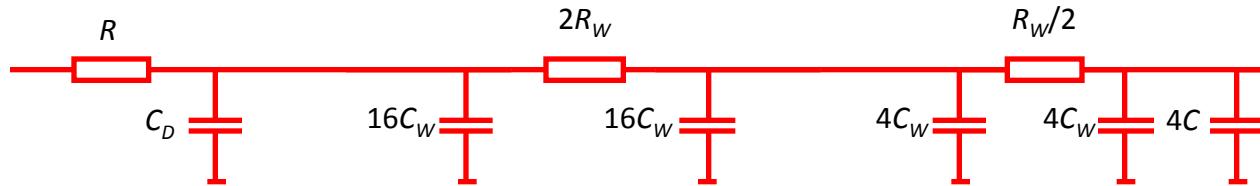

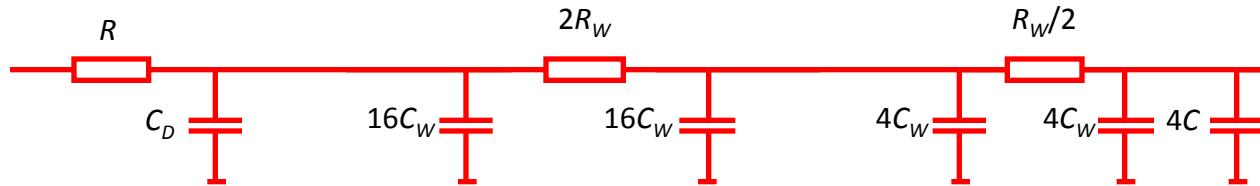

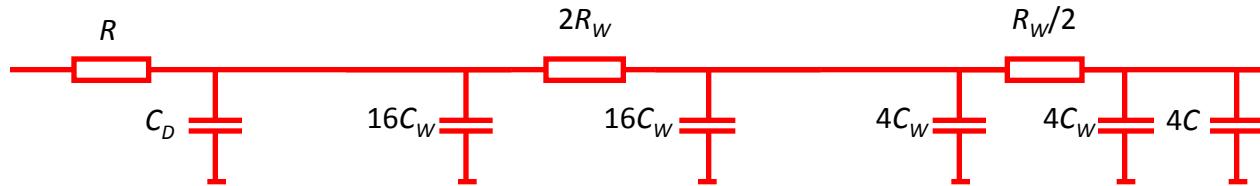

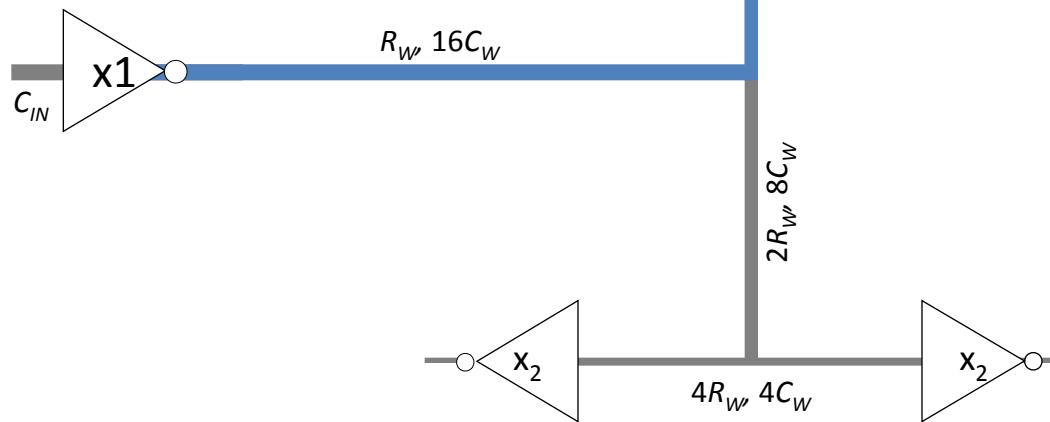

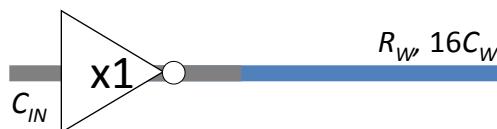

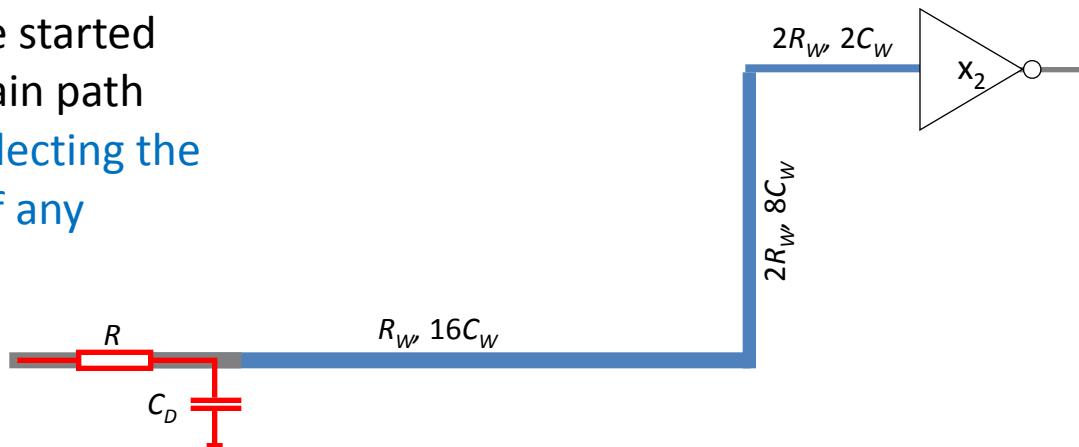

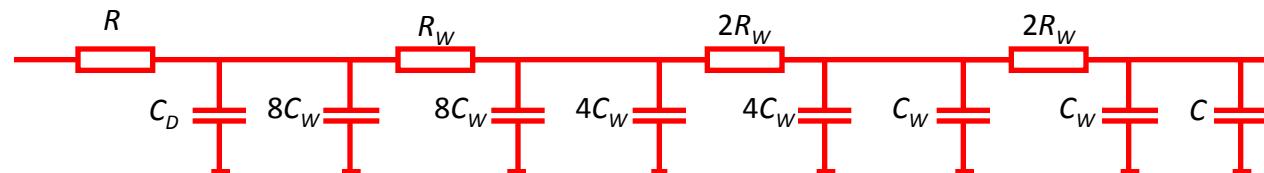

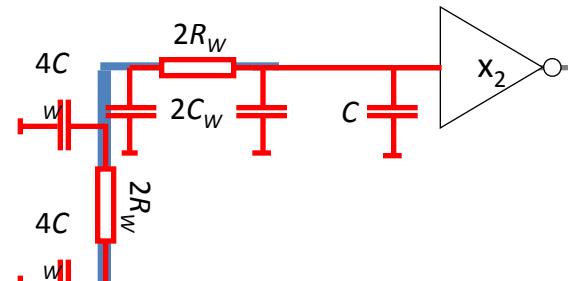

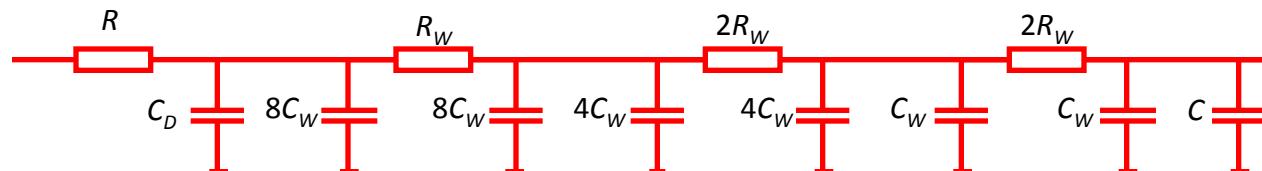

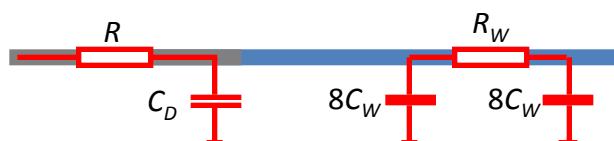

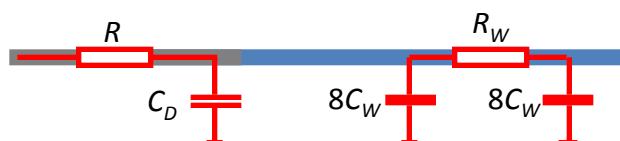

Electrical RC wire model (neglecting branches)

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – **neglecting the influence of any branches**

Electrical RC wire model (neglecting branches)

Obtain Elmore time constant

(by multiplying each resistance by

all downstream capacitances)

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – **neglecting the influence of any branches**

Electrical RC wire model (neglecting branches)

Obtain Elmore time constant

(by multiplying each resistance by

all downstream capacitances)

$$T_{E,main} = R(C_D + C) + R \times 26C_W + R_W(C + 18C_W) + 2R_W(C + 6C_W) + 2R_W(C + C_W)$$

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – **neglecting the influence of any branches**

Electrical RC wire model (neglecting branches)

Obtain Elmore time constant

(by multiplying each resistance by

all downstream capacitances)

$$T_{E,main} = R(C_D + C) + R \times 26C_W + R_W(C + 18C_W) + 2R_W(C + 6C_W) + 2R_W(C + C_W)$$

$$T_{E,main} = R(C_D + C) + 26RC_W + 5R_WC + 32R_WC_W$$

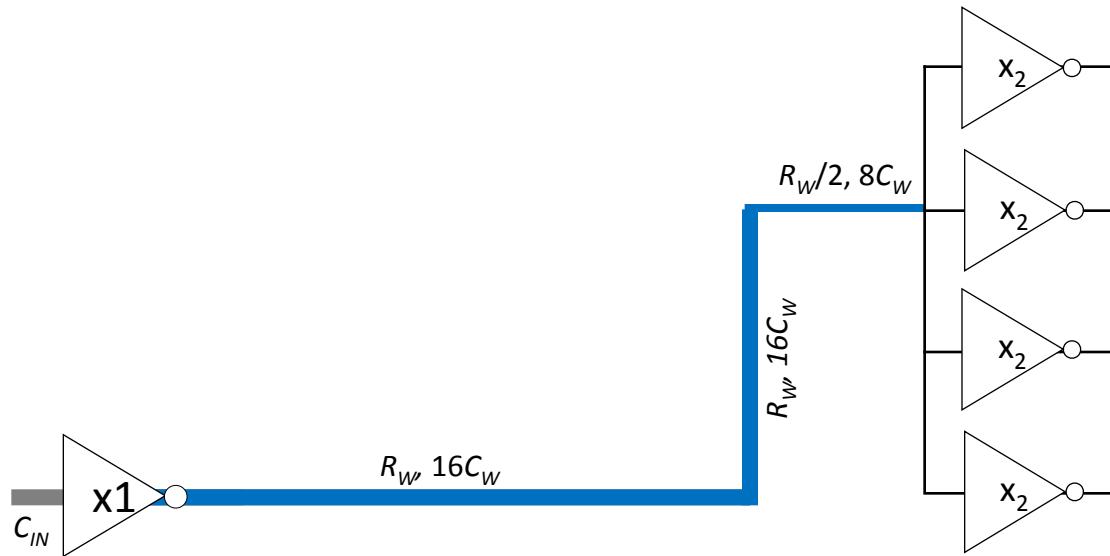

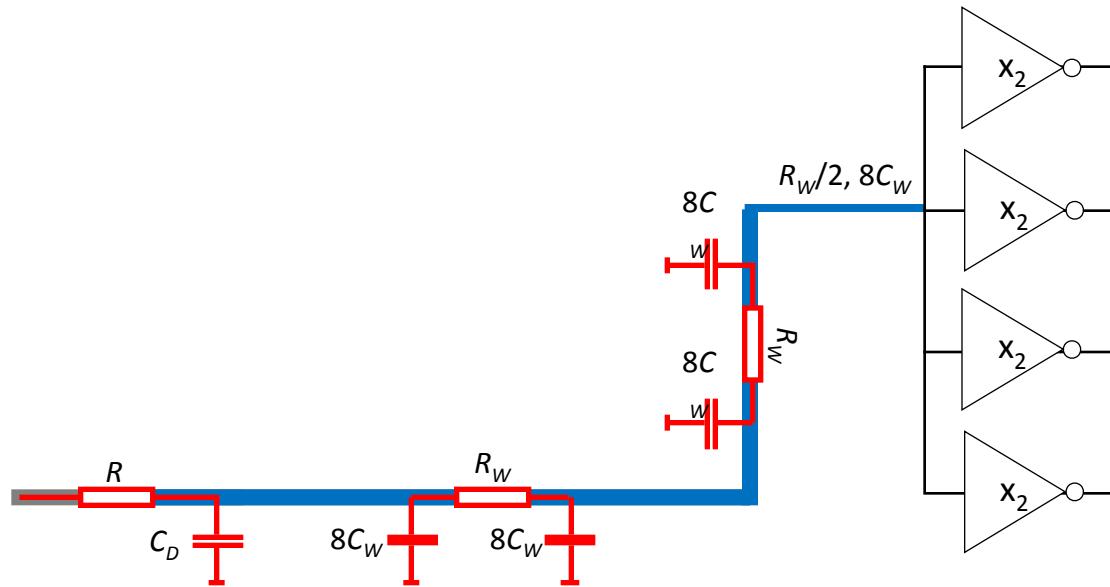

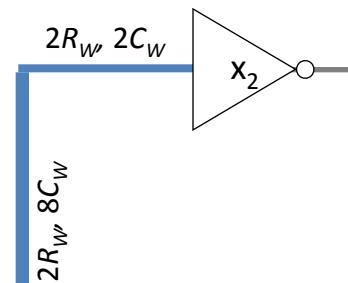

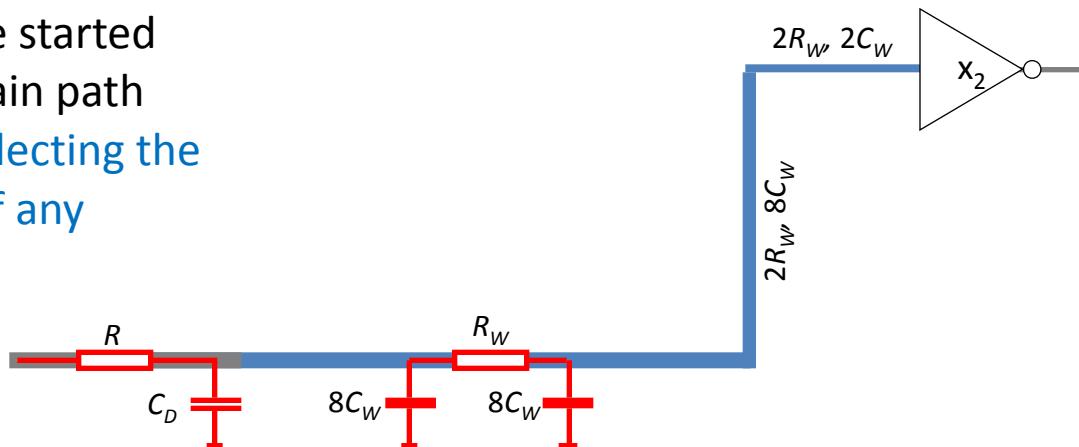

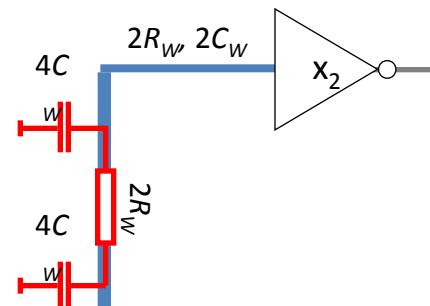

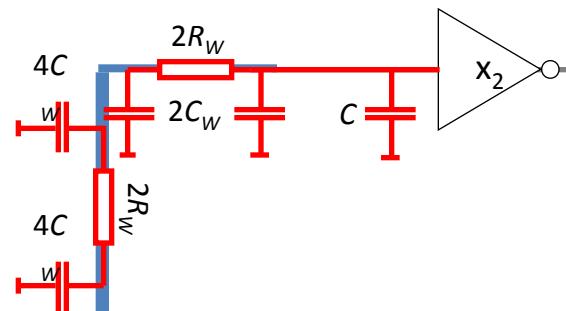

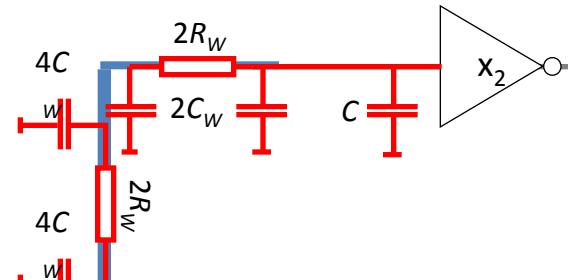

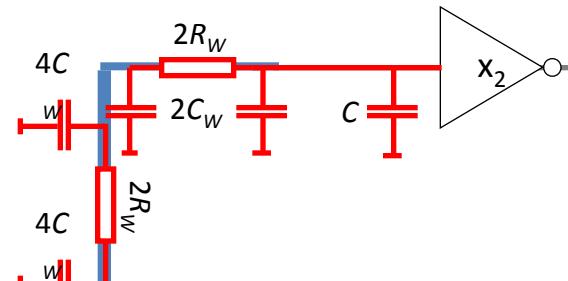

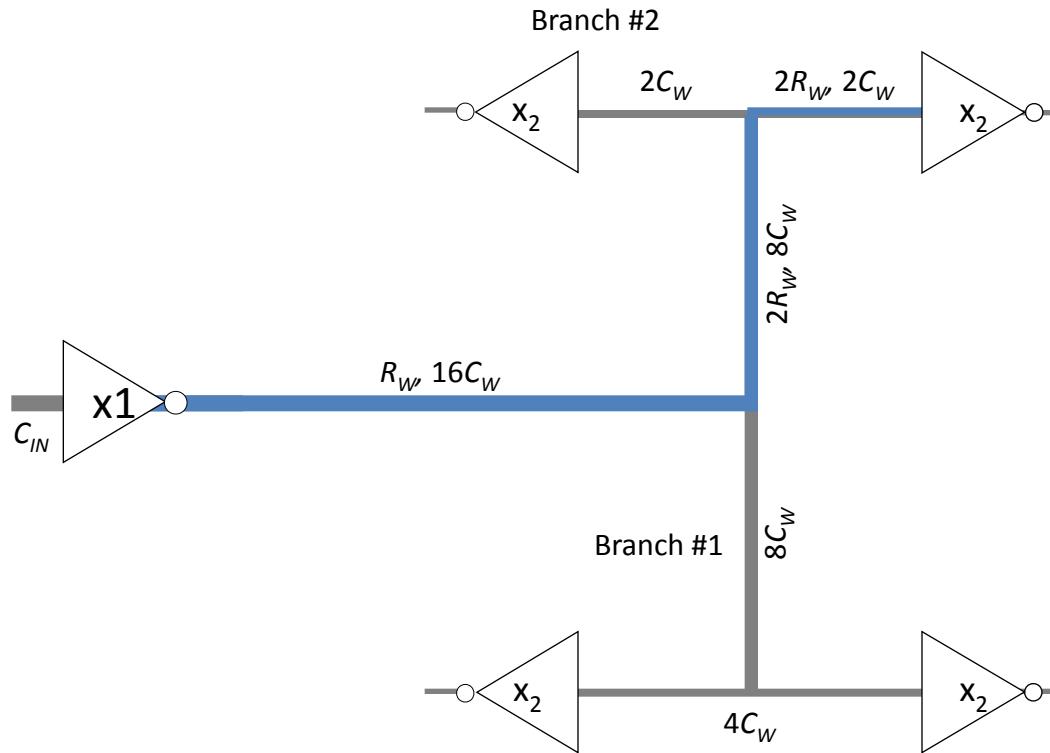

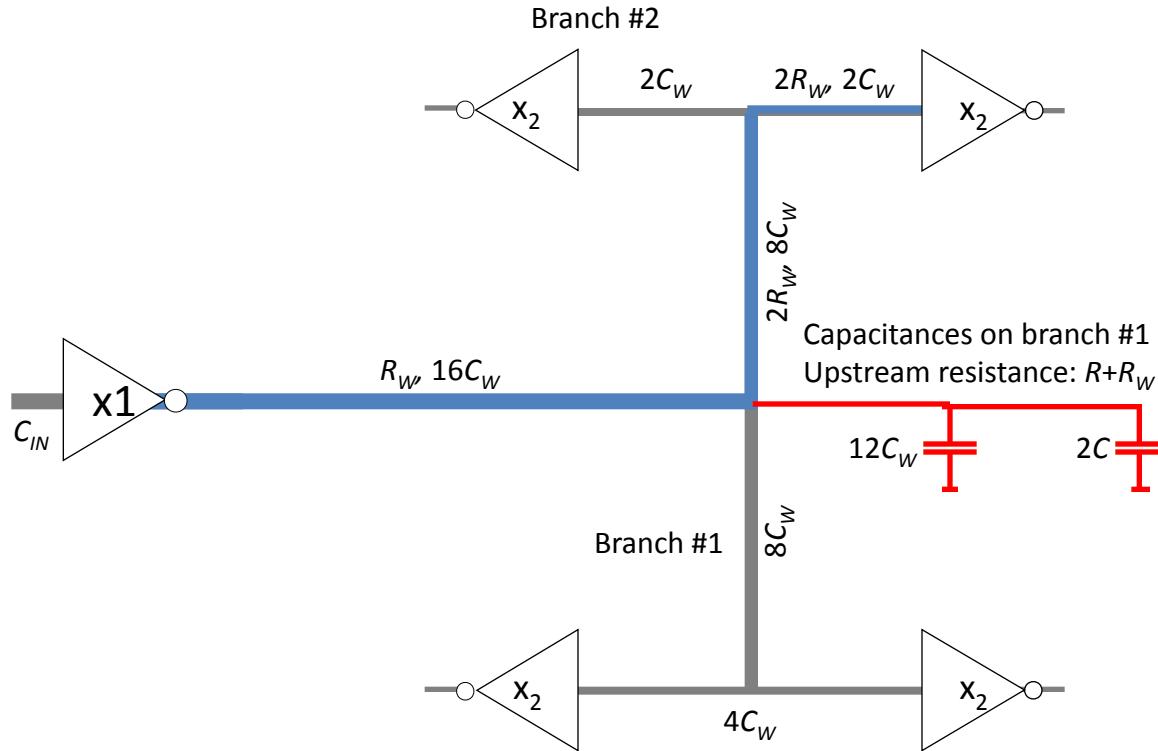

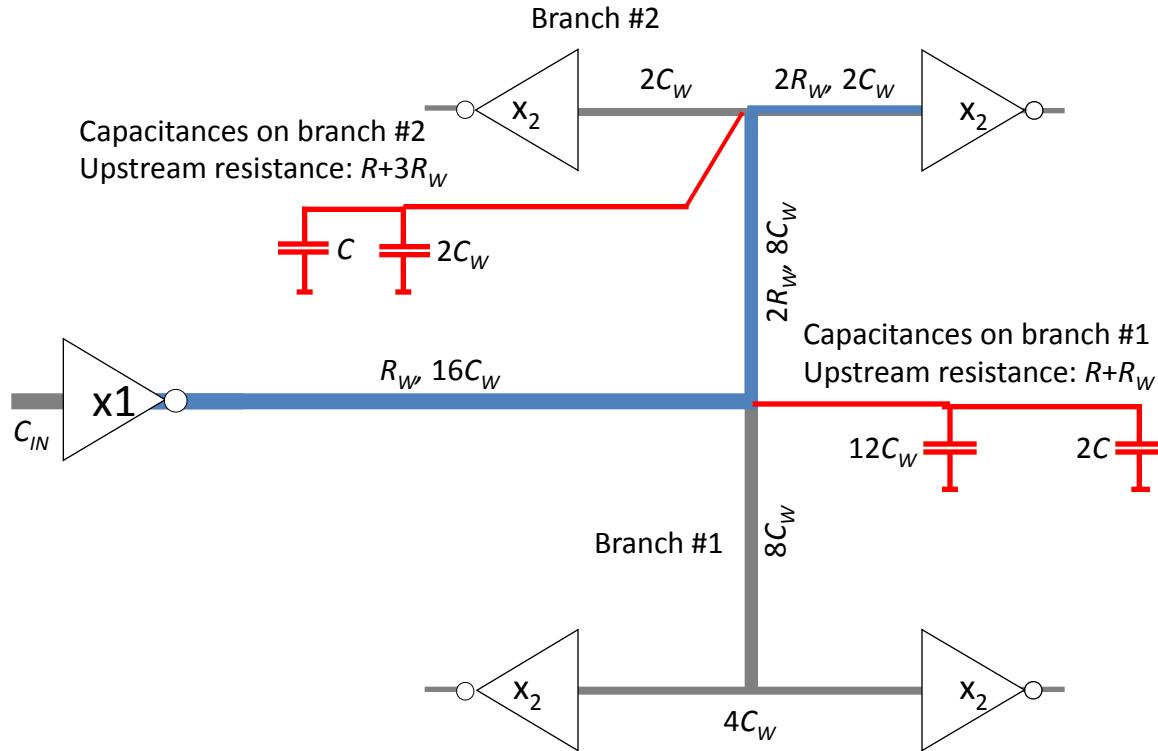

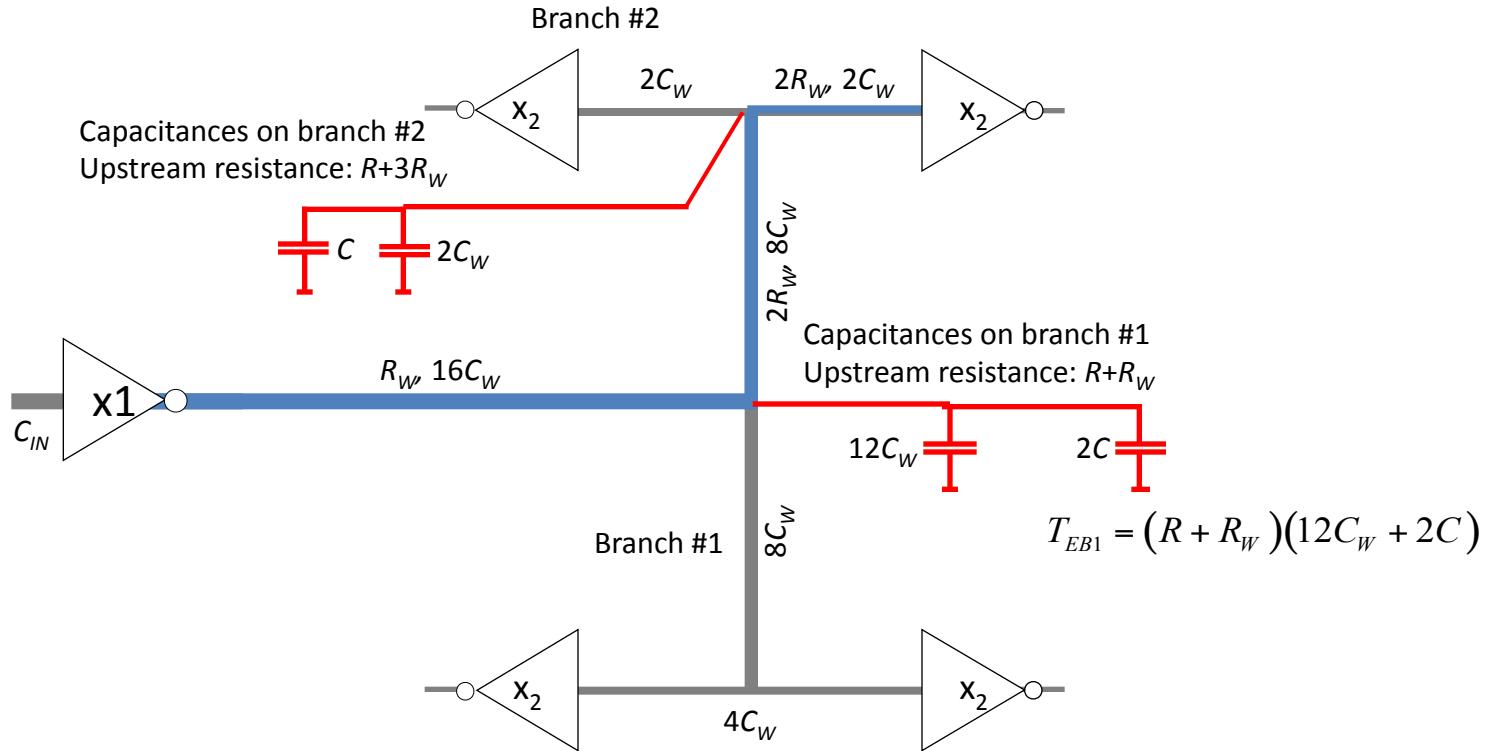

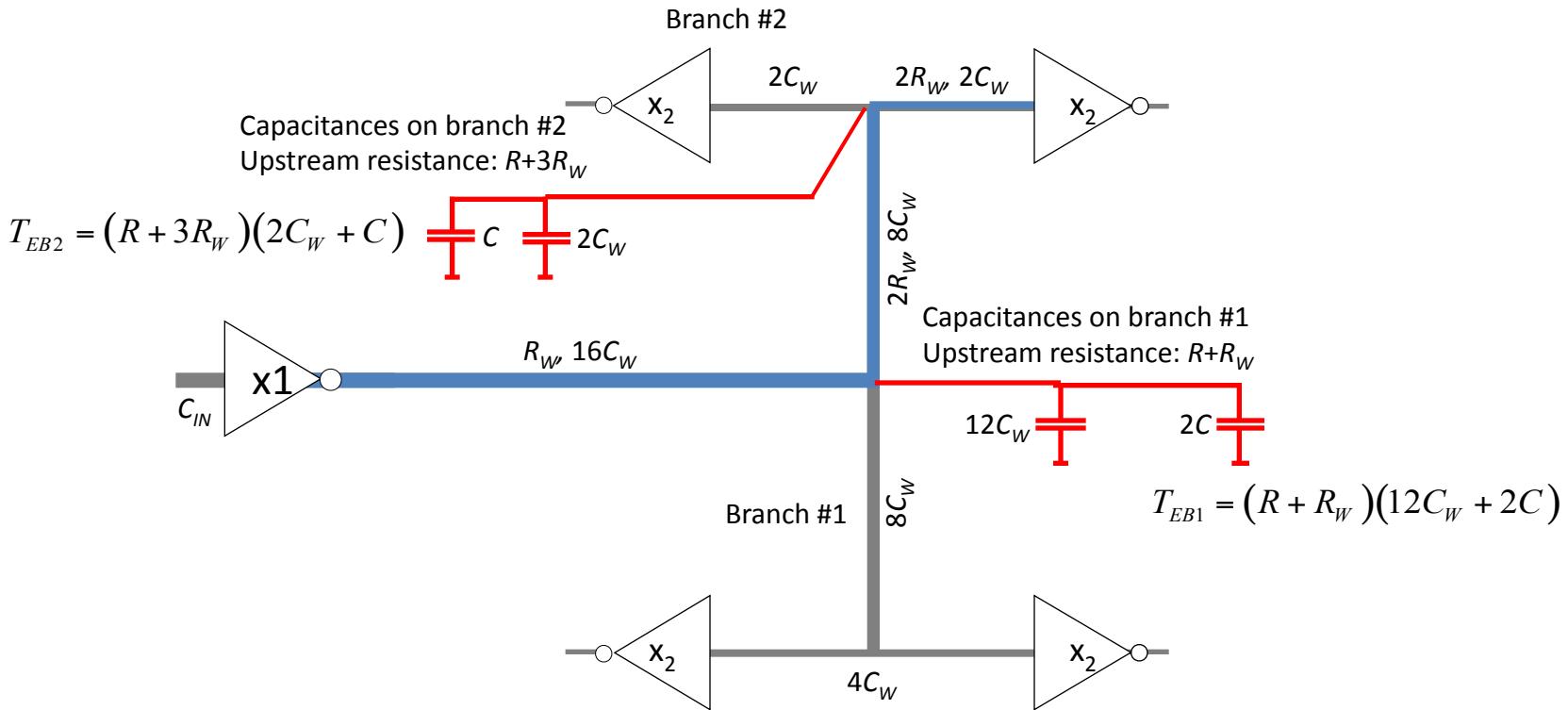

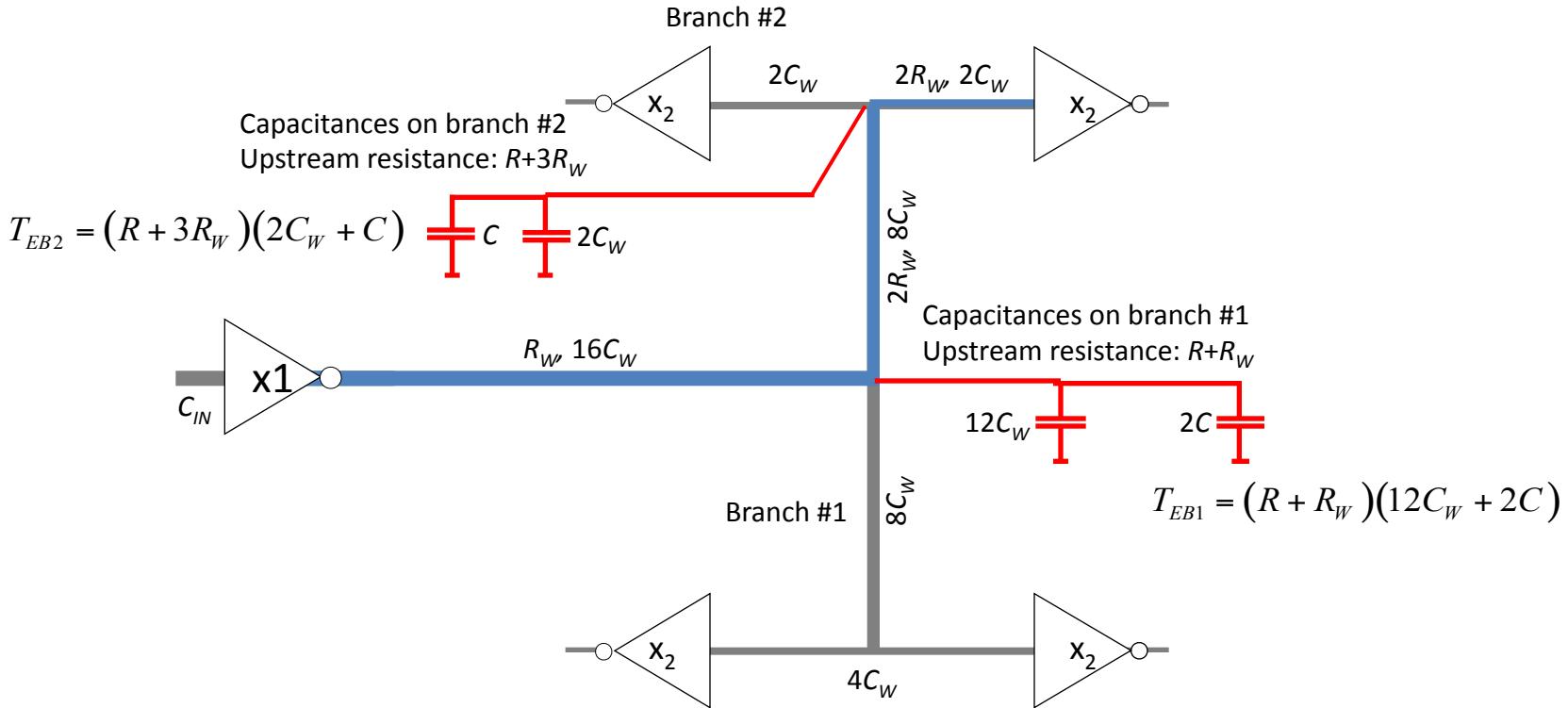

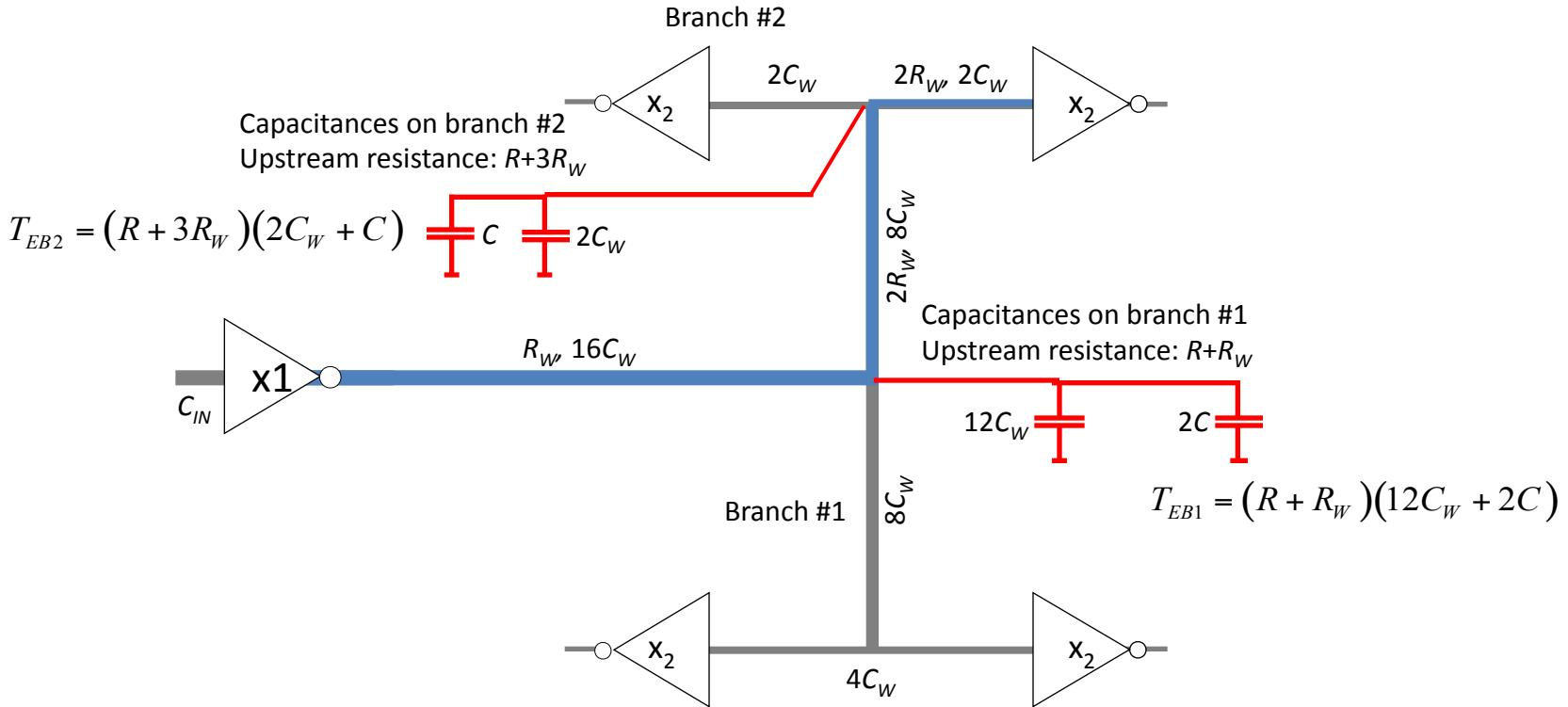

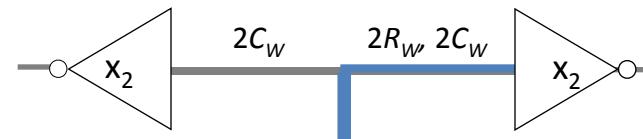

# Then consider neglected branches

# Then consider neglected branches

We have two neglected branches: #1 and #2

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

Branch contribution to Elmore time constant:  $T_{E,branches} = 3RC + 14RC_W + 5R_WC + 18R_WC_W$

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

Branch contribution to Elmore time constant:  $T_{E,branches} = 3RC + 14RC_W + 5R_WC + 18R_WC_W$

Total Elmore time constant:  $T_E = R(C_D + 4C) + 40RC_W + 10R_WC + 50R_WC_W$

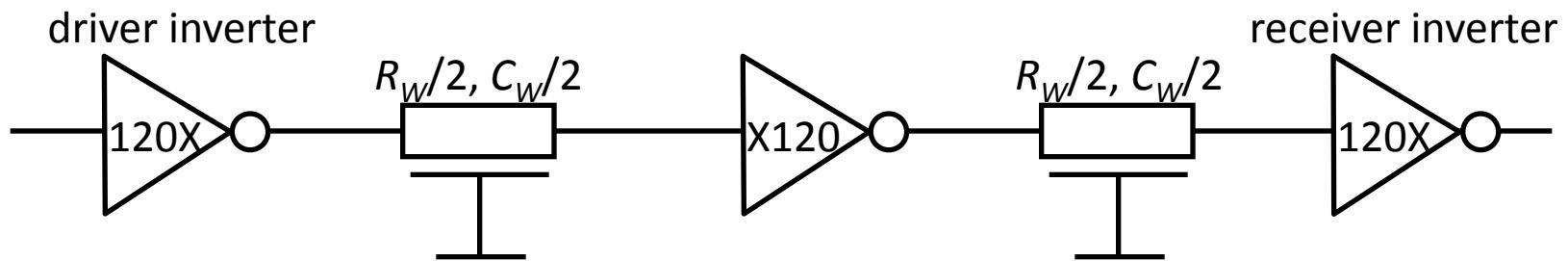

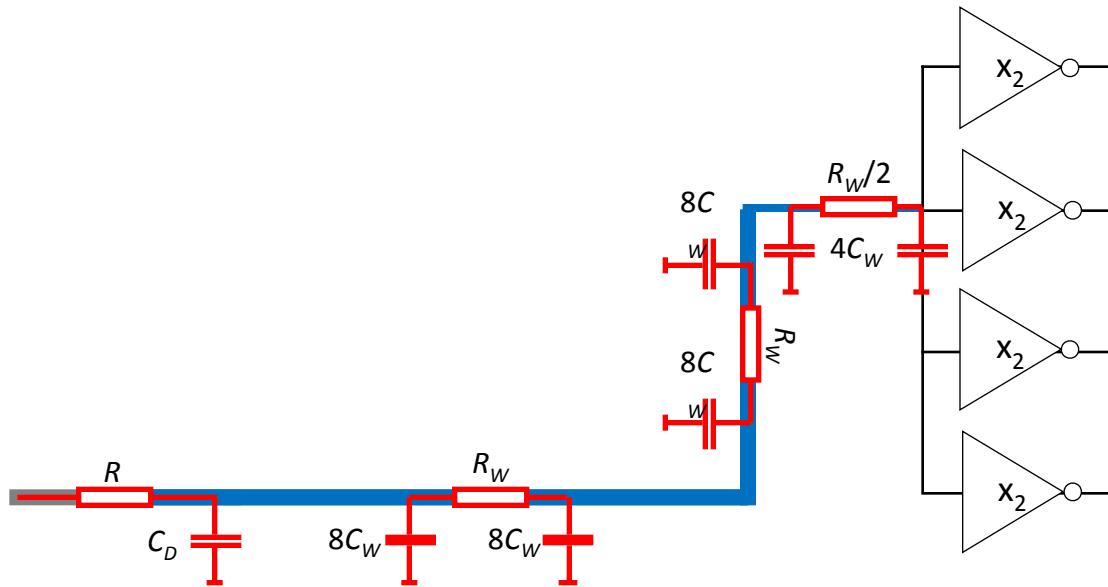

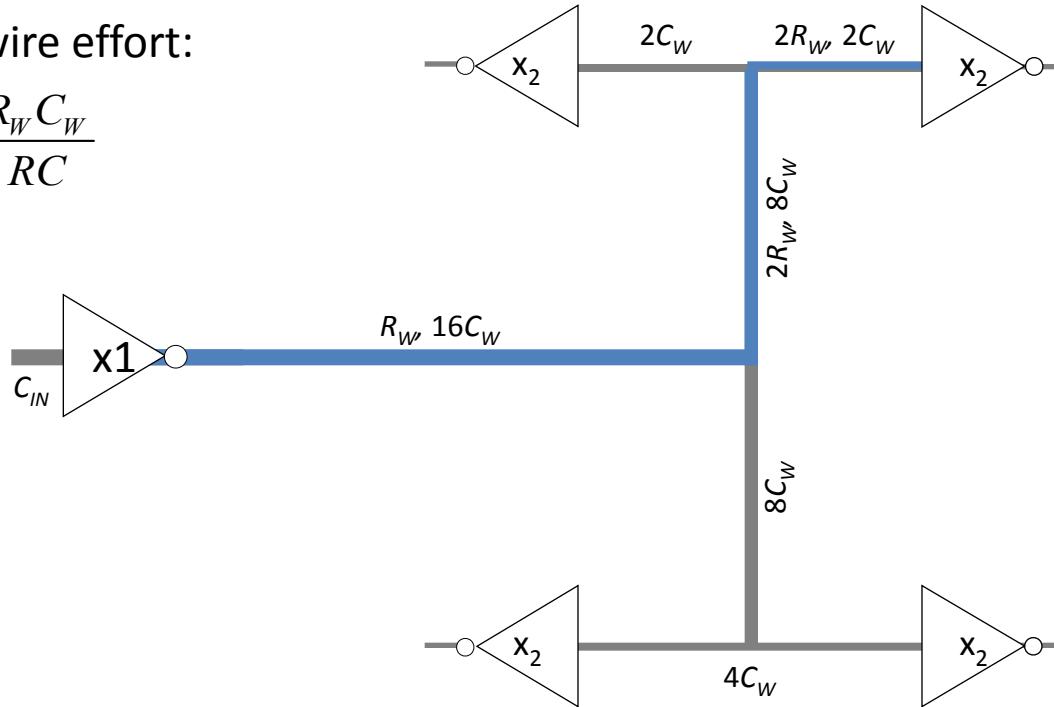

# Inverter sizing

How to size driver inverter to minimize the time constant, and hence the wire delay?

$$\text{Total Elmore time constant: } T_E = R(C_D + 4C) + 40RC_W + 10R_WC + 50R_WC_W$$

# Inverter sizing

How to size driver inverter to minimize the time constant, and hence the wire delay?

Normalize Elmore time constant:  $d = \frac{T_E}{RC} = p_{inv} + 4 + 40 \frac{R_W C_W}{RC} \frac{R}{R_W} + 10 \frac{R_W}{R} + 50 \frac{R_W C_W}{RC}$

Total Elmore time constant:  $T_E = R(C_D + 4C) + 40RC_W + 10R_W C + 50R_W C_W$

# Inverter sizing

How to size driver inverter to minimize the time constant, and hence the wire delay?

Normalize Elmore time constant:  $d = \frac{T_E}{RC} = p_{inv} + 4 + 40 \frac{R_W C_W}{RC} \frac{R}{R_W} + 10 \frac{R_W}{R} + 50 \frac{R_W C_W}{RC}$

Define wire effort:

$$W_E = \frac{R_W C_W}{RC}$$

$$\text{Total Elmore time constant: } T_E = R(C_D + 4C) + 40RC_W + 10R_W C + 50R_W C_W$$

# Inverter sizing

How to size driver inverter to minimize the time constant, and hence the wire delay?

Normalize Elmore time constant:  $d = \frac{T_E}{RC} = p_{inv} + 4 + 40 \frac{R_W C_W}{RC} \frac{R}{R_W} + 10 \frac{R_W}{R} + 50 \frac{R_W C_W}{RC}$

Define wire effort:

$$W_E = \frac{R_W C_W}{RC}$$

Total Elmore time constant:  $T_E = R(C_D + 4C) + 40RC_W + 10R_W C + 50R_W C_W$

# Inverter sizing

How to size driver inverter to minimize the time constant, and hence the wire delay?

Normalize Elmore time constant:  $d = \frac{T_E}{RC} = p_{inv} + 4 + 40 \frac{R_W C_W}{RC} \frac{R}{R_W} + 10 \frac{R_W}{R} + 50 \frac{R_W C_W}{RC}$

Define wire effort:

$$W_E = \frac{R_W C_W}{RC}$$

$$d = p_{inv} + 4 + 40W_E \frac{R}{R_W} + 10 \frac{R_W}{R} + 50W_E$$

$$d \text{ minimum when } \frac{\partial d}{\partial R} = 4 \frac{W_E}{R_W} - 1 \frac{R_W}{R^2} = 0$$

$$d_{\min} \text{ for } R = \frac{R_W}{2\sqrt{W_E}}$$

$$\text{Total Elmore time constant: } T_E = R(C_D + 4C) + 40RC_W + 10R_W C + 50R_W C_W$$

# Conclusion

We have learnt two things:

- The Elmore model – a generalized delay model

- Relying on the existence of a dominating time constant

- How to handle the influence on delay of branches

- Main timing path first, neglecting branches

- Then consider branches neglecting any branch resistances only considering branch capacitances!

# Thanks a lot for listening!