## MCC092 Exercises 2018

*Lena Peterson and Kjell Jeppson*

Preliminary version

is being updated during course

Revised 0 times so far.

# Contents

|                   |                                                     |           |

|-------------------|-----------------------------------------------------|-----------|

| <b>1</b>          | <b>Introduction</b>                                 | <b>5</b>  |

| <b>2</b>          | <b>Background material</b>                          | <b>7</b>  |

| 2.1               | Logic . . . . .                                     | 7         |

| 2.2               | Capacitance and charge . . . . .                    | 7         |

| 2.3               | Power and energy . . . . .                          | 7         |

| <b>3</b>          | <b>Logic functions, static CMOS gates, ILAs</b>     | <b>9</b>  |

| 3.1               | Realizing logical functions . . . . .               | 9         |

| 3.2               | Iterative logic arrays . . . . .                    | 10        |

| <b>4</b>          | <b>The MOS transistor</b>                           | <b>11</b> |

| <b>5</b>          | <b>The CMOS inverter</b>                            | <b>13</b> |

| 5.1               | Static characteristics . . . . .                    | 13        |

| 5.2               | Dynamic characteristics . . . . .                   | 15        |

| 5.3               | Tapered buffers etc. . . . .                        | 17        |

| <b>6</b>          | <b>Delay for complex gates and paths</b>            | <b>19</b> |

| 6.1               | Gate delay . . . . .                                | 19        |

| 6.2               | Path delay . . . . .                                | 19        |

| <b>7</b>          | <b>Wire delay</b>                                   | <b>23</b> |

| <b>8</b>          | <b>Layout</b>                                       | <b>27</b> |

| <b>9</b>          | <b>Sequential circuits</b>                          | <b>31</b> |

| <b>10</b>         | <b>Power, energy and scaling</b>                    | <b>35</b> |

| 10.1              | Power and energy . . . . .                          | 35        |

| 10.2              | Technology scaling and other scalings too . . . . . | 39        |

| <b>11</b>         | <b>Adders</b>                                       | <b>41</b> |

| <b>12</b>         | <b>Solutions</b>                                    | <b>43</b> |

| 12.1              | Introduction . . . . .                              | 43        |

| 12.2              | Background material . . . . .                       | 43        |

| 12.3              | Logic functions . . . . .                           | 43        |

| 12.4              | The MOS transistor . . . . .                        | 44        |

| 12.5              | The CMOS inverter . . . . .                         | 46        |

| 12.6              | Delay for complex gates and paths . . . . .         | 51        |

| 12.7              | Wire delay . . . . .                                | 55        |

| 12.8              | Layout . . . . .                                    | 61        |

| 12.9              | Sequential circuits . . . . .                       | 65        |

| 12.10             | Power, energy and scaling . . . . .                 | 67        |

| 12.11             | Adders . . . . .                                    | 73        |

| <b>Appendices</b> |                                                     |           |

**A Templates and graphs to draw on****77**

# Chapter 1

## Introduction

This is a set of exercises for the course MCC092. For the 2017 instance of the course we compiled problems previously used in exams and various sets of exercises through the years into one contained document. This document has further been updated for 2018. Still, it is not yet complete and will be updated some as we go. We have relied heavily on our old solutions from previous years. However, over the years our practice in how to express things in the course has evolved. So quite likely there are still quite a few errors, some due to this evolution and some just plain typos. We would be extremely happy if you students would report any errors you find to us. We promise to mention you in the list of contributors.

# Chapter 2

## Background material

This part is still missing, but it would be very good to have.

Here we have complied some problems on topics we expect you to have seen before. However, it may have been a long time ago so a brush-up may be good.

### 2.1 Logic

### 2.2 Capacitance and charge

### 2.3 Power and energy

# Chapter 3

## Logic functions, static CMOS gates, ILAs

### 3.1 Realizing logical functions

**Exercise 3.1:** Task tests understanding the implementation of static CMOS gates from logical expression. *Solution on page 43.*

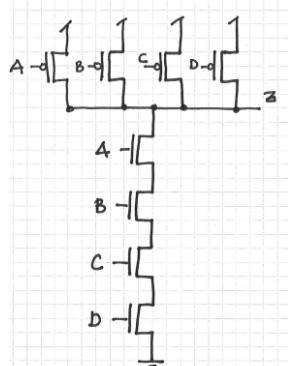

Design **static CMOS gates** realizing the following Boolean expressions:

From old book. Check the homework exercises - are any of these included there? Missing solution.

- a)  $z = \overline{A \cdot B \cdot C \cdot D}$

- b)  $z = \overline{A \cdot B \cdot C + D}$

- c)  $z = \overline{(A + B + C) \cdot D}$

- d)  $z = \overline{A \cdot B + C \cdot (A + B)}$

**Exercise 3.2:** Task tests understanding the implementation of static CMOS gates from logical expression and the difference between implementing with given gates and as compound gates. *Solution on page 43.*

From old book. Missing solution.

Realize the following Boolean expressions using:

1. NAND, NOR, and-or-invert (AOI) and/or or-and-invert (OAI) gates.

2. Compound gates (that is implement one static CMOS gate that implements the full function.)

The functions are:

- a)  $z = A'B + AB'$  (XOR)

- b)  $z = AB + A'B'$  (XNOR)

- c)  $z = (AB'C' + A'BC' + A'B'C + A'B'C')$  which corresponds to the sum function,  $SUM = A \oplus B \oplus C$ , in a binary adder.

Which Solution more efficient in terms of the number of transistors used?

**Exercise 3.3:** BONUS Task tests understanding of pass transistor logic. *Solution on page 44.*

From old book. Missing solution.

Repeat exercise 3.2 but this time using MUXes, which can easily be implemented as pass-transistor logic.

**Exercise 3.4:** Task tests understanding of transistor scaling. Exam 2016-12-22 Task 1(a). *Solution on page 44.*

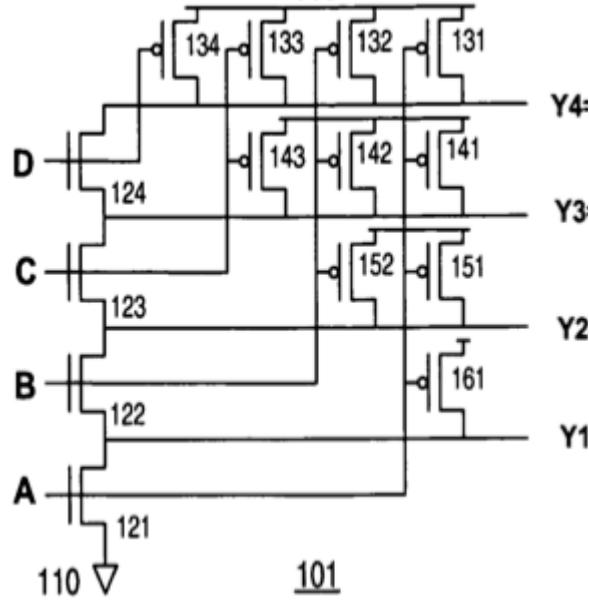

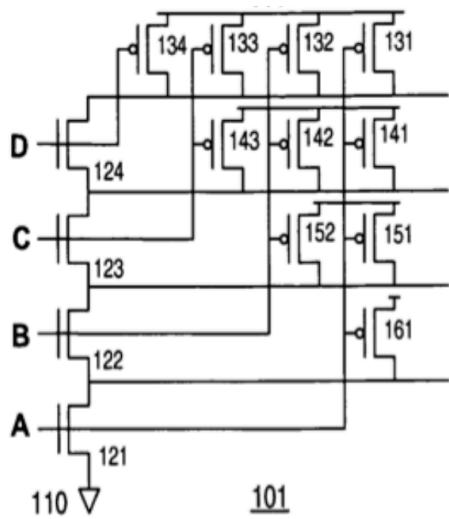

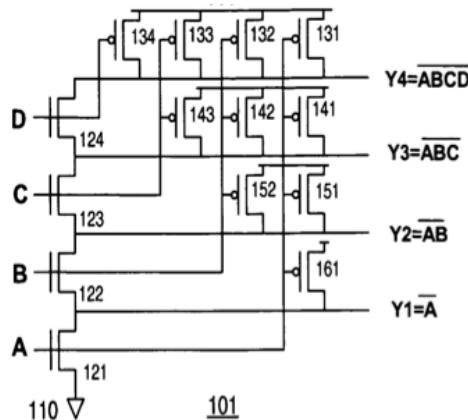

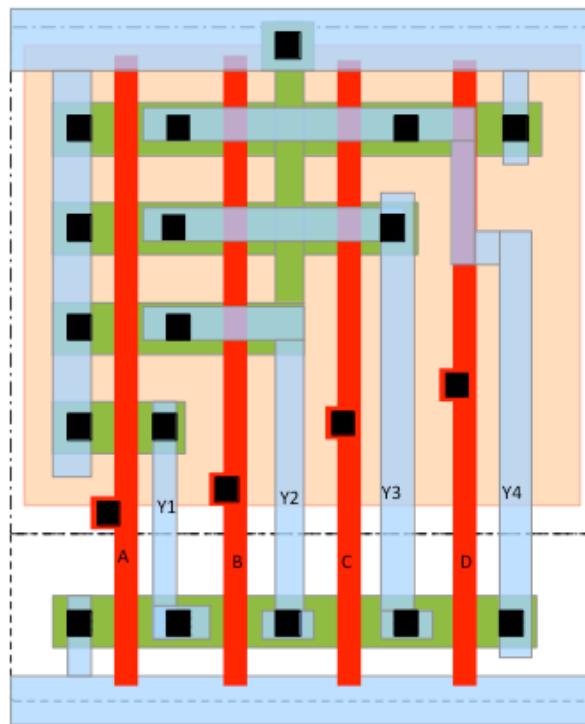

David Harris, the author of our textbook, holds quite a few patents. One of these is for static CMOS gates that have multiple outputs. The schematic for one such gate is shown in Figure 3.1, taken from the patent (but the gate in the figure is not one of the patented gates). What are the four logical functions for the four outputs Y1 through Y4 indicated in the schematic in Figure 3.1? (2 p)

Figure 3.1: A schematic of the gate with multiple outputs taken from a patent application.  $V_{DD}$  is at the top of all pMOS transistors although is not so clear from the notation. There is no contact when lines cross.

## 3.2 Iterative logic arrays

Missing problems here. Add some that is not exactly like the lab.

# Chapter 4

## The MOS transistor

**Exercise 4.1:** Task tests understanding of MOS regions of operation. *Solution on page 44.*

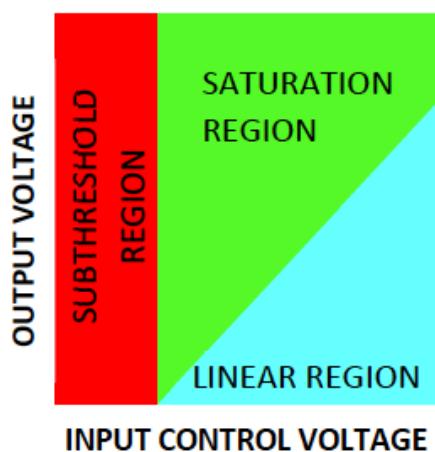

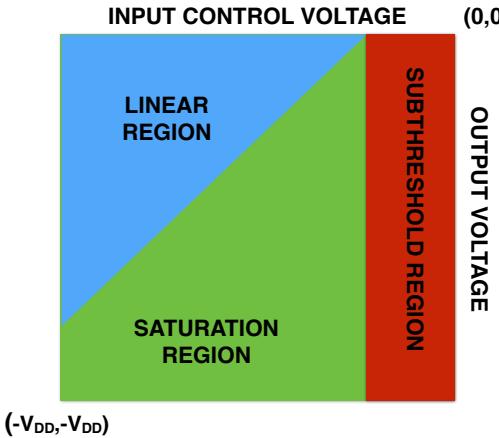

Figure 4.1: Regions of operation for a n-channel MOSFET.

- Figure 4.1 shows the regions of operation for a n-channel MOSFET. What would be the equations for the borderlines between the different regions?

- Draw a similar “regions of operation” diagram for a p-channel MOSFET.

**Exercise 4.2:** Task tests understanding of MOS model parameters. *Solution on page 45.*

The model parameters for an n-channel MOSFET,  $k_N$  and  $V_{TN}$ , in a certain MOSFET technology are given by  $k_N=900 \mu\text{A}/\text{V}^2$  and threshold voltage  $V_{TN}=0.30 \text{ V}$ .

- Calculate the gate voltage overdrive  $V_{GT}$  if the supply voltage,  $V_{DD}$ , is 1.2 V and  $V_{GS} = V_{DD}$ .

- Calculate the saturation current,  $I_{DSAT}$  when  $V_{GS} = V_{DD}$ .

- Calculate the saturation voltage,  $V_{DSAT}$ .

**Exercise 4.3:** Exercise tests understanding of MOS capacitance . *Solution on page 45.*

- Calculate the gate capacitance for a 1 mm wide MOSFET in the 65 nm CMOS process if its insulator capacitance per unit area,  $C_{ox}$ , is given as  $20 \text{ fF}/\mu\text{m}^2$ .

- b) What would be the gate capacitance of the MOSFET in task 4.4b) if the effective gate length,  $L_{\text{eff}}$ , in the process is 45 nm and  $C_{\text{ox}}$  is  $10 \text{ fF}/\mu\text{m}^2$ ?

- c) Repeat task b) for the MOSFET width in task 4.4c).

- a) Calculate the gate voltage overdrive  $V_{\text{GT}}$  if the supply voltage,  $V_{\text{DD}}$ , is 1.2 V and  $V_{\text{GS}} = V_{\text{DD}}$ .

- b) Calculate the saturation current,  $I_{\text{DSAT}}$  when  $V_{\text{GS}} = V_{\text{DD}}$ .

- c) Calculate the saturation voltage,  $V_{\text{DSAT}}$ .

**Exercise 4.4:** Exercise tests understanding of MOS effective resistance . *Solution on page 46.*

- a) Calculate the effective resistances for two MOSFETs delivering maximum currents of  $500 \mu\text{A}$  and  $750 \mu\text{A}$ , respectively, at a supply voltage of 1 V.

- b) If the effective resistance of a MOSFET in a certain technology is specified as  $2 \text{ k}\Omega \mu\text{m}$ , what would be the effective resistance of a  $5 \mu\text{m}$  wide MOSFET,

- c) What if the MOSFET in b) was 280 nm wide? What would its effective resistance be then?

# Chapter 5

## The CMOS inverter

We use the CMOS inverter as a model for all static CMOS gates. Therefore it is essential to understand the inverter in detail.

### 5.1 Static characteristics

**Exercise 5.1:** Task tests understanding of voltage transfer curves, nMOS and pMOS transistors and and inverter bias point. *Solution on page 46.*

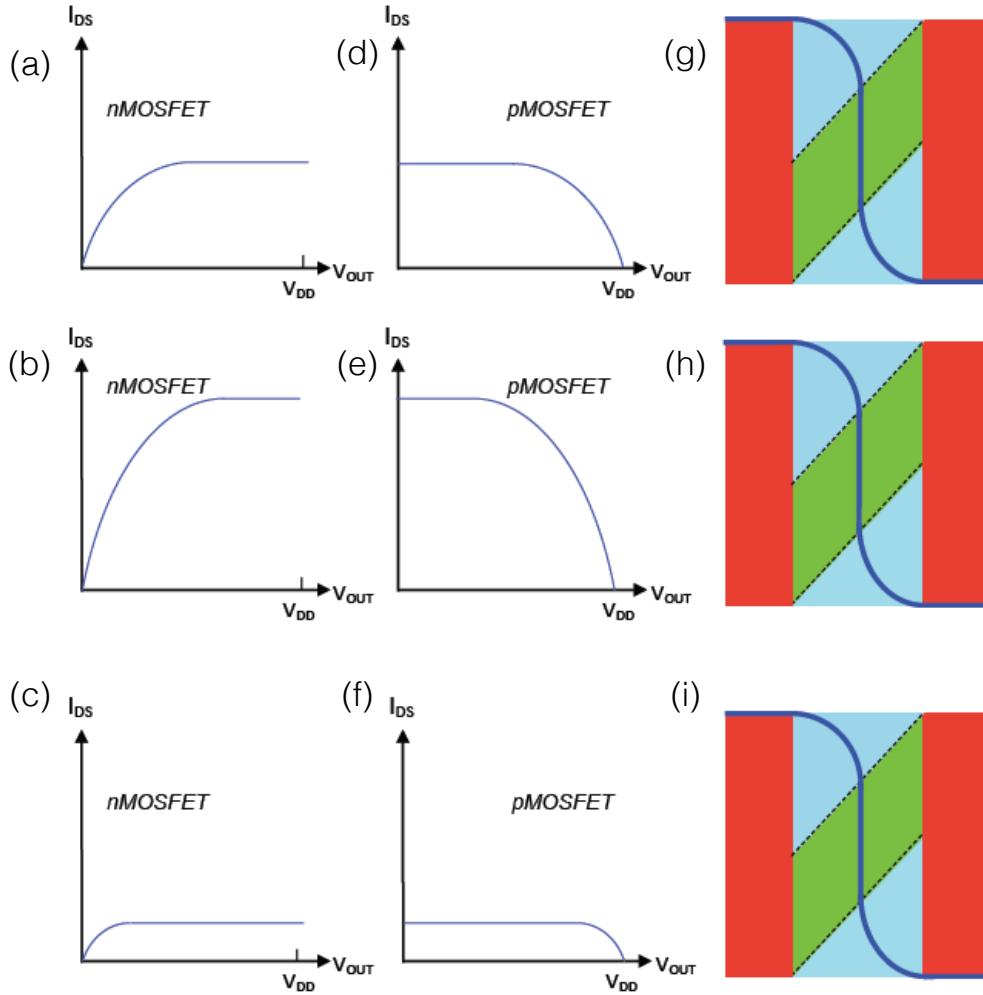

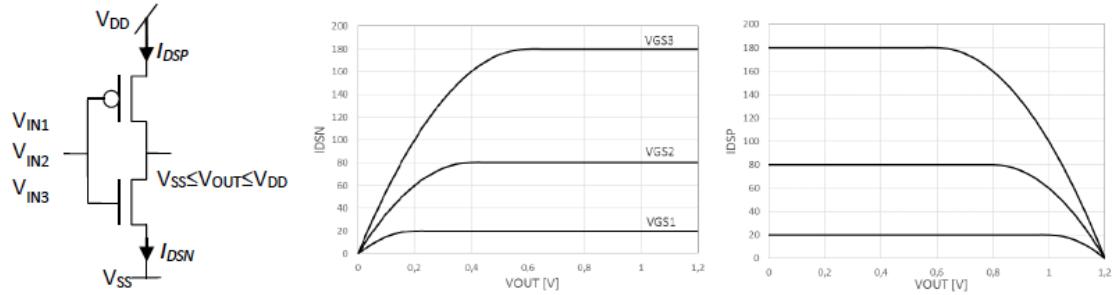

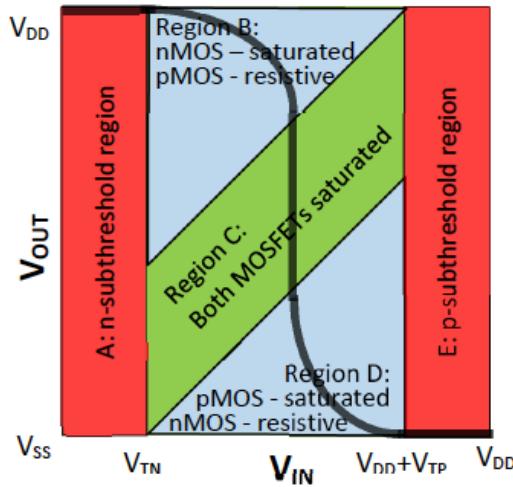

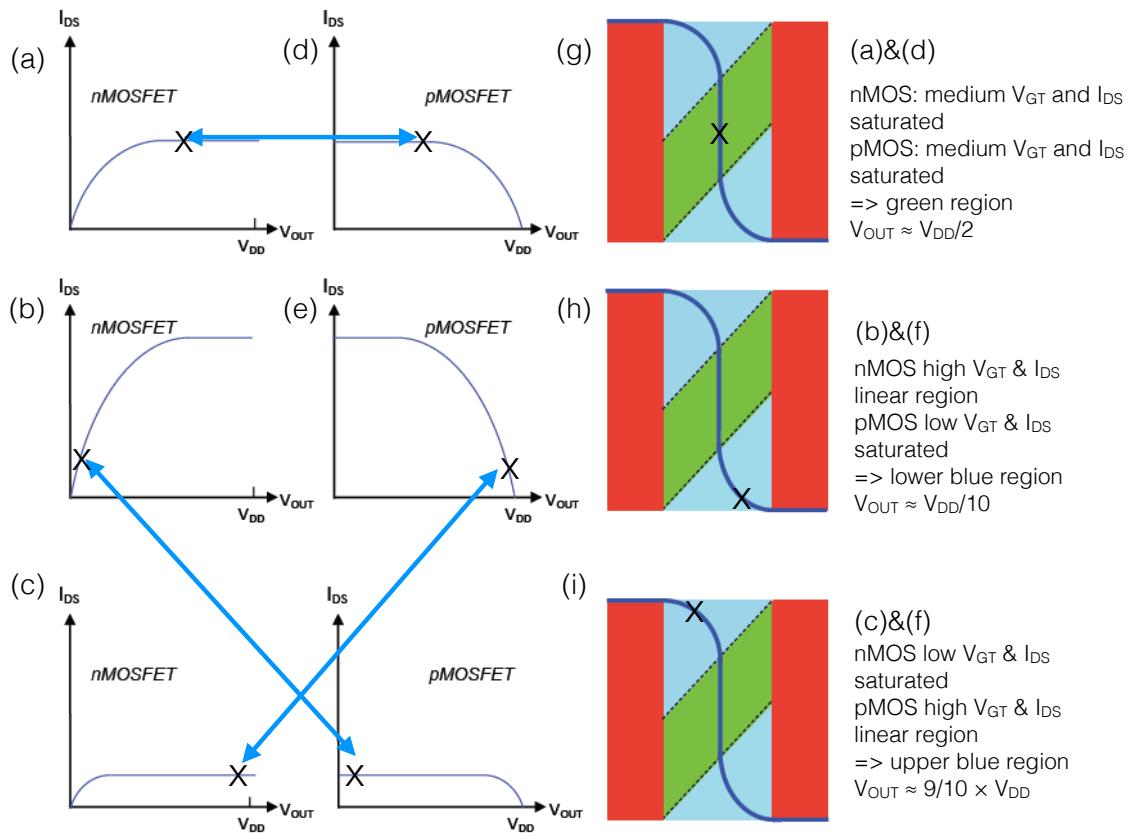

In Figure 5.1 you see the graphs of  $I_{DS}$  vs  $V_{OUT}$ , for the nMOS and pMOS FETs in a CMOS inverter. Match the three nMOS characteristics (a) through (c), shown to the left in in Figure 5.1. with the pMOS characteristics, (d) through (f) that corresponds the same input voltage. Then mark the corresponding bias points in the three voltage transfer curves (g) through (i) to the right. For more details on the red, blue, and green VTC diagrams refer to Figure 5.3.

**Exercise 5.2:** Task tests understanding of voltage transfer curves, nMOS and pMOS transistors and and inverter bias point. It is a variation of 5.1 *Solution on page 47.*

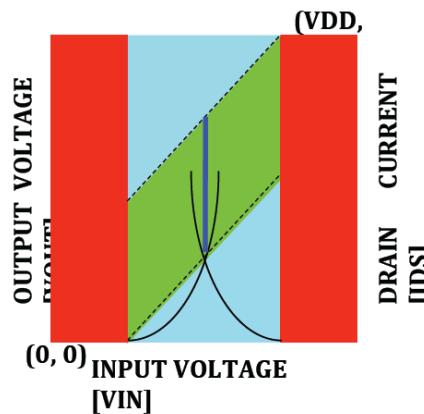

For three different input voltages, the output voltage of an inverter is swept from  $V_{SS}$  to  $V_{DD}$  while measuring the two MOSFET currents,  $I_{DSN}$  and  $I_{DSP}$ . The resulting current-voltage characteristics thus obtained are shown in Figure 5.2.

- Match the two MOSFET currents for each of the three inverter input voltages, and find the bias points where the two currents are equal.

- In the diagram of CMOS inverter regions shown in Figure 5.3 mark each of these three bias points with B, C, or D, depending on the region of operation in the  $V_{OUT}$  vs  $V_{IN}$  graph to which they belong.

**Exercise 5.3:** Task tests understanding of inverter switching voltage and VTC. *Solution on page 47.*

- Add a secondary axis representing the “short-circuit” current through the inverter as shown in Figure 5.3. Sketch the “short-circuit” current through the inverter vs.  $V_{IN}$  based on your knowledge about the current through the current-limiting MOSFET.

- Use the square-law MOSFET model and Kirchhoff’s current law to derive the expression for the switching voltage of an electrically symmetrical CMOS inverter ( $k_n = k_p$ ,  $V_{TN} = -V_{TP}$ )?

- What happens to the switching voltage if  $k_n = 4k_p$ ?

- Derive an expression for the inverter switching voltage ( $V_{IN} = V_{OUT}$ ) in the general case based on the square-law MOSFET models.

Figure 5.1: To the left, (a) to (c), are three nMOS characteristics each for one input voltage. In the middle, (d) to (f), are three pMOS characteristics for the same input voltages but not in the order that correspond to that of the nMOS characteristics. To the right, (g) through (i), are three transfer curves in which to indicate the bias points for cases (a) through (c).

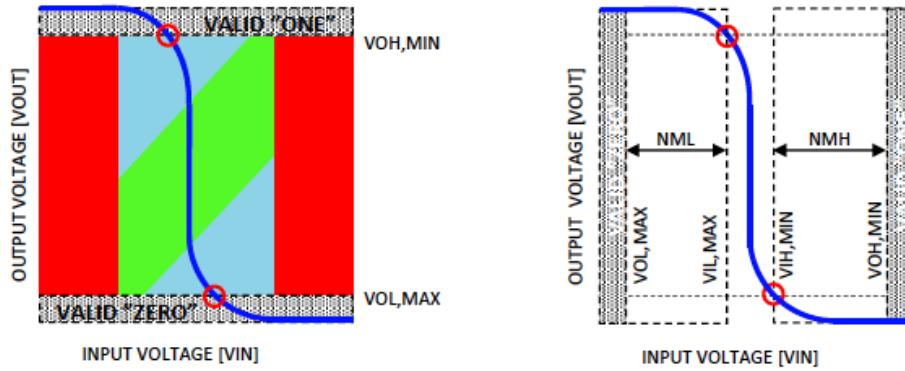

**Exercise 5.4:** Task tests understanding of noise margins. *Solution on page 49.*

The solution for this problem is not included yet, because this problem is part of prelab 1.

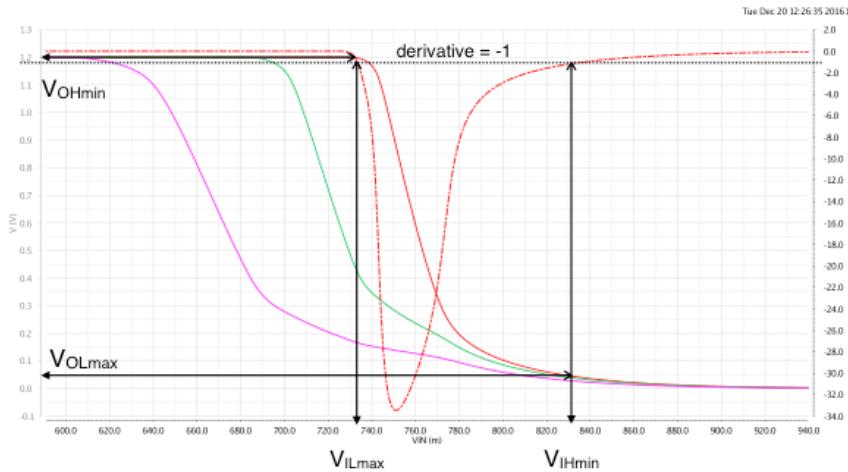

To account for voltage fluctuations, i.e. noise, the valid high and low output voltages are usually defined within certain ranges like  $0 \leq V_{OUT} \leq V_{OL,max}$ , and  $V_{OH,min} \leq V_{OUT} \leq V_{DD}$ . Since CMOS is a robust technology, the input voltage can vary within ranges larger than those defined for valid output voltages without causing invalid output voltages,  $0 \leq V_{IN} \leq V_{IL,max}$ , and  $V_{IH,min} \leq V_{IN} \leq V_{DD}$ . These regions are usually defined from the two points,  $(V_{OL,max}, V_{IH,min})$  and  $(V_{OH,min}, V_{IL,max})$ , on the VTC where the amplifications are equal to minus one,  $A_v = -1$ .

a) Derive expressions for the low and high noise margins, NML and NMH, as defined in the Figure 5.4 using the following expressions for  $(V_{OL,max}, V_{IH,min})$  and  $(V_{OH,min}, V_{IL,max})$ :

$$\begin{aligned} V_{OL,max} &= \frac{V_{DD} + V_{TP} - V_{TN}}{8}, \quad V_{IH,min} = V_{SW} + \frac{V_{DD} + V_{TP} - V_{TN}}{8} \\ V_{OH,min} &= V_{DD} - \frac{V_{DD} + V_{TP} - V_{TN}}{8}, \quad V_{IL,max} = V_{SW} - \frac{V_{DD} + V_{TP} - V_{TN}}{8}. \end{aligned}$$

b) What are the explicit noise margin values in terms of fraction of  $V_{DD}$  if  $V_{TN} = -V_{TP} = V_{DD}/5$ ?

Figure 5.2: The CMOS inverter with three input voltages and corresponding curves for NMOS and PMOS transistors.

Figure 5.3: The CMOS inverter voltage transfer curve (VTC) with regions marked.

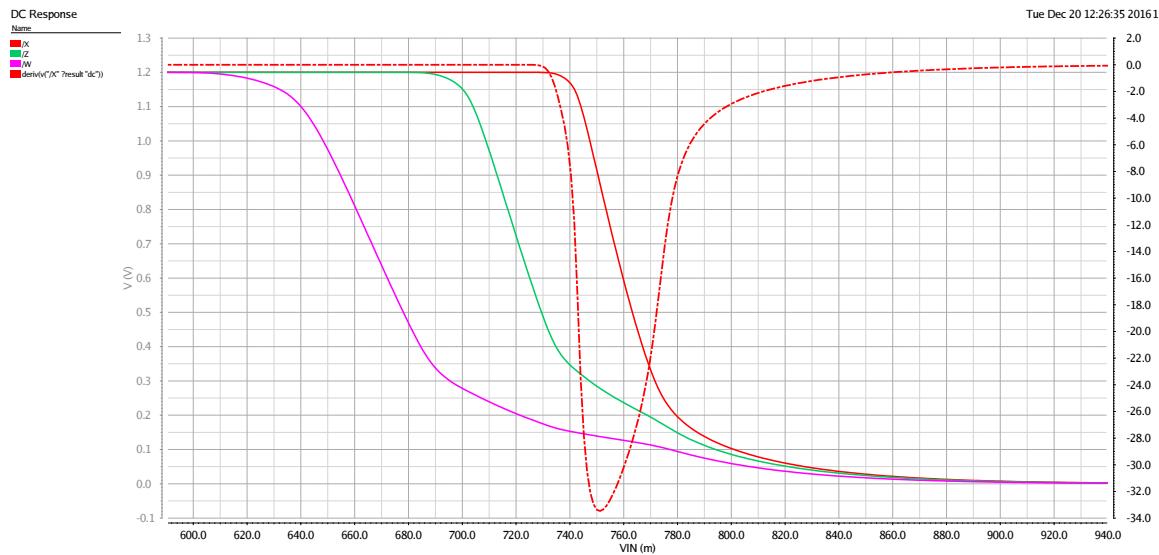

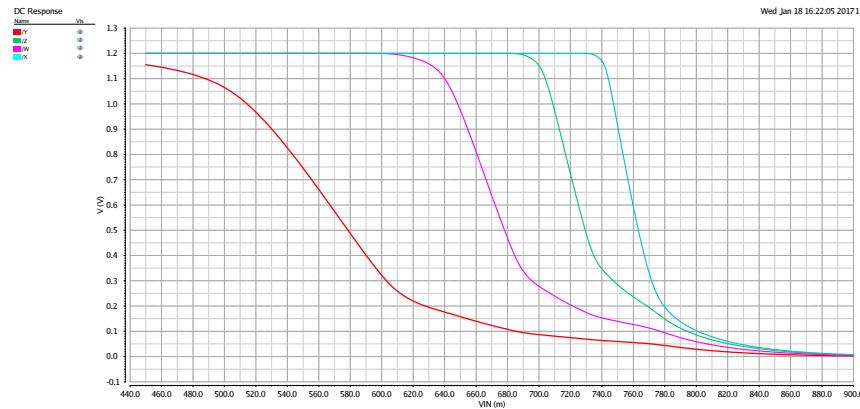

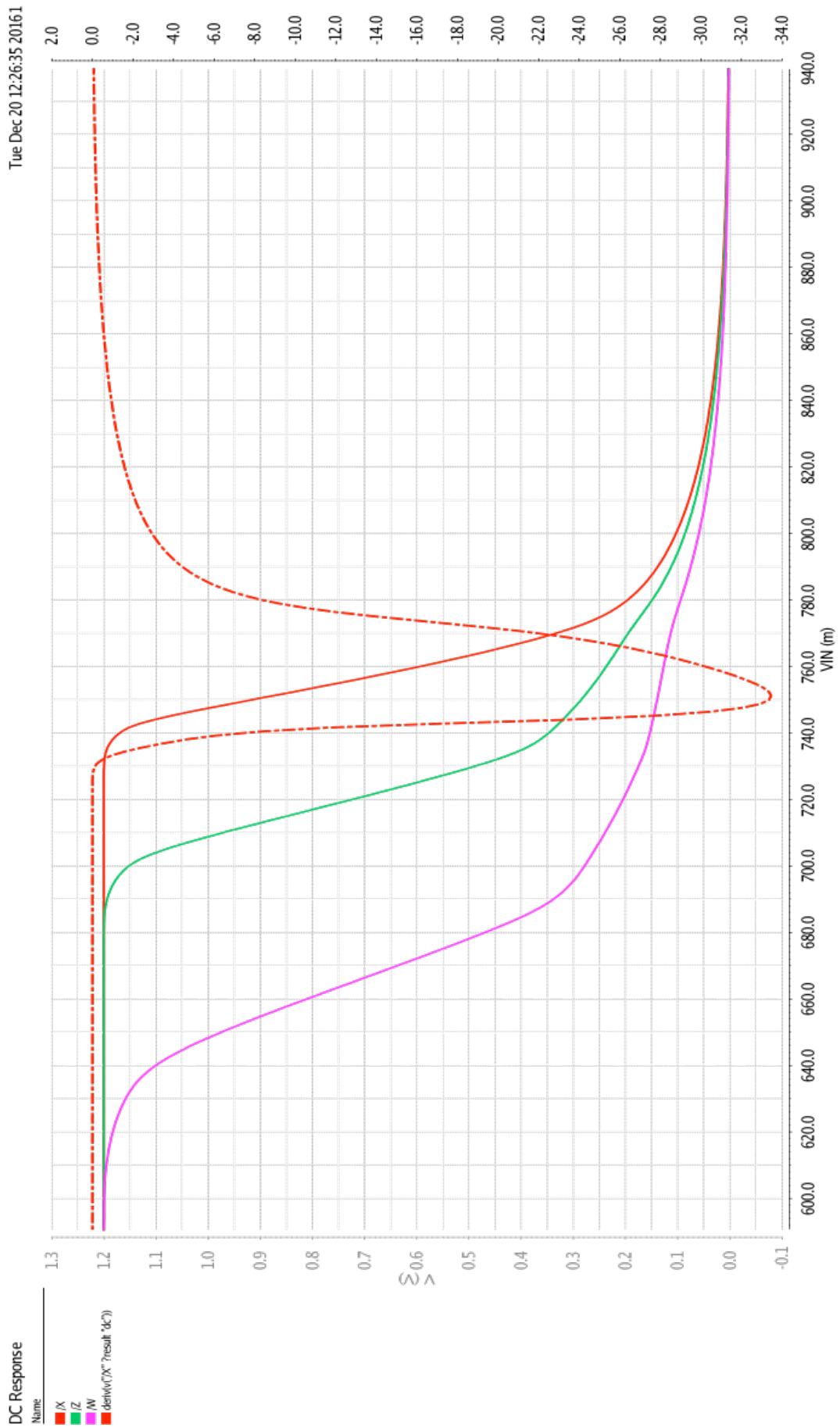

**Exercise 5.5:** Problem tests understanding of voltage transfer curves and noise margin. Slightly adapted from exam 2016-12-22 Tasks 2(a) and (c). *Solution on page 49.*

Figure 5.5 shows the voltage transfer curves for three of the four logical gates in the schematic Figure 3.1 simulated with all transistors having the same widths and with all four inputs, A-D, connected together, so that there is now only one input. The VTCs have been simulated in a DC analysis in Cadence in the usual 65 nm process. For simplicity you can assume that  $V_{TN} \approx -V_{TP}$ .

- Which logical output of Y1-Y4 corresponds to each of the three VTCs named X (red), Y(green) and W(purple) in the graph in Figure 5.5? Motivate! (3 p)

- In Figure 5.5 is also a plot of the derivative of the VTC for the X output (the red dash-dotted line). From the data given in Figure 5.5 calculate the noise margin for the X output. The graph in Figure 5.5 is repeated in larger scale in Figure A.1 for your convenience. (3 p)

## 5.2 Dynamic characteristics

**Exercise 5.6:** Task tests RC circuits. *Solution on page 49.*

From chapters. Missing solution.

Analyze the RC circuit and show that the time needed for the exponential decay of the voltage across the capacitor

Figure 5.4: The The definition of noise margins.

Figure 5.5: Voltage transfer curves (VTC) for the three outputs X, Y and W and the derivative of the VTC for output X.

to 50 % of the initial voltage,  $V_{DD}$ , is given by  $t_d = RC \ln(2)$ !

**Exercise 5.7:** Task tests understanding of inverter R,C and delay calculation. *Solution on page 49.*

- What do we mean with an ideal inverter concerning its parasitic output capacitance?

- Calculate the propagation delay of an ideal inverter driving an identical inverter! Assume the following MOSFET data: n-channel MOSFETs can sink  $500 \mu\text{A}/\mu\text{m}$  channel width at  $V_{DD} = 1 \text{ V}$ , and their input capacitances are  $1.3 \text{ fF}/\mu\text{m}$ . The p-channel MOSFET is made twice as wide as the n-channel device to obtain the same driving capability.

**Exercise 5.8:** Task tests understanding fanout-of-four delay. Exam 2012-10-26 Problem 2. *Solution on page 50.*

2017-09-07 Resistance values updated to reflect that 0.7 factor nowadays is not included in R.

- Calculate the FO4 delay of a  $0.35 \mu\text{m}$  CMOS process with  $V_{DD} = 3.3 \text{ V}$  if the effective resistance in the timing model,  $R_{\text{eff}}$ , is  $6 \text{ k}\Omega \mu\text{m}$  and the inverter input capacitance is  $6 \text{ fF}/\mu\text{m}$ . Assume  $p_{\text{inv}} = 1$ . (3 p)

- What is the FO4 delay in a  $65 \text{ nm}$  process if we assume  $V_{DD} = 1.2 \text{ V}$ ,  $R_{\text{eff}} = 2 \text{ k}\Omega \mu\text{m}$ ,  $C_G = 4.5 \text{ fF}/\mu\text{m}$ , and  $p_{\text{inv}} = 1/3$ ? (2 p)

**Exercise 5.9:** Task tests understanding of inverter R,C and delay calculation. *Solution on page 49.*

From chapters. Missing solution.

- Assume that we, for simplicity, introduce a modified effective resistance  $R' = R \ln(2)$ , how large would this resistance be for the MOSFET in exercise 5.8?

- How does the use of  $R'$  modify our delay model?

**Exercise 5.10:** Task tests understanding inverter operation, inverter switch voltage. Exam 2013-08-26 Problem 2. Slightly modified. *Solution on page 50.*

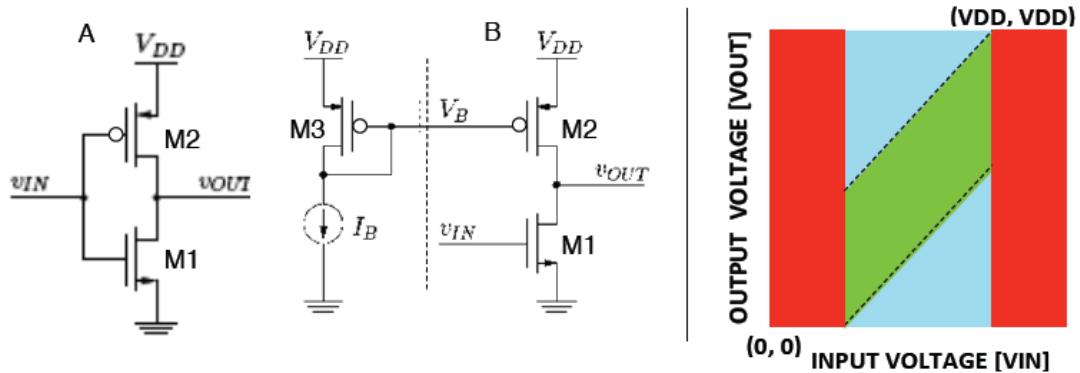

Figure 5.6: Two CMOS inverters. (A) is a regular CMOS inverter (B) is a pseudo-NMOS inverter intended for use as an amplifier. To the right is a diagram showing the MOSFET regions of operation in CMOS.

In Figure 5.6 you see the circuit diagram for two CMOS inverters, (A) and (B). Inverter (A) is an ordinary CMOS inverter that switches at an input voltage of  $V_{DD}/2$ . Inverter (B) is a pseudo-NMOS inverter intended for use as an amplifier. Its load p-channel MOSFET, M2, is biased at an unknown gate voltage  $V_B$  determined by a current mirror. A current mirror takes current  $I_B$  from a constant-current source and mirrors it to the inverter. Except for the biasing arrangement, the two CMOS inverters are identical. That is, transistors M1 and M2, respectively, are the same MOSFETs in both inverters. The rightmost diagram in the figure above shows the MOSFET regions of operation in CMOS.

- Relate the two current gain factors  $k_1$  and  $k_2$  of MOSFETs M1 and M2 to each other considering that inverter (A) flips at  $V_{DD}/2$  assuming symmetrical threshold voltages,  $V_{TN} = -V_{TP} = V_{DD}/5$ ? (2 p)

- Assuming  $V_B = 0.6V_{DD}$ , what is the switching voltage of the pseudo-NMOS inverter (B)? (2 p)

- Calculate current  $I_B$  if  $V_{DD} = 1.2$  V, and  $k = 600$  mA/V<sup>2</sup>! (2 p)

- For what output voltage range are both MOSFET devices saturated in inverter (A)? Refer to the right-hand diagram showing the CMOS regions of MOSFET operation! (2 p)

- For what output voltage range are both devices saturated in the pseudo-NMOS inverter? Refer to the right-hand diagram showing the CMOS regions of MOSFET operation! (2 p)

### 5.3 Tapered buffers etc.

**Exercise 5.11:** Task tests understanding of inverter delay calculation and minimization. *Solution on page 50.*

Missing solution.

Four is sort of a magic number, if the number of loading inverters becomes much larger than four, it is often more efficient to insert an extra inverter with a better driving capability as a buffer between the original inverter and the capacitive load.

- What driving capability should the inserted buffer inverter have to minimize the delay?

- For what number of loading inverters does the inserted buffer shorten the propagation delay?

- How does the parasitic output capacitance influence these critical numbers?

**Exercise 5.12:** Task tests understanding of inverter delay calculation and minimization. *Solution on page 51.*

Mssing solution.

For how big a capacitive load would the insertion of a non-inverting, two-inverter buffer give the shortest propagation delay?

**Exercise 5.13:** Task tests understanding of inverter delay calculation and minimization. *Solution on page 51.*

Mssing solution.

- Determine the number of buffer inverters needed to minimize the delay if the load capacitance is 1000 times larger than the inverter input capacitance?

- What would be the optimum tapering factor?

**Exercise 5.14:** Task tests understanding of how to deign a tapered buffer. Exam 2015-01-09 Problem X. *Solution on page 51.*

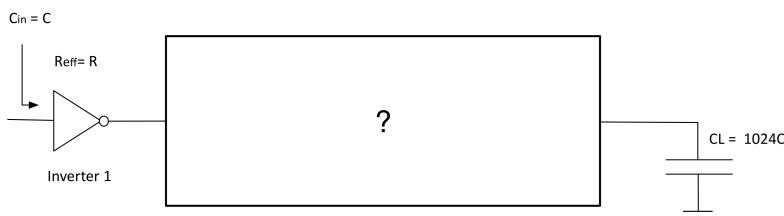

In a chip you are responsible for designing a driver for an output pad. The capacitance of the pad is (around)  $1024C$  where  $C$  is the input of the minimum inverter in the process. The setup is shown in the figure below. The polarity of the output signal is not important in this particular case. Assume that the parasitic output capacitance is half of the inverter input capacitance (that is  $p_{inv} = 0.5$ ). Tau in the particular process is 4 ps. (Tasks c) and d) of this exam problem will appear when we get to power and energy.)

Figure 5.7: The setup for the driver that you are to design.

- If minimum delay is the main design goal, how many inverters do you choose to use in the box with the question mark? How would you size them? Draw a figure of your entire inverter chain with the inverter sizes clearly marked. Motivate your design choices, but proofs are not required. (4 p)

- For your design what is the delay? (2 p)

#### BONUS QUESTION

- What if in a similar design situation as in task a) the polarity at the output were of importance and the obvious design choice was an odd number of inverters? Would you add one more inverter or would you remove one? Discuss your considerations. (2 p)

# Chapter 6

## Delay for complex gates and paths

### 6.1 Gate delay

**Exercise 6.1:** Task tests understanding of calculating logical effort,  $g$ , and parasitic delay,  $p$ , for simple gates. *Solution on page 51.*

Imagine that you have started working with a CMOS process where for the pMOS transistors the maximum saturation current is only 1/3 of that for an nMOS transistor of the same width (as usual we assume that we use the minimum length for all transistors).

- Find the parasitic delay,  $p$ , and the logical effort,  $g$ , for a 2-input NAND and a 2-input NOR gate in this process. Assume that  $p$  for the inverter (sometimes called  $p_{inv}$ ) is 0.5.

- Imagine that the NAND2 gate in this process, which you analysed in task a), is connected to one 3-to-1 scaled inverter at its output to create an AND gate. If the pMOS transistors in the inverter gate are twice as wide as the ones in the NAND2 gate, what the normalized delay of the NAND2 gate?

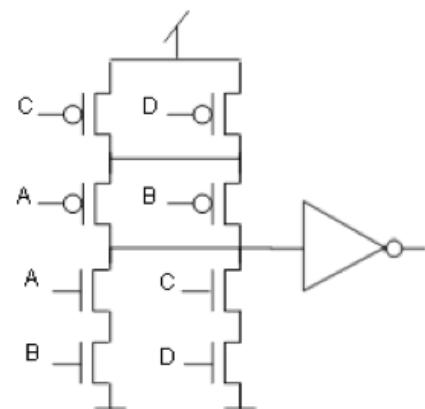

**Exercise 6.2:** Task tests understanding of calculating logical effort,  $g$ , and parasitic delay  $p$ , for complex gates. *Solution on page 53.*

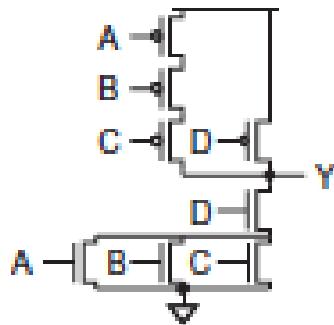

In Figure 6.1 you see two complex gates that we have found in the textbook. Again the task is to calculate the parasitic delay,  $p$ , and the logical effort,  $g$ . Note that in these gates the logical effort will not be the same for all the inputs, so you have to calculate one  $g$  value per input. In contrast, the parasitic delay,  $p$ , is related to the output, so there cannot be more than one value for  $p$  for one specific circuit topology. As usual, assume that the p-transistor current is twice the n-transistor current for the same transistor width.

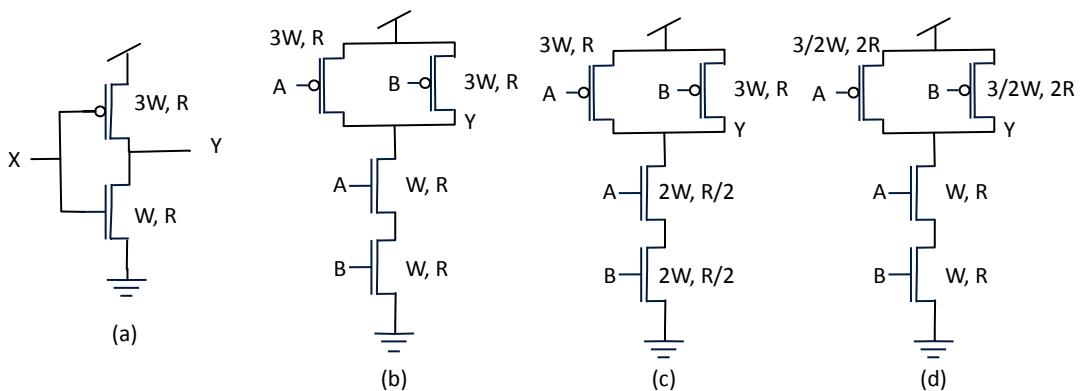

**Exercise 6.3:** Task tests understanding of transistor scaling for same worst-case resistance. Exam 2016-12-22 Task 1(c). *Solution on page 53.*

Refer to Figure 3.1. What if your task was to ensure that the worst-case resistance is the same for the p-net and the n-net for all four logic functions, Y1 – Y4. How would you size the transistors then? Assume that the drive strength of an nMOS transistor is twice that of a pMOS transistor with the same width. There are multiple solutions – you only have to give one. (3 p)

### 6.2 Path delay

**Exercise 6.4:** Problem tests understanding of how to calculate the path delay. *Solution on page 53.*

**FIGURE 1.19**

CMOS compound gate

for function

$Y = (A + B + C) \cdot D$

$$\begin{aligned} G_{2:1} &= G_2 + \bar{K}_2 G_1 \\ &= A_2 B_2 + (A_1 + B_2) A_1 B_1 \end{aligned}$$

(b) The second complex gate.

(a) The first complex gate.

Figure 6.1: Two complex gates for which to calculate logical effort and parasitic delay. Both are taken from the textbook.

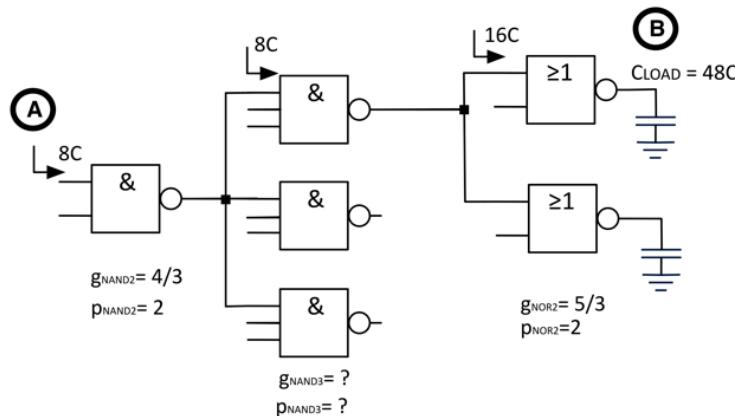

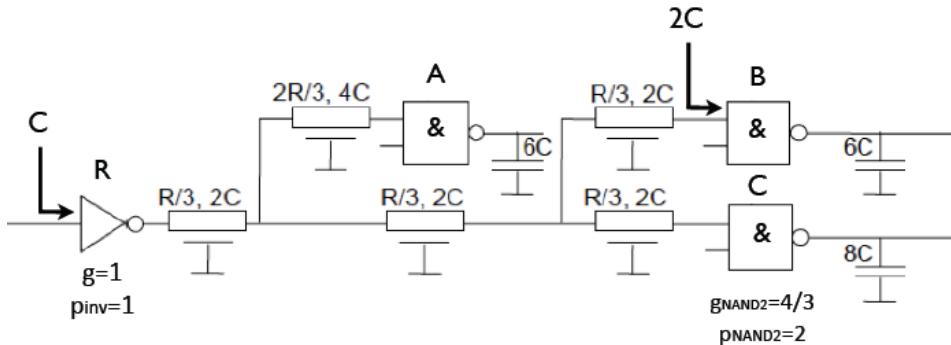

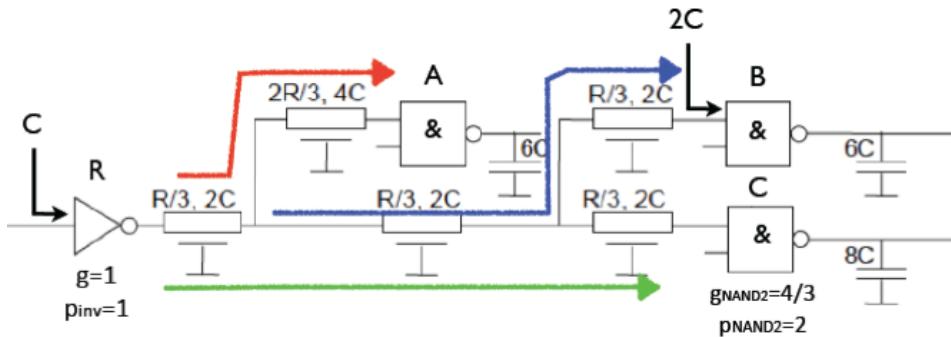

In Figure 6.2 you see a path through a circuit made up of NAND and NOR gates. Add the missing data for the 3-input NAND gate and calculate the delay from A to B. In this process  $p_{inv}$  is 1.

Figure 6.2: A path of NAND and NOR gates for which to calculate the path delay.

**Exercise 6.5:** Problem tests understanding of how to optimize the path delay. *Solution on page 54.*

Again consider the path shown in Figure 6.2. However this time assume that the load capacitance is 45C. Your task is to find the optimal sizes for the 3-input NAND and 2-input NOR gates to minimize the delay. What are the sizes and what is the delay when these sizes are applied?

**Exercise 6.6:** These three tasks test understanding of logical effort and path effort, and delay minimization Exam 2016-12-22 Problem 3. *Solution on page 55.*

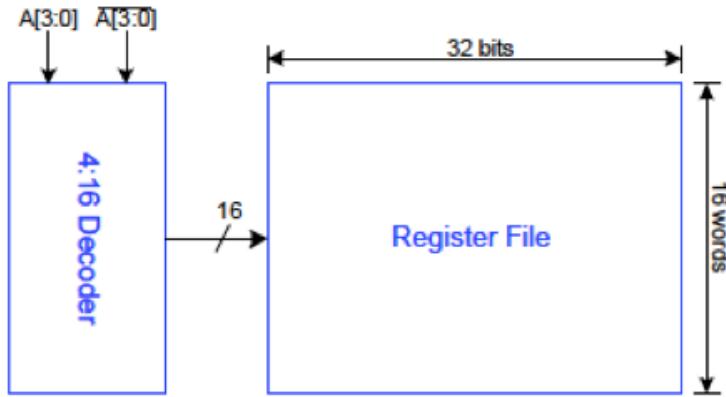

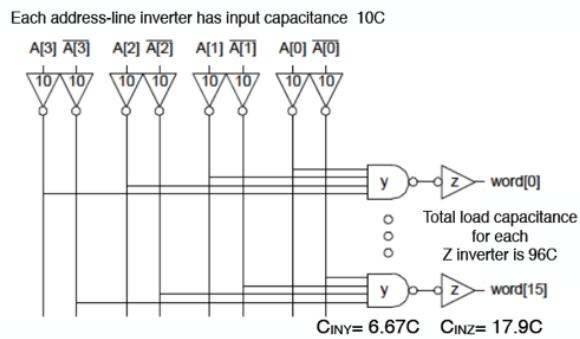

In Figure 6.3 you see a block diagram schematic of a register file with 16 32-bit words and a 4-to-16 decoder that selects one of the 16 registers according to the address A[3:0].

Figure 6.3: Block diagram of 4-to-16 decoder for addressing register file.

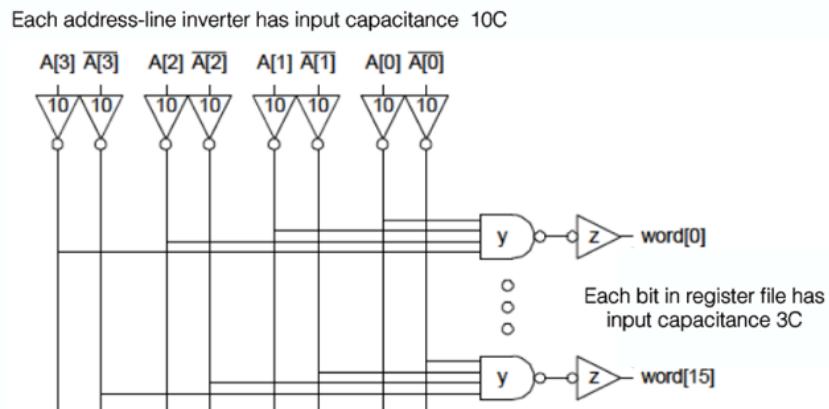

In this problem your task is to size the decoder circuitry shown in detail in Figure 6.4.

Figure 6.4: Detail of 4-to-16 decoder for addressing register file.

- How should the 4-input nand gate (labelled  $y$  in Figure 6.4) and inverter (labelled  $z$  in Figure 6.4) be sized for minimum delay with the assumptions given in Figure 6.4? Assume that an nMOS transistor has twice the current of a pMOS transistor of the same width. (5 p)

- What is the resulting delay, including parasitic delays with the sizing from your result in task a)? Assume that the inverter's output capacitance is the same as its input capacitance. (2 p)

- What if we had a wider register file of 16 64-bit words? Would it be faster to use two inverters in place of inverter  $z$ ? (One would also have invert the address bits of course, but that could easily be achieved by swapping the lines for each address bit and its inverse). Motivate your reply. (3 p)

# Chapter 7

## Wire delay

**Exercise 7.1:** Task tests understanding of wire approximation. *Solution on page 58.*

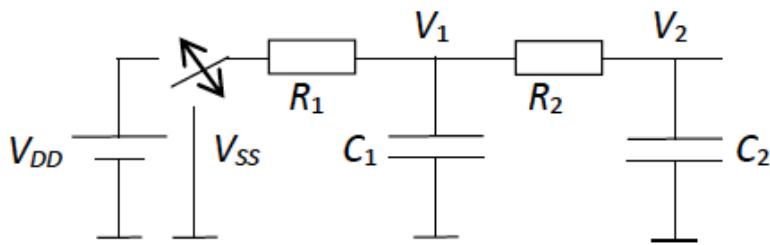

Figure 7.1: A two-node RC system.

Solution to be added for b and c

Shown in Figure 7.1 is a simplified version of the two-pole network from the book chapter.

- Write down the two nodal equations for  $V_1(t)$  and  $V_2(t)$ .

- Find a method to convert these two nodal equations into second-order linear differential equation for  $V_1(t)$  and  $V_2(t)$ .

- Use the characteristic equation you found in task b), and identify  $(s + a)(s + b) = s^2 + (a + b)s + ab = 0$  to find a simple way of determining the dominating time constant  $1/a$  if  $1/a \gg 1/b$ .

**Exercise 7.2:** Task tests ability to calculate wire parameters. *Solution on page 56.*

In a certain CMOS process the wire sheet resistance is  $0.2 \Omega/\square$  and the wire capacitance is  $0.4 \text{ fF}/\mu\text{m}^2$ .

- For a 200 nm wide wire calculate the resistance and capacitance for a wire that is 25  $\mu\text{m}$  long.

- Calculate the critical wire length for a wire that is 100 nm wide when the wire is driven by an inverter (that is, a repeater) with time constant  $t_{rep} = 4.6 \text{ ps}$ .

**Exercise 7.3:** Task tests ability to calculate wire parameters. *Solution on page 56.*

In another CMOS process, the wire fringing field capacitance along the wire sidewalls cannot be neglected. This capacitance is  $35 \text{ aF}/\mu\text{m}$  (including both sidewalls). The bottom-plate capacitance is  $30 \text{ aF}/\mu\text{m}^2$ . The wire sheet resistance is  $0.10 \Omega/\square$ .

- Calculate the wire resistance and wire capacitance for a wire that is 10 mm long and 1  $\mu\text{m}$  wide.

b) Calculate the delay from the input of a driver inverter to input of an identical receiver inverter at the other end of the 10 mm wire from task a), if the inverter can deliver  $600 \mu\text{A}$  at  $V_{\text{DD}} = 1.2 \text{ V}$  and its input and output capacitances are both  $3.25 \text{ fF}$ .

c) For this process and wire width, what is the critical wire length?

**Exercise 7.4:** Task tests understanding inverter and wire delay calculations. Adapted from exam problem from 2008. *Solution on page 56.*

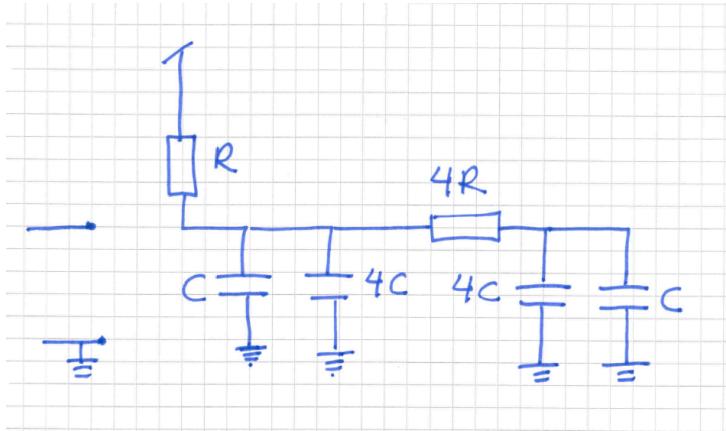

An inverter is driving another identical inverter across a rather long RC wire. The inverter input and output capacitances are both  $C$ , and its resistance is  $R$ . The wire resistance is  $4R$  and the wire capacitance  $8C$ .

- Draw a circuit diagram for the two inverters and the wire using a suitable model for the wire.

- Use the diagram to calculate the wire RC delay from the output of the driver inverter to the input of the receiver inverter.

- What if the *receiver* inverter were a NAND2 gate with input capacitance  $2C$ . What would the change in the delay be then?

- What if, instead, the *driver* inverter were a NAND2 gate with input capacitance  $2C$ . How would the delay change then?

- What if, instead, a branch wire ( $R, 2C$ ) were added at the midpoint of the wire. How much would the delay increase then?

- If the inverters in the original setup (task b) were properly scaled for minimum delay, what would be the resulting delay then?

**Exercise 7.5:** Task tests calculating wire and gate delay, logical effort. Exam 2016-08-22 Problem 3. *Solution on page 58.*

Figure 7.2 shows part of a clock-distribution network that comprises an inverter that acts as the clock driver, some wiring, and three identical NAND gates that act as clock gaters.

Figure 7.2: Clock-distribution network with a driver driving three receivers over different wires.

- Calculate the clock skews at the inputs of all three clock gaters: A, B, and C. The clock driver has a driver resistance  $R$  and an input capacitance  $C$ . The identical NAND2 gates all have an input capacitance of  $2C$ . (6 p)

- Calculate the clock skews at the outputs of the three NAND2 gates: A, B and C. (4 p)

**Exercise 7.6:** Task tests calculating wire delay and sizing path to drive wire. Exam 2015-10-29 Problem 4. *Solution on page 59.*

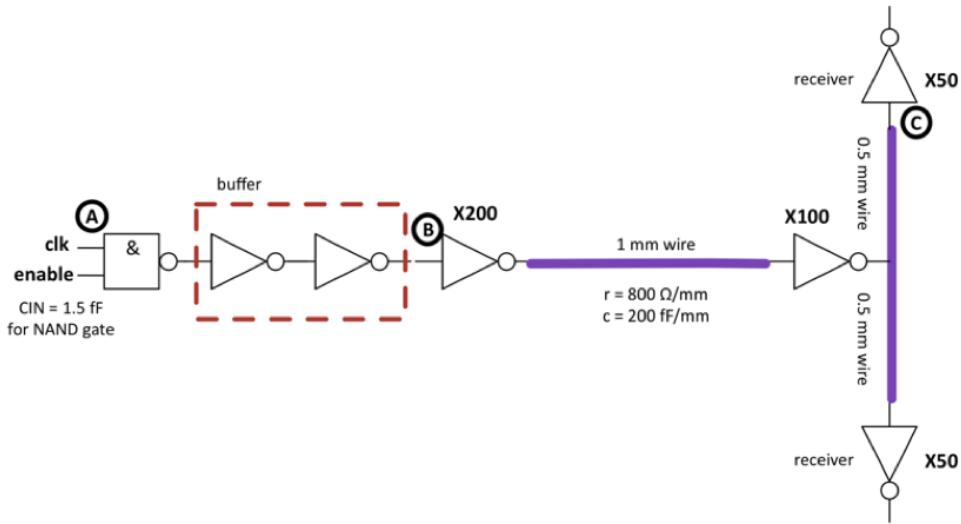

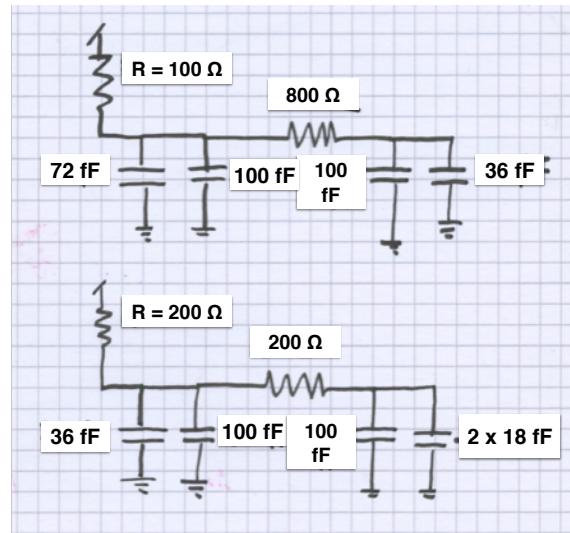

Figure 7.3 shows part of a clock-gated network for distributing a system clock on a chip. The largest available inverter in the cell library ( $X200, C_{\text{IN}} = 72 \text{ fF}, R = 100 \Omega$ ) was chosen to drive the wire network.

Figure 7.3: Clock-network for distribution of clock on chip.

- Calculate the delay from the input of the X200 inverter (point B) to the input of one of the X50 receivers (point C). You may assume that the input of the X200 inverter is driven by an infinitely strong driver. (4 p)

- There is a two-inverter buffer inserted between the clock-gating NAND gate and the X200 inverter. Design this buffer – that is, determine the sizes and/or input capacitances of the two buffer inverters for minimum delay from the CLK input of the NAND gate (point A) to the X200 inverter input (point B). (3 p)

- Calculate the resulting delay from the CLK input of the NAND gate (point A) to the X200 inverter input (B). (3 p)

**Exercise 7.7:** Task tests calculating wire parameters and resulting delays. Exam 2014-08-25 Problem 2.

Solution on page [60](#).

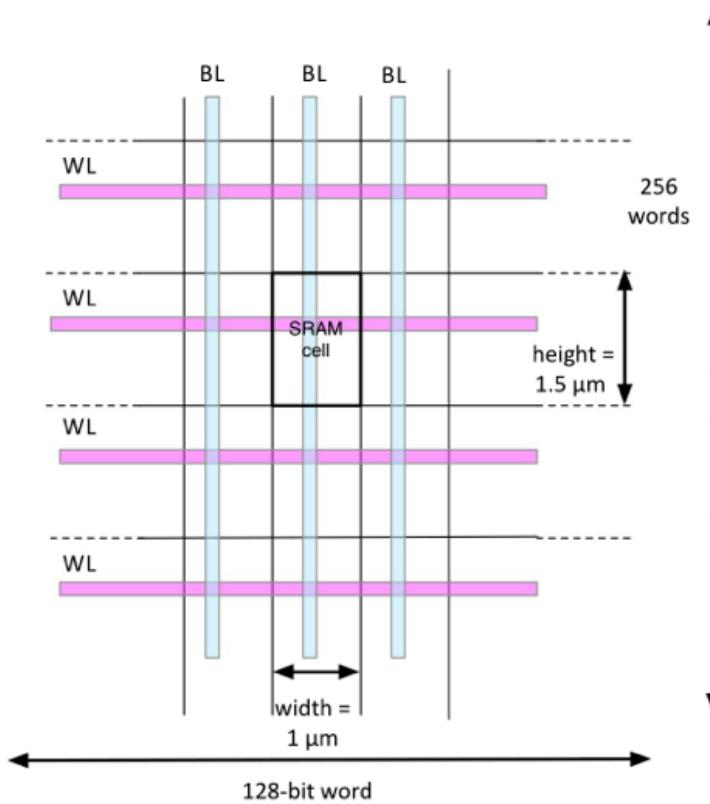

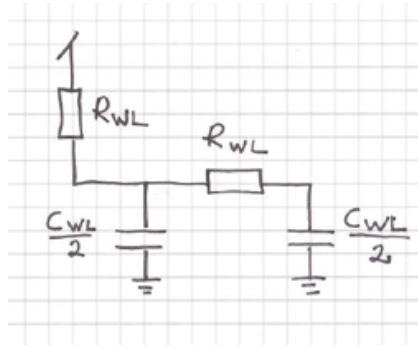

In Figure 7.4 you see the general layout of a static random-access memory (SRAM). The word lines (WL) select the particular word that is to be read or written. The bit lines (BL) carry the bit values out when reading and supply the bit values that are to be written when writing. The bit lines are routed in metal 1 (blue) and the word lines are routed in metal 2 (purple). In each memory cell the word line is connected to two minimum-size nMOS transistors for accessing that particular memory cell.

A word line is  $0.1 \mu\text{m}$  wide, which is the minimum width for an M2 wire in this particular process. A word line has a capacitance of  $0.1 \text{ fF}/\mu\text{m}$  to ground and an inter-wire capacitance to one adjacent word line of  $0.02 \text{ fF}/\mu\text{m}$  and the M2 layer has a resistance of  $0.1 \Omega/\square$ . A minimum-size nMOS transistor has a gate capacitance  $C_g = 0.1 \text{ fF}$ .  $V_{DD}$  is 1 V.

- Calculate the resistance for one WL.

- Calculate the total capacitance for one WL including the capacitance of the access transistors.

- Draw a circuit diagram for the WL and the inverter that is driving it. Assume the driver is an inverter with the same equivalent resistance as the WL resistance. Calculate the delay. For simplicity neglect the parasitic capacitance of the driver.

- Calculate the energy required for accessing the memory when reading the memory once.

- Estimate what would happen to the delay and energy computed in c) and d) if one could make the memory cells half as high and half as wide. Assume that the inter-wire capacitances are pure plate capacitances and the driver is re-sized so that its equivalent resistance still is the same as that of the wire. Reflect on the result.

Figure 7.4: General layout of SRAM memory bank with 256 128-bit words. The word lines (WL) run horizontally in metal-2 (purple) and the bit lines (BL) vertically in metal-1 (blue).

**Exercise 7.8:** Task tests calculating wire delay and sizing inverter to drive wire. Related to lab 4. Exam 2016-12-22 Problem 5. *Solution on page 60.*

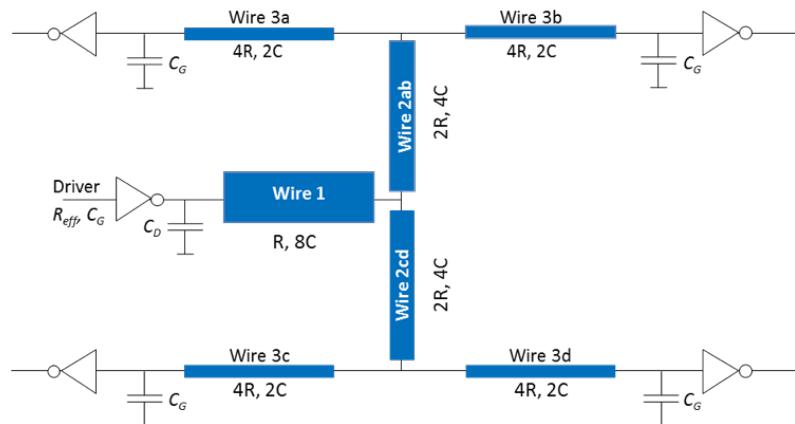

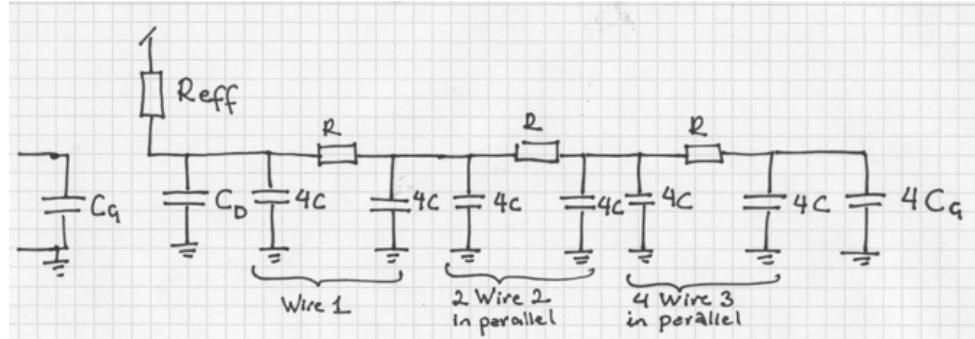

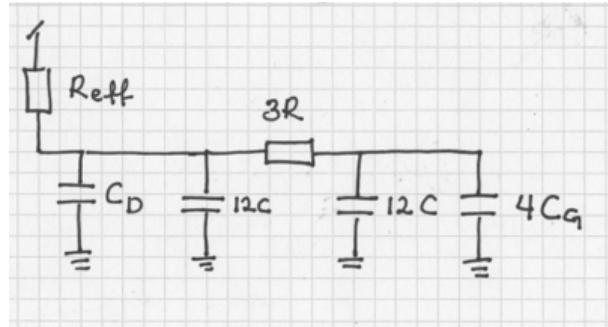

In Figure 7.5 you see a driver inverter loaded by four identical receiver inverters across an H-tree wire interconnect.

- Calculate the FO4 delay for the driver inverter when loaded as shown in Figure 7.5. (5 p)

- Determine the inverter resistance,  $R_{eff}$ , that minimizes the FO4 delay as calculated in a). You may assume that the inverter output capacitance,  $C_D$ , is equal to the inverter input capacitance,  $C_G$ . (5 p)

Figure 7.5: A driver inverter loaded by four identical receiver inverters across an H-tree wire interconnect.

# Chapter 8

## Layout

**Exercise 8.1:** Problem tests the understanding of continuous-line-of-diffusion layout. *Solution on page 61.*

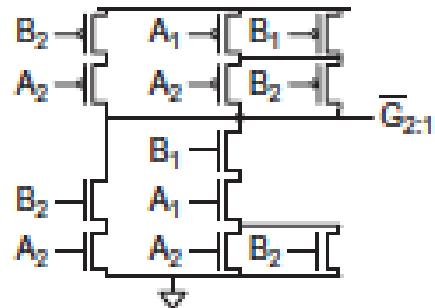

- Using Euler paths determine if it is possible to lay out the gate shown in Figure 6.1 a) with single-line-of-diffusion approach. If it is possible determine one order of the input signals in the layout that will work.

- Using Euler paths determine if it is possible to lay out the gate shown in Figure 6.1 b) single-line-of-diffusion approach. Assume that the repeated signals, A2 and B2, will also be repeated in the diffusion line. If it is possible, determine one order of the input signals that will work.

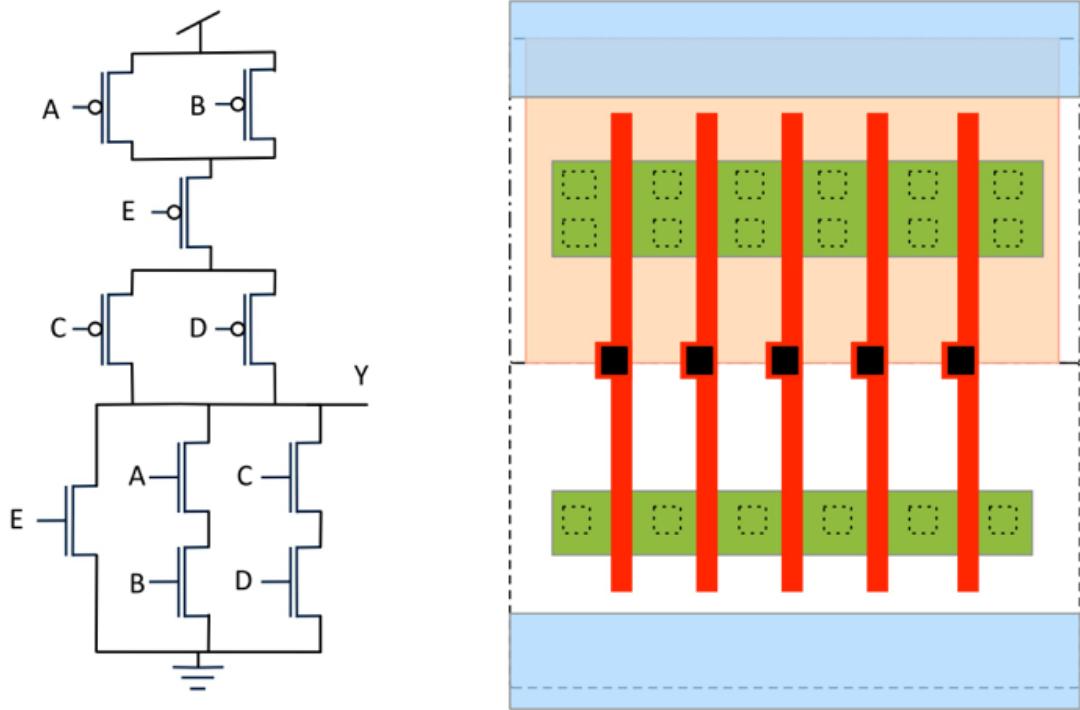

**Exercise 8.2:** Problem test understanding of layout, parasitic delay and logical effort of multi-stage gates. Adapted from problem 1 in exam 2016-08-22. *Solution on page 62.*

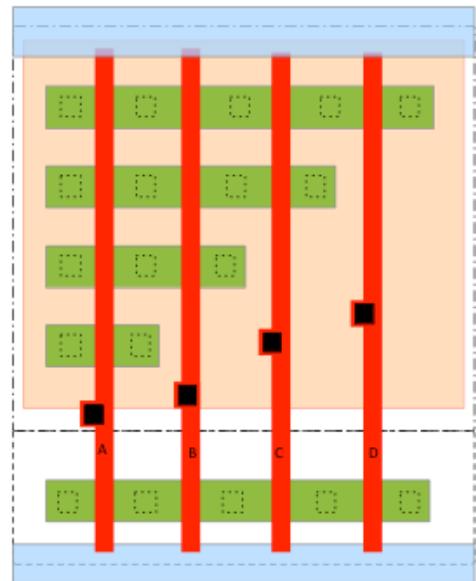

Figure 8.1: Template for 4-input AND gate.

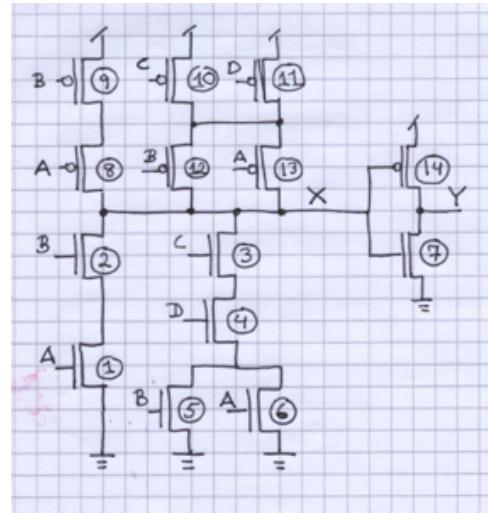

For a 4-input NAND gate we have previously found that the logical efforts for all inputs are 2 and the parasitic delay is  $4 \times p_{inv}$ . In this problem you will layout and model a 4-input AND gate using such a NAND gate. You can assume that  $p_{inv} = 1$ .

- In the cell layout template in Figure 8.1 you see the layout of one inverter to the right. To the left of that inverter is a continuous-line-of-diffusion template. Draw the layout for the 4-input NAND gate there; also

connect the output of the NAND gate to the inverter input, thus forming a 4-input AND gate. Draw the layout such that you minimize the number of diffusion areas connected to the output node of the NAND gate. (3p)

b) The parasitic delay,  $p$ , of a static CMOS gate is due to the capacitances of the diffusion areas connected to the gate output. Find the value for  $p_{NAND4}$  for your layout from task a). Assume that the capacitance of a diffusion area of a particular width is the same if it is shared between two transistors as if it is not shared. (2p)

c) For the 4-input AND gate, formed by the inverter and the 4-input NAND gate, find the logical effort,  $g_{AND4}$ , (the same for all four inputs), and parasitic delay  $p_{AND4}$ , for the entire gate. Use the  $p_{NAND4}$  value from task b) and find the relative transistor widths from the layout. (3p)

**Exercise 8.3:** Problem tests going from schematic to layout and from layout to schematic and logical function. Exam 2015-08-24 Task 1. *Solution on page 63.*

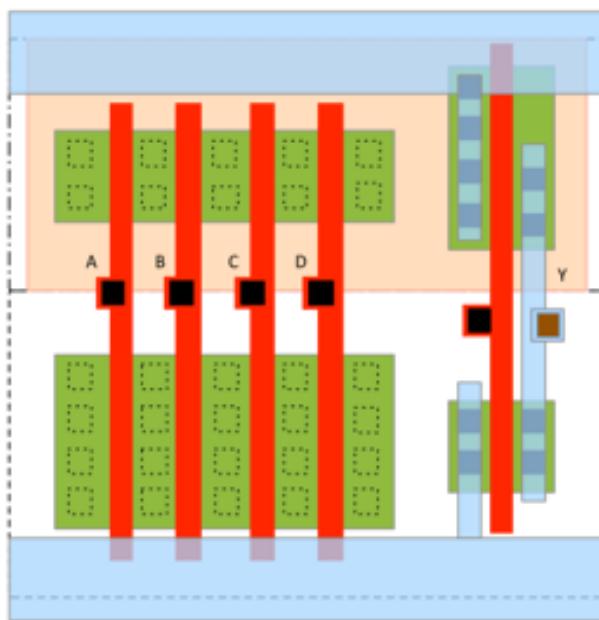

a) Figure 8.2a shows the circuit schematic for a compound gate that implements a 5-input logical function. Draw the corresponding layout in the template supplied in 8.2b. The layout should correspond exactly to the schematic – logical equivalence is not enough. Label all inputs and outputs. Indicate clearly any contacts to metal. (5 p)

Figure 8.2: A 5-input static CMOS gate.

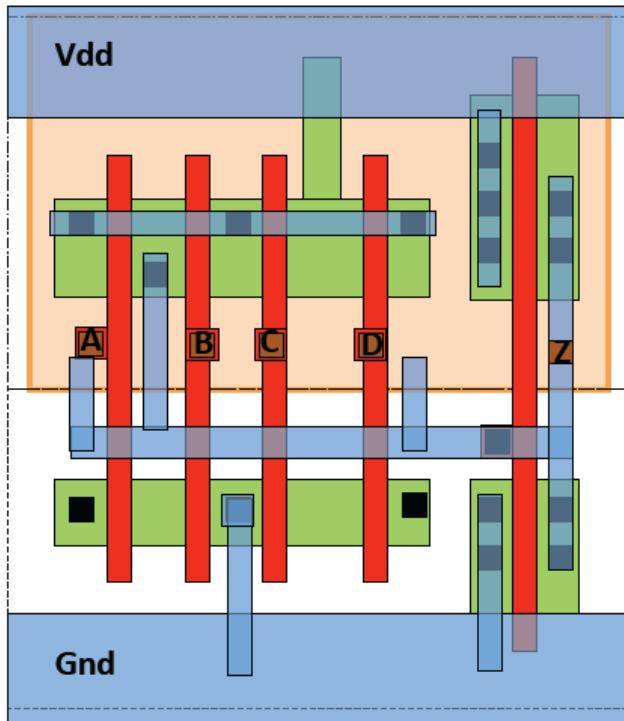

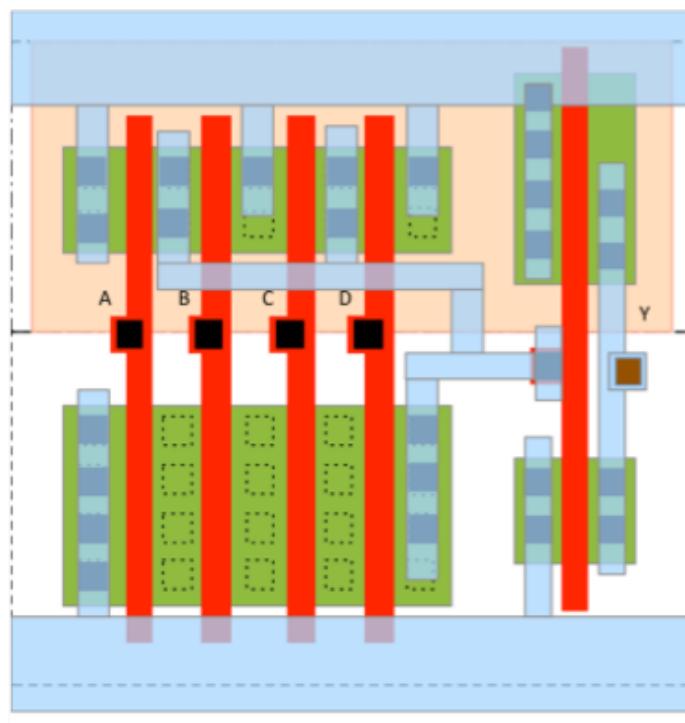

b) In Figure 8.3 is the layout for a compound static CMOS implementation of a 4-input logical function. Draw the circuit schematic for the gate and find the Boolean expression for the logical function. (5 p)

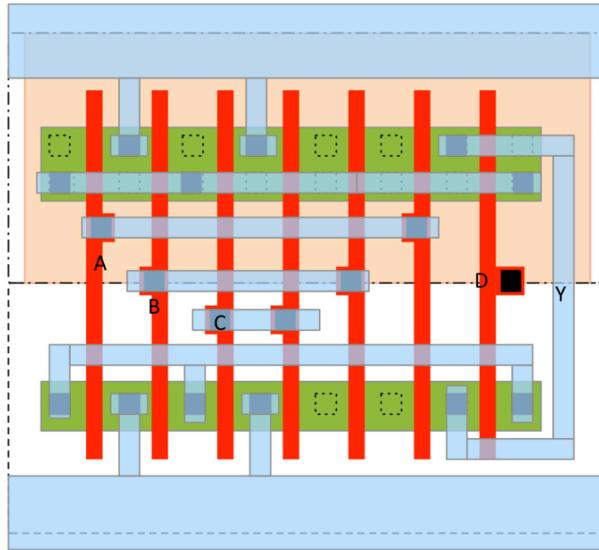

**Exercise 8.4:** Problem tests going from layout to schematic and identifying the logical function. Exam 2015-01-05 Problem 1. *Solution on page 63.*

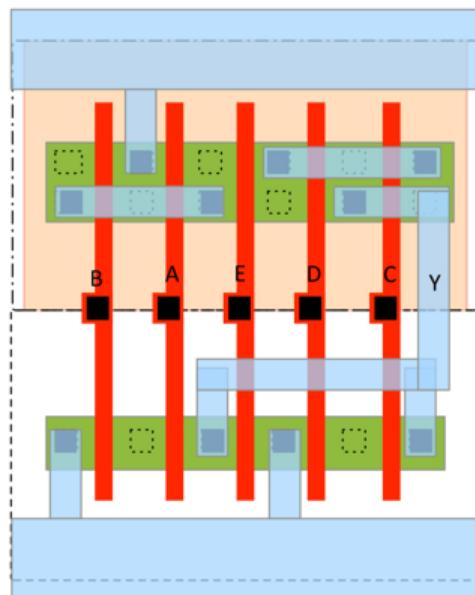

Figure 8.4 shows the layout of another four-input standard cell.

a) Draw the corresponding transistor diagram. Make sure that your transistor diagram matches the layout exactly! (6 p)

Figure 8.3: The layout for a 4-input static CMOS gate.

Figure 8.4: The layout for another 4-input standard cell.

b) Identify the logical function that the layout implements.

(4 p)

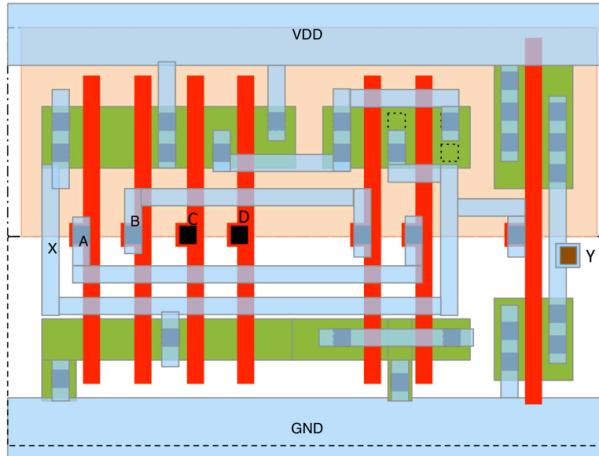

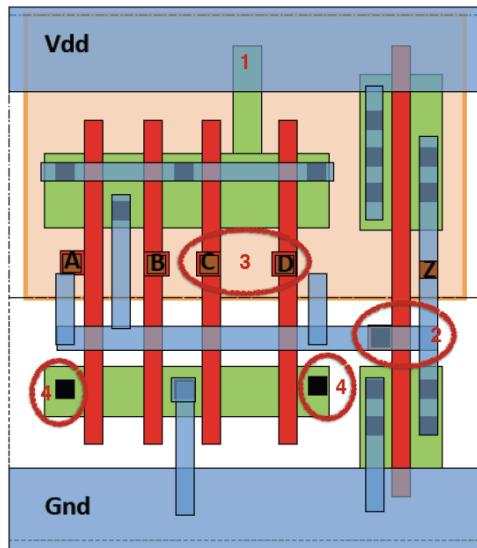

**Exercise 8.5:** Task tests going from schematic to layout. Exam 2016-12-22 Task 1(b). *Solution on page 64.*

Draw the layout for the gate schematics in Figure 8.5a in the template provided in Fig. 8.5b. For simplicity we have assumed that all transistors have the same width although that may not be a good sizing. Hint: Remember that diffusion can be used to route  $V_{DD}$  or ground short distances. (5 p)

**Exercise 8.6:** Task tests understanding of what LVS does and reading layout. Exam 2013-10-22 Task 1. *Solution on page 64.*

What if we are confused by the error messages from the LVS, how shall we go about to find the discrepancies between the layout and the schematic entry? In other words, find the errors in the layout shown in Figure 8.6a for an AO22 gate. There are four discrepancies to detect! (10 p)

(a) A schematic of the gate taken from a patent application.  $V_{DD}$  is at the top of the schematic although is not clear from the notation.

(b) A layout template in which to lay out the gate.

Figure 8.5: A static CMOS gate with four logical functions outputs.

(a) Layout of the AO22 gate

(b) Schematic for the AO22 gate.

Figure 8.6: An LVS problem - where in the layout are the discrepancies between the layout and the schematic?

# Chapter 9

## Sequential circuits

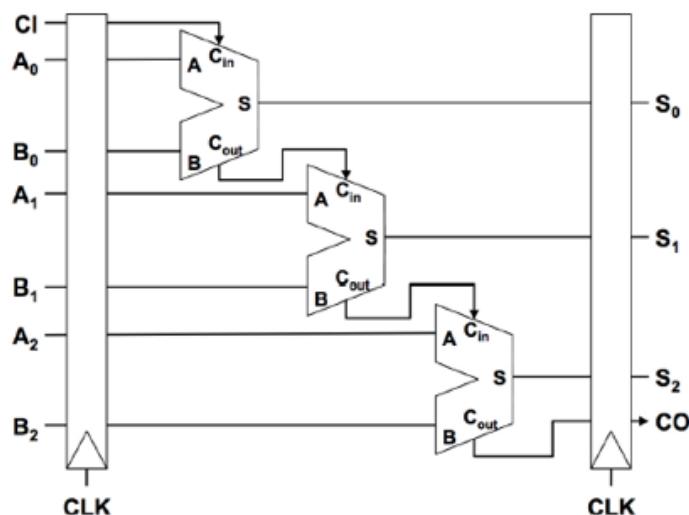

**Exercise 9.1:** Problem tests understanding of delay for ripple-carry adder together with flip-flops *Solution on page 65.*

You are to use an adder made up of your ripple-carry cell from prelab 2 and a sum cell in a pipelined processor. For simplicity we do not analyze the sum cell in detail; rather we assume the sum cell has a propagation delay of 60 ps. Also assume that the sum cell is of the type that takes the generated  $C_{out}$  from the same bit as one of its inputs, in addition to the input data bits  $A$  and  $B$  and  $C_{in}$ . (That is the sum cell shown in Figure 11.4 in Weste & Harris.)

Reminder in case you do not have it handy: The delay of the 8-bit ripple circuit in prelab 2 was around 340 ps with  $p_{inv} = 0.8$ .

You have available flip-flops with the characteristics given in Table 9.1

Table 9.1: Flip-flop timing characteristics

| Flip-flop timing parameter              | Value [ps] |

|-----------------------------------------|------------|

| Setup time, $t_{setup}$                 | 50         |

| clk-to-Q propagation delay, $t_{pq}$    | 50         |

| clk-to-Q contamination delay, $t_{ccq}$ | 35         |

| Hold time, $t_{hold}$                   | 10         |

- Assuming the adder is the combinational circuit limiting the speed of your entire processor, what is the highest clock frequency with which you can clock it, if your adder has 16 bits?

- Again assuming the adder is the combinational circuit limiting the delay of the processor, what is the highest clock frequency with which you can clock it, if your adder has 64 bits?

- What if there is clock skew in your system? Assuming the maximum clock skew is 75 ps between any two flip-flops, how will the results in tasks a) and b) change?

**Exercise 9.2:** Problem tests understanding of delay for ripple-carry adder together with flip-flop hold violations. *Solution on page 65.*

Return to the setup in the previous exercise. Go back to the ripple-carry adder design based on the carry-chain you implemented in lab 2. Also assume that the sum cell has a contamination delay of 30 ps.

- Estimate the contamination delay of the 16-bit ripple-carry adder designed from your ripple-carry chain. If necessary, you may assume that the inverses are also available from the flip-flops preceding the adder.

- With these contamination delays, the flip-flop data in Table 9.1, the clock frequency calculated in task 9.1. a) and no clock skew determine if you have to worry about hold violations.

c) What if you have a clock skew of maximum 75 ps?

**Exercise 9.3:** Problem tests understanding of delay for adders together with flip-flops and critical path. This problem is from the exam 2016-08-22. It has been modified slightly to fit the purpose in this chapter. *Solution on page 65.*

In this course we have designed many adders but no multipliers. In this problem you will investigate how to use adders to implement binary multiplication and the performance of such an approach.

In Figure 9.1 is an example of a 6-bit binary multiplication from the Weste and Harris textbook.

$$\begin{array}{r}

011001 : 25_{10} \\

\times 100111 : 39_{10} \\

\hline

011001 \\

011001 \\

011001 \\

000000 \\

000000 \\

+011001 \\

\hline

001111001111 : 975_{10}

\end{array}$$

multiplicand

multiplier

partial products

product

Figure 9.1: Example of a multiplication of two 6-bit binary numbers. From Weste and Harris textbook.

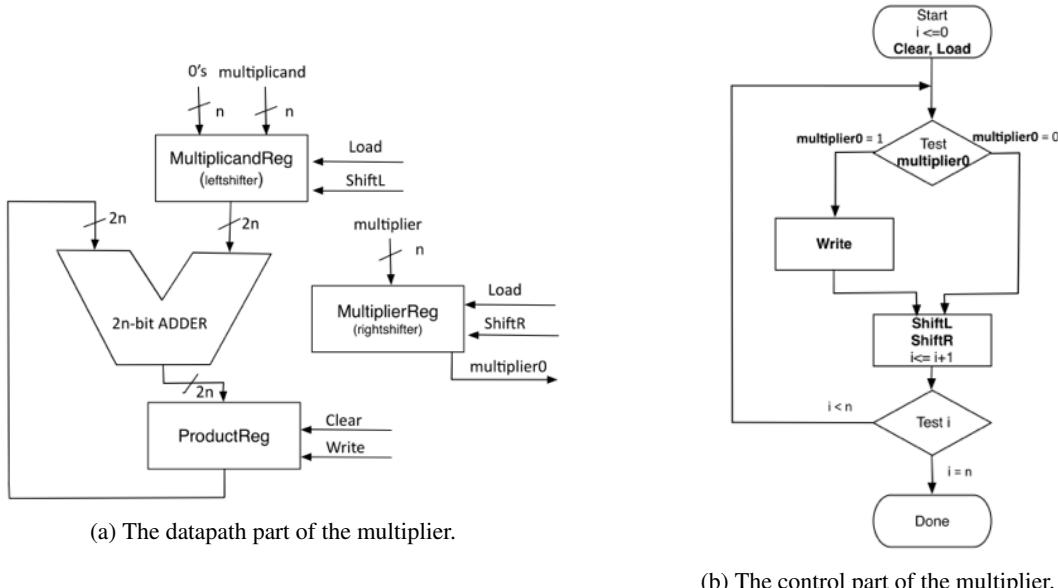

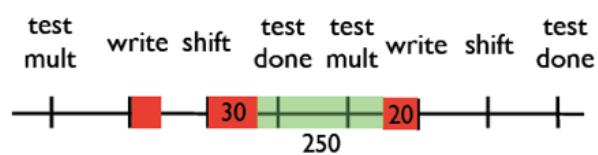

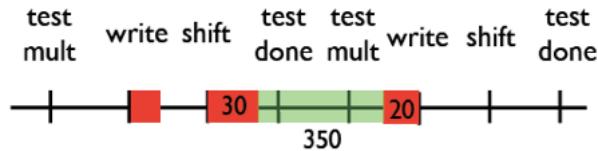

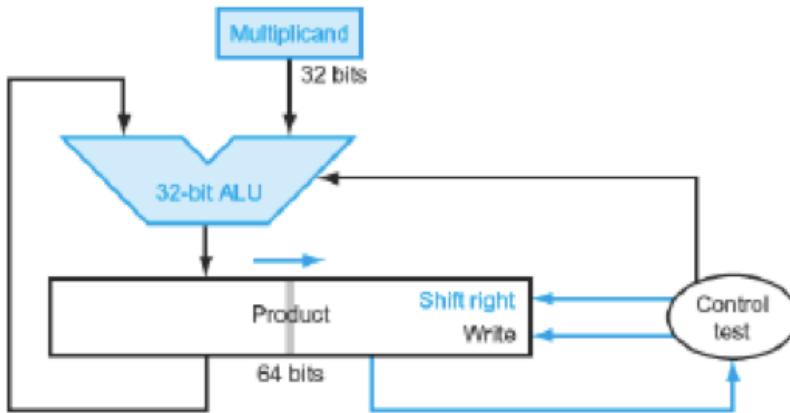

From the example it is clear that the partial products are just left-shifted versions of the multiplicand. Binary multiplication can thus be performed by repeatedly shifting the multiplicand to the left and adding it to the product. Figure 9.2 shows how a 2n-bit adder can be used to perform binary multiplication of two n-bit binary numbers. To the left in the figure you see the datapath with an adder, two shifters and a register, and to right the iterative control required to perform a multiplication.

Figure 9.2: An iterative multiplier that uses a 2n-bit adder.

In this problem, your task is to investigate the performance of this iterative multiplication for different types of adders and number of bits,  $n$ .

In Table 9.2 are worst-case propagation delays for two types of adders, for 8- and 16-bit additions.

Table 9.2: Adder worst-case propagation delays

| Number of bits in adder $n$ | Ripple-carry adder $t_{pd}$ (ps) | Prefix adder $t_{pd}$ (ps) |

|-----------------------------|----------------------------------|----------------------------|

| 8                           | 130                              | 200                        |

| 16                          | 250                              | 250                        |

As you know for ripple-carry adders the worst-case delay grows linearly with the number of bits,  $n$ . We have not yet dealt with prefix adders, but their delay grows linearly with  $\log_2(n)$ .

Assume that the **ProductReg** is made up of flipflops with these characteristics:  $t_{setup} = 20$  ps,  $t_{pcq} = 30$  ps. For the shifter registers, assume there is a 30 ps delay from when the **ShiftR** and **ShiftL** signals are issued until the shifted output is available at their outputs.

For the control logic assume that each step takes one clock cycle. You may assume that the control signals that are the outputs from the control logic are perfectly synchronized with the clock.

- Use the worst-case delay adder data in the table above to estimate the maximum clock frequency that can be used for the iterative 8-bit multiplier. With this clock frequency and assuming worst-case multiplier input data, how long would it take to complete one 8-bit multiplication? (4 p)

- What if we extend the iterative multiplier from task a) to multiply two 32-bit binary numbers? How will its worst-case delay change? Assume that you can generate wider versions of the two types of adders in the table above. Which type of adder would you select? Motivate! For the selected type of adder, estimate the maximum clock frequency with which one could clock the multiplier control logic and still ensure a correct result. How long would it then take to complete one 32-bit multiplication with the worst-case multiplier input data? (6 p)

#### BONUS QUESTION

- The proposed multiplier is not that well designed. Suggest one substantial improvement that could be made to the datapath and estimate how much that improvement would increase the maximum clock frequency calculated in task b). (4 p)

**Exercise 9.4:** Problem tests understanding of critical path, setup and hold violations. It is problem 5 from exam 2016-10-29. *Solution on page 66.*

Assume that you are designing an adder for the minimalistic 3-bit ArmStrong processor. The adder is built from three full adders such that the carry-out signal of the first adder is the carry-in signal to the second adder and the carry out from the second adder is the carry in of the third adder, as shown in Figure 9.3. At the input and output of the adder are two registers made up of flip-flops.

Figure 9.3: ArmStrong 3-bit adder.

a) If there is no clock skew, what is the maximum operating frequency of the circuit? Assume the delays for typical CMOS-process parameters, given in the leftmost column of values in Table 9.3. (2 p)

b) How much clock skew can the circuit tolerate before it might experience a hold violation? Again assume the delays for typical CMOS process parameters from Table 9.3. (2 p)

c) Assume we had characterized the flip-flop and full-adder cells also for the fast-fast and slow-slow process corners and measured the delays shown in the two right-hand columns in Table 9.3. Describe how you would go about extending the results from tasks a) and b) with these additional data so that you can be sure that your adder works correctly also for these two extreme corners. Carry out your proposed calculations. Did you have to modify your results from a) and b)? If so, what are the updated results? (6 p)

Table 9.3: ArmStrong timing characteristics

| Delay                                  | Typical corner measured value<br>[ps] | Fast-fast corner measured value<br>[ps] | Slow-slow corner measured value<br>[ps] |

|----------------------------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|

| <b>Full adders</b>                     |                                       |                                         |                                         |

| $t_{pd}$ , A or B $\rightarrow$ S      | 30                                    | 25                                      | 35                                      |

| $t_{cd}$ , A or B $\rightarrow$ S      | 22                                    | 16                                      | 20                                      |

| $t_{pd}$ , A or B $\rightarrow$ Cout   | 25                                    | 20                                      | 30                                      |

| $t_{cd}$ , A or B $\rightarrow$ Cout   | 22                                    | 17                                      | 25                                      |

| $t_{pd}$ , Cin $\rightarrow$ S or Cout | 20                                    | 17                                      | 25                                      |

| $t_{cd}$ , Cin $\rightarrow$ S or Cout | 15                                    | 12                                      | 20                                      |

| <b>Flip-flops</b>                      |                                       |                                         |                                         |

| $t_{pcq}$                              | 35                                    | 28                                      | 40                                      |

| $t_{ccq}$                              | 21                                    | 16                                      | 24                                      |

| $t_{\text{setup}}$                     | 30                                    | 25                                      | 35                                      |

| $t_{\text{hold}}$                      | 10                                    | 5                                       | 20                                      |

# Chapter 10

## Power, energy and scaling

This chapter contains problems on power and energy. There is also a section on technology scaling in combination with delay, power, energy and area calculations, since the reason for technology scaling is often to decrease the power consumption while maintaining speed.

### 10.1 Power and energy

**Exercise 10.1:** Problem tests understanding of power. Problem is 5.2 in the textbook. *Solution on page 67.*

You are considering lowering  $V_{DD}$  to try to save power for a static CMOS gate. You will also scale the threshold voltages,  $V_T$ , proportionally to maintain speed (= performance). Will dynamic power consumption go up or down? Will static power consumption go up or down?

**Exercise 10.2:** Problem tests basic knowledge on how to calculate static and dynamic power dissipation. Exam 2014-10-31 Problem 1. Slightly revised. *Solution on page 67.*

The power consumption of a CMOS inverter can be minimized through circuit optimizations. How should each parameter in Table 10.1 be changed to reduce the three different components of the inverter power consumption? For each parameter indicate I for increase, D for decrease or N for does not affect this type of power consumption.

Table 10.1: Table for power optimization.

| Type of power to minimize                                                                                                   | Capacitive load $C_L$ | Supply voltage $V_{DD}$ | Threshold voltages $V_T$ | Transistor widths $W$ |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|--------------------------|-----------------------|

| Dynamic power consumption due to the charging and discharging of the capacitive load $C_L$                                  |                       |                         |                          |                       |

| Power consumption due to shortcircuit current during transition (assuming a fixed rise and fall time at the inverter input) |                       |                         |                          |                       |

| Static power dissipation, that is the power due to the transistor leakage currents                                          |                       |                         |                          |                       |

**Exercise 10.3:** Problem tests understanding of subthreshold leakage. *Solution on page 67.*

Shown in Figure 10.1 are the static power entries for a 2-input NAND gate in the .lib file from a standard-cell library. When we inspect the power entries, we notice that one of the input combinations for this gate has a much lower leakage power than do the other three. Why is this? Explain!

```

cell (ND2HSX1) {

area : 6.0516;

cell_leakage_power : 10.64;

leakage_power() {

when : "A&B";

value : 2.874;

}

leakage_power() {

when : "!A&B";

value : 15.24;

}

leakage_power() {

when : "A&!B";

value : 16.38;

}

leakage_power() {

when : "A&B";

value : 17.2;

}}

```

Figure 10.1: Data from lib file for 2-input NAND gate.

Will the ripple-carry gate that you have designed in labs 2 and 3 exhibit a similar leakage pattern, or not? That is, is there a best or worst combination of inputs when it comes to leakage? If so, what for input combination do we have this situation?

**Exercise 10.4:** Problem tests ability to calculate dynamic power dissipation and understanding of its origins. Exam 2015-01-05 Problem 3 c)-d). *Solution on page 68.*

Refer back to your solution to Exercise 5.14 or to its solution on page 51. Also, assume that the operating frequency is 200 MHz and that  $\alpha$  is 0.25 for the signal that drives the pad.  $V_{DD}$  is 1 V.

- c) For your design what is the dynamic power consumption? (2 p)

- d) From the usual formula used for the dynamic power consumption it seems that to minimize the power consumption during switching there should be no inverters in the box in Figure 5.7. Why is this conclusion incorrect? (2 p)

**Exercise 10.5:** Problem tests ability to calculate static and dynamic power dissipation and knowledge of power and energy. It is adapted from two examples in the text book. Exam 15-10-29 Problem 3. *Solution on page 68.*

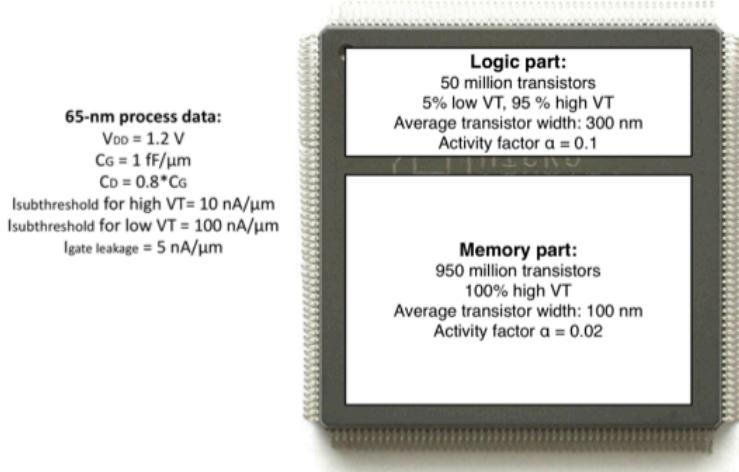

A digital system on a chip has 1 billion transistors. Of these 50 million are used in static CMOS logic gates and the rest are used in memories. The two parts of the chip are illustrated in Figure 10.3, which also includes relevant chip and process data.

- a) Using data from Figure 10.3, estimate the power due to dynamic switching at a clock frequency of 1 GHz, if we neglect the effects of short-circuit current and wire capacitances. (2 p)

- b) Using data from the figure above, estimate the static power consumption for the chip. (2 p)

- c) What if the logic part can be redesigned so that fewer transistors than before require the low  $V_T$ : only 1 % of the original number, while the total number of logic transistors has to be increased by 20 %. The activity factor stays the same. What are the effects of this redesign on the static and dynamic power consumption for the logic part? (2 p)

- d) If the measures above are not enough, one may have to use power gating to reduce the leakage further. What if we are to power-gate the entire logic part in the chip? We can tolerate only a 5 % drop of  $V_{DD}$  due to the resistance in the power switch, otherwise the increase in delay will be too large. How wide would our switch have to be if the pMOS transistor ON resistance is  $2 \text{ k}\Omega \mu\text{m}$ ? Assume the dynamic power consumption of the logic calculated in task a). (2 p)

Figure 10.2: Data for the system on chip.

e) How much energy would be required to switch the power-gating transistor on and off once? How long a time with the leakage current for the logic part only, as calculated in task b), does that energy correspond to? (2 p)

#### BONUS QUESTION

f) When considering power gating, would it be better to start with the situation described in tasks a) and b) or the one described in task c)? Discuss the design considerations! (2 p)

**Exercise 10.6:** Problem tests ability to calculate static and dynamic power dissipation and knowledge of power and energy. It is adapted from two examples in the text book. Exam 15-10-29 Problem 3. *Solution on page 69.*

What if the processor in problem 10.5 is running at  $V_{DD} = 1$  V instead. Would the width of the required switch, calculated in 10.5 d) change? What about the energy and time calculated in 10.5 e)?

**Exercise 10.7:** Problem tests static and dynamic power dissipation and their relation to  $V_{DD}$  and clock frequency. Exam 2016-12-22 Problem 4. *Solution on page 69.*

In this problem you will analyze the energy consumption for a video-rendering application run on a processor dedicated to this application. The processor can run at different supply voltages and has both a sleep mode and a hibernation mode. Your final task is to determine if the hibernation mode is useful for this particular application.

**Application:** The digital video in the video-rendering application has 25 frames per second. One frame is 640x480 pixels. Each pixel is represented by 24 bits. The number of operations needed per pixel is 8 and these operations take 10 clock cycles to complete on the PP processor. The computations for one frame have to be completed in the time allotted for that frame.

**PP processor:** The PP processor used for this application has some characteristics shown in Table 10.2. You also know that it is fabricated in a CMOS process where the threshold voltages are 0.3 V. You may assume that the quadratic current equations hold in this process.

**Sleep mode:** The time it takes to enter sleep mode is 10 μs and it takes 20 μs for the processor to wake up from sleep mode. The energy required to switch the clocks off is 10 μJ.

**Hibernation mode:** The time it takes to enter hibernation mode is 1 ms and it takes 19 ms to wake up from hibernation mode. The energy required to turn off  $V_{DD}$  is 500 μJ.

a) Fill in the four empty cells in Table 10.2 above with reasonable values. (4 p)

b) Considering only dynamic power, how much energy will be used for one frame of the video-rendering application in these two cases: 1.2 V and 0.8 V supply voltage? (2 p)

Table 10.2: Data for the PP processor

| Supply voltage $V_{DD}$ [V] | Maximum clock frequency [GHz] | Current due to dynamic power consumption @ max clock frequency and a realistic activity factor [mA] | Idle current @ room temperature @ max clock frequency and a low activity factor [mA] | Static current in sleep mode @ room temperature (clock signal turned off for logic, but clock generation maintained) [mA] | Static current in hibernation mode (clock generation stopped and internal supply voltages turned off) [ $\mu$ A] |

|-----------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 1.2                         | 1.0                           | 600                                                                                                 | 100                                                                                  | 60                                                                                                                        | 60                                                                                                               |

| 1.0                         | ?                             | ?                                                                                                   | 80                                                                                   | 37.5                                                                                                                      | 60                                                                                                               |

| 0.8                         | ?                             | ?                                                                                                   | 64                                                                                   | 28                                                                                                                        | 60                                                                                                               |

c) How much energy will be dissipated due to static power consumption for one frame for the two cases: 1.2 and 0.8 V supply voltage? Assume that the processor immediately enters sleep mode when no computations are required for the video-rendering application. (2 p)

d) What is your recommendation regarding the hibernation mode? Should it be used or not for the video-rendering application? Motivate your reply using data given in this problem and your results from tasks a)-c). (2 p)

**Exercise 10.8:** Problem tests ability to calculate delay with different threshold voltages. Exam 2013-10-21 Problem 5. *Solution on page 71.*

Need to add existing solution. Should this problem move, since it actually does not require any power calculation?

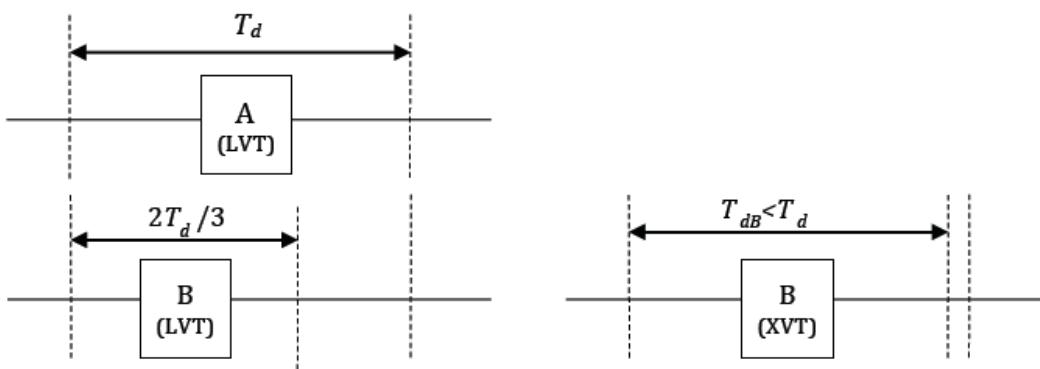

In a processor we have two circuit blocks, A and B, working in parallel. Both blocks are designed using the low- $V_T$  standard cell library (where  $V_{TL} = 0.2V_{DD}$ ). The delay of block B is only two thirds of the delay of block A, so in a way it is too fast and in some sense probably wasting energy. For block B the supply voltage could be reduced to save energy, or equivalently, the threshold voltage could be increased. The CMOS process used for the design comes with three different threshold voltages, low  $V_T$ , standard  $V_T$  and high  $V_T$ . By redesigning block B with cells from a library with a higher  $V_T$ , we can reduce the static leakage power while timing constraints are still met. Remember that a 100 mV increase in  $V_T$  leads to a factor of ten reduction of the subthreshold current. The standard  $V_T$ :  $V_{TS} = 0.3V_{DD}$  and the high  $V_T$ :  $V_{TH} = 0.4V_{DD}$ .

Figure 10.3: Illustration of timing situation with blocks A and B. With the VLT library, the delay of block B is  $2/3$  of that of B. Which library can we select for B while still maintaining the situation that A determines the critical delay.

What if we were to redesign block B using a higher threshold voltage, which cell library would we use, the standard SVT library or the high HVT library, if we still were to meet the  $T_d$  timing constraint? Assume that the simple square-law MOSFET saturation current model can be used to estimate the MOSFET driving capability! All

parameters except the threshold voltages are the same among libraries.

## 10.2 Technology scaling and other scalings too

In this section we have collected problems related to technology scaling, but also problems that deal with other scalings, so that there is a mix.

**Exercise 10.9:** Problem tests ability to calculate scaling dependence for secondary parameters *Solution on page 71.*

Technology scaling is (or maybe, one now should say, was) performed to increase speed while lowering power consumption and increasing packing density, thus decreasing chip area, or enabling more functions on the same chip area. The classic scaling is the Dennard scaling. In table 10.3 the scaling of the primary parameters is given at the top part of the table. Your task is to derive the scaling for each of the secondary parameters from the primary ones. It is best to do it in order since many of the derived parameters depend on each other.

Table 10.3: Table for Dennard scaling.

| Parameter                         | Sensitivity expression         | Dennard scaling, scaling factor $S$ |

|-----------------------------------|--------------------------------|-------------------------------------|

| Scaling parameters                |                                |                                     |

| $L$ : length                      |                                | $1/S$                               |

| $W$ : width                       |                                | $1/S$                               |

| $t_{ox}$ : gate oxide thickness   |                                | $1/S$                               |

| $V_{DD}$ : power supply voltage   |                                | $1/S$                               |

| $V_T$ : threshold voltage(s)      |                                | $1/S$                               |

| $NA$ : substrate doping           |                                | $S$                                 |

| Device characteristics            |                                |                                     |

| $\beta$ : current factor          | $\frac{W}{L} \frac{1}{t_{ox}}$ |                                     |

| $I_{DS}$ : transistor current     | $\beta(V_{DD} - V_T)^2$        |                                     |

| $R_{eff}$ resistance              | $\frac{V_{DD}}{I_{DS}}$        |                                     |

| $C$ : gate capacitance            | $\frac{WL}{t_{ox}}$            |                                     |

| $\tau$ : gate delay               | $R_{eff}C$                     |                                     |

| $f$ : clock frequency             | $\frac{1}{\tau}$               |                                     |

| $E$ : switching energy (per gate) | $CV_{DD}^2$                    |                                     |

| $P$ : switching power (per gate)  | $Ef$                           |                                     |

| $A$ : area (per gate)             | $WL$                           |                                     |

| Switching power density           | $\frac{P}{A}$                  |                                     |

| Switching current density         | $\frac{I_{DS}}{A}$             |                                     |

**Exercise 10.10:** EXTRA Problem tests ability to calculate scaling dependence for secondary parameters

*Solution on page 71.*

For quite a few years semiconductor manufacturers resisted scaling down the supply voltage and threshold voltages, since it would make interfacing with existing technologies harder. To see the effect of this type of scaling repeat exercise 10.9 but with "1" as the entries for  $V_{DD}$  and  $V_T$ .

**Exercise 10.11:** Problem tests ability to apply process scaling to delay and power. Exam 2011-08-24, task 4a. *Solution on page 71.*

The FO4 delay of the AMS 0.35  $\mu\text{m}$  CMOS process running at 3.3 V is 125 ps. What would the FO4 delay be of a 0.13  $\mu\text{m}$  CMOS process running at  $V_{DD} = 1.8$  V?

**Exercise 10.12:** Problem tests ability to calculate static and dynamic power dissipation under the effect of technology scaling. Exam 2012-10-26 Problem 5. *Solution on page 72.*

The work horse product of the California-based microprocessor company MegaProcessor is a singlecore microprocessor manufactured in a 90 nm CMOS technology. The microprocessor operates at 3.8 GHz with a 1.2 V supply, a 100 W power dissipation, and a die area of 200  $\text{mm}^2$ . The company is now about to design a dual-core microprocessor in the same technology, by duplicating the single-core design.

- What would be the frequency and supply voltage for the dual-core design if the same size of the heat sink is to be maintained, that is if  $P_{DUAL CORE} = P_{SINGLE CORE}$ ? Assume that 100 % of the power dissipation is due to dynamic power, and, for simplicity, assume that the frequency of operation is roughly linearly proportional to the supply voltage. (3 p)

- When the single core design from above is moved to the 65 nm technology node, what would be its size, power and frequency of operation with a 1 V power supply? (3 p)

- Now consider the following what-if situation: assume that 10 % of the 100 W total power dissipated by the single-core in task a) is due to static (leakage) power and that 90 % is due to dynamic switching power. Furthermore, in the 65 nm process the standard threshold voltage (svt) is almost 50 mV lower than in the 90 nm process, yielding a four-fold increase in leakage power at room temperature. What would be the total power dissipation of the single-core processor when transferred to the 65 nm process? How many percent would be leakage power? (4 p)

**Exercise 10.13:** Problem tests ability to minimize dynamic power dissipation under constraint of constant delay. Exam 13-08-26 Problem 3. *Solution on page 72.*

One reason for going to multi-core computer systems is to reduce the total power dissipation by lowering the supply voltage and then compensate for speed losses by using more than one core that work in parallel. A simplified assumption is that four cores at a fourth of full speed can do the same work as one core at full speed. From these simple assumptions and from the assumption that the delay is given by  $0.7 \frac{CV_{DD}}{I_{DSAT}}$ , find out how much one can reduce the power dissipation by using a quad-core design, while still getting the same job done. Assume that we use the same CMOS process and the same core, but that an additional 20 % of the core capacitance must be added to the total chip capacitance for the control unit coordinating the four cores. Let us assume that  $V_T$  is 25 % of the original supply voltage. Use the simple square-law current model for the MOSFET saturation current!

# Chapter 11

## Adders

Need to add more adder problems.

**Exercise 11.1:** Problem test understanding of block-propagate signal and its use to create faster adders.

Exam 2017-08-21 Problem 6. *Solution on page 73.*

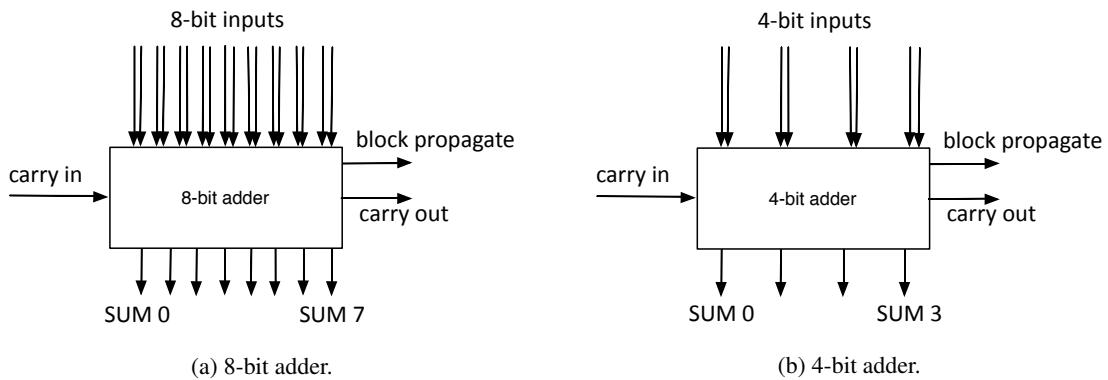

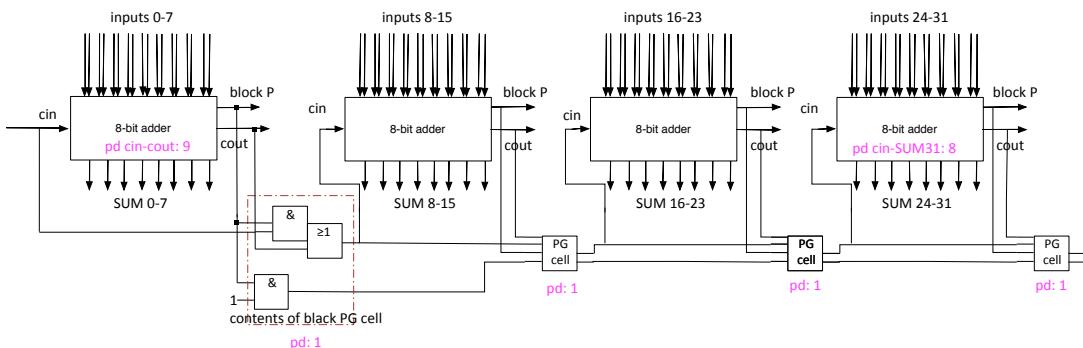

Figure 11.1: Two adders. In (a) is an 8-bit adder and in (b) a 4-bit adder.

You have designed an 8-bit adder circuit with eight SUM outputs, one carry output and one block-propagate output, as shown in Figure 11.1 (a). The propagation delays expressed in unit delays are shown in Table 11.1. You have now been asked to design a 32-bit adder with as short a propagation delay as possible. Available to you are AO, OA, AND and OR gates which each have a delay of 1 unit delay.

Table 11.1: Adder propagation delays

| Propagation delay                       | 8-bit adder<br>[unit delays] | 4-bit adder<br>[unit delays] |

|-----------------------------------------|------------------------------|------------------------------|

| From carry in to carry out              | 9                            | 5                            |

| From any data bit to carry out          | 9                            | 5                            |

| From any data bit to block propagate    | 4                            | 2                            |

| From carry in to highest SUM output     | 8                            | 4                            |

| From any data bit to highest SUM output | 8                            | 4                            |

- Draw a diagram of how you would construct a fast 32-bit adder from your 8-bit adder. In addition to the 32 SUM bits your 32-bit adder should also output the block-propagate and block-generate signals for the entire adder. (5 p)

- Derive the propagation delay of your adder as drawn in task a). Assume that all inputs to your adder arrive simultaneously. (3 p)

c) What if you also had designed a similar 4-bit adder, as shown in Figure 11.1 (b), with propagation delays given in the last column of are shown in Table 11.1. Would it be better to use the 4-bit adder rather than the 8-bit adder in your 32-bit adder? Motivate by drawing a diagram and calculating the delay. (2 p)

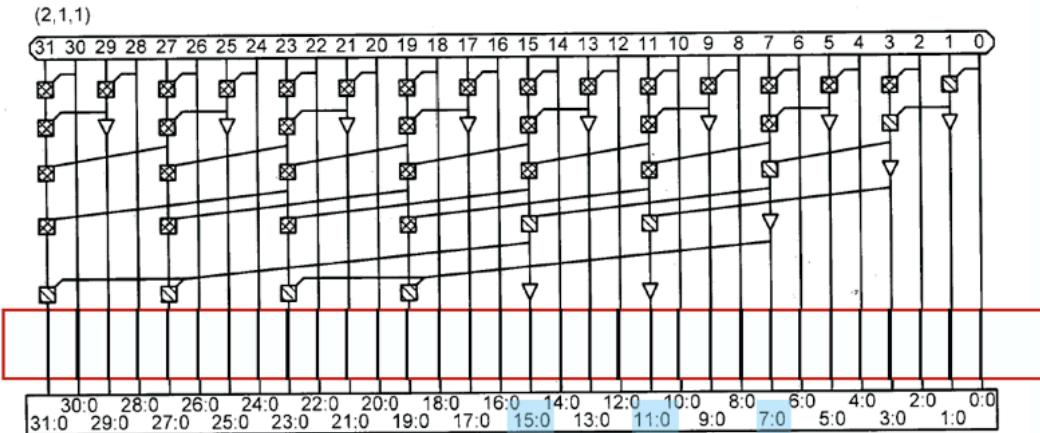

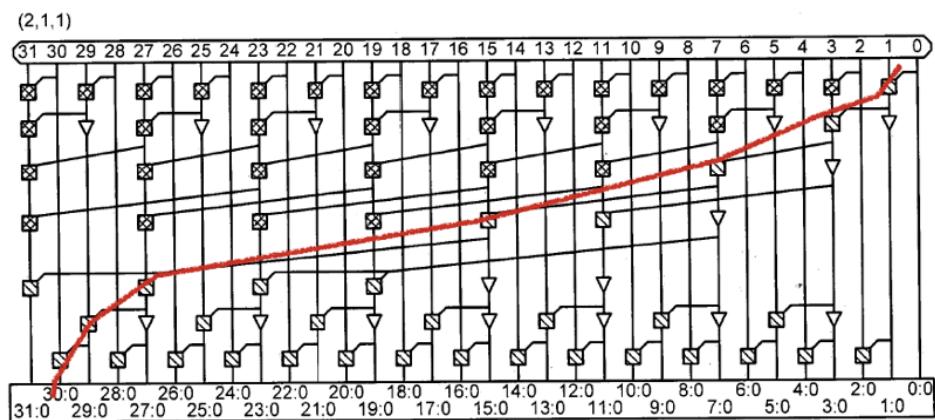

**Exercise 11.2:** Problem tests understanding of prefix adder sum generation and critical path. Exam 2016-12-22 Problem 6. *Solution on page 73.*

Figure 11.2 shows the beginning of the design of an unknown prefix adder. As you can see from the figure, in this type of adder no dot-operator cell in the forward or backwards tree drives more than two other dot-operator cells. (The triangles in the diagram are buffers that you can ignore in this problem.)

Figure 11.2: An unknown prefix adder where the output of any dot-operator cell is connected to a maximum of two other dot-operator cell inputs.

a) Your task is to complete the adder design by adding the missing dot-operator cells, in the red box, so that all input carries needed for the SUM operations are available at the bottom. As an example, group carries C15:0, C11:0 and C7:0 (indicated with blue in Figure 6) are already available to form SUM16, SUM12 and SUM8, respectively. A fully correct solution should maintain the design principle that no cell in the tree drives more than two other dot-operator cells. Solutions that do not fulfill this principle, but are logically correct, will give partial credit. The figure is repeated twice at the end of the exam so that you tear off and turn in with your solutions. (7 p)

b) What is the critical path of the prefix tree you have drawn in task a)? Indicate it clearly in the complete tree that you hand in. (3 p)

# Chapter 12

## Solutions

### 12.1 Introduction

### 12.2 Background material

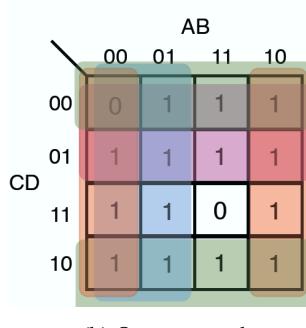

### 12.3 Logic functions

**Solution 3.1** Problem is on page 9.

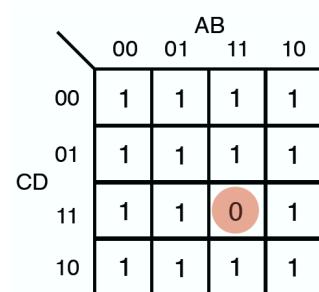

- The circuit is a 4-input NAND gate. One solution with corresponding Karnaugh maps (ones and zeros) is shown in Figure 12.2. With the zeros covered it is easy to directly find the n-net, because the n-net implements the inverse of the logical function; in this case AND.

- The logic gate is an AND-OR-INVERT (AOI) 3+1 gate. One solution with corresponding Karnaugh maps (ones and zeros) is shown in Figure ??.

- The logic gate is an OR-AND-INVERT (OAI) 3+1 gate. One solution with corresponding Karnaugh maps (ones and zeros) is shown in Figure ??.

- One solution with corresponding Karnaugh maps (ones and zeros) is shown in Figure ??.

(a) Gate.

(b) Ones covered.

(c) Zero(s) covered.

Figure 12.1: NAND4 (a) gate and corresponding Karnaugh map with (b) ones and (c) zeros covered.

**Solution 3.2** Problem is on page 9.

Figure 12.2: NAND4 (a) gate and corresponding Karnaugh map with (b) ones and (c) zeros covered.

**Solution 3.3** *Problem is on page 9.*

**Solution 3.4** *Problem is on page 10.*

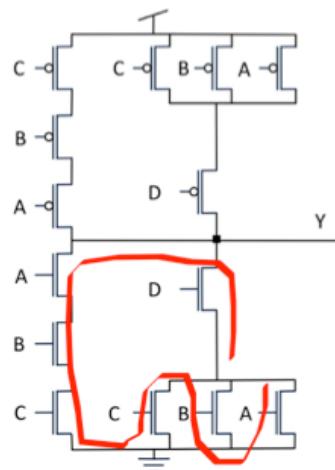

The logical functions are inverter ( $Y_1$ ) and nand ( $Y_2$ - $Y_4$ ). The expressions are found in Figure 12.3.

Figure 12.3: Schematic and logic functions for multi-output gate.

## 12.4 The MOS transistor

**Solution 4.1** *Problem is on page 11.*

a) For the n-channel MOSFET we have the following conditions. For the transistor being ON:

$$V_{GS} \geq V_{TN} \quad (12.1)$$

For the transistor being in saturation:

$$V_{DS} \geq V_{GS} - V_{TN} \quad (12.2)$$

The borders between the regions is found when there is an equal sign in (12.1) and (12.2) instead of a greater-than-equal sign.

b) The corresponding conditions for the p-channel MOSFET are as follows below. For the transistor being ON it is

$$V_{GS} \leq V_{TP} \quad (12.3)$$

Figure 12.4: Regions of operation for a p-channel MOSFET. Note that all voltages are negative.

Remember here that  $V_{TP}$  is negative for the p-channel MOSFET. condition is

$$V_{DS} \leq V_{GS} - V_{TP}. \quad (12.4)$$

For the p-channel MOSFET the borders between the regions are found when there is an equal sign in (12.3) and (12.4) instead of a less-than-equal sign. So the equations for the borders are the same for the n-channel and the p-channel MOSFETs. The difference is that all voltages are negative for the pMOS case. The resulting diagram of the regions of operation for the p-channel MOSFET is shown in Figure 12.4.

**Solution 4.2** *Problem is on page 11.*

a)

$$V_{GT} = V_{GS} - V_T = 1.2 \text{ V} - 0.3 \text{ V} = 0.9 \text{ V} \quad (12.5)$$

b) Assuming that the quadratic equation for the saturation current holds, we find:

$$I_{DSAT,\max} = \frac{k_N}{2} V_{GT}^2 = \frac{900 \mu\text{A/V}^2}{2} 0.9^2 \text{ V}^2 = 364.5 \mu\text{A} \quad (12.6)$$

c) The saturation voltage is the drain-source voltage for which we have

$$V_{DSAT} = V_{GS} - V_T. \quad (12.7)$$

Thus in the situation in task b) we have

$$V_{DSAT} = 1.2 \text{ V} - 0.3 \text{ V} = 0.9 \text{ V}. \quad (12.8)$$

**Solution 4.3** *Problem is on page 11.*

a) The expression for the gate capacitance is

$$C = C_{\text{ox}} \times L \times W \quad (12.9)$$

One would assume that in a 65 nm process the transistor length is 65 nm. However, it turns out that the physical length is somewhat less so we have to use 60 nm as the transistor length. So in this case we have:

$$C = 20 \text{ fF}/\mu\text{m}^2 \times 60 \text{ nm} \times 1 \text{ mm} = 20 \text{ fF}/\mu\text{m}^2 \times 0.060 \mu\text{m} \times 1000 \mu\text{m} = 1200 \text{ fF} = 1.2 \text{ pF} \quad (12.10)$$

b)

$$C = 10 \text{ fF}/\mu\text{m}^2 \times 45 \text{ nm} \times 5 \mu\text{m} = 10 \text{ fF}/\mu\text{m}^2 \times 0.045 \mu\text{m} \times 5 \mu\text{m} = 2.25 \text{ fF} \quad (12.11)$$

c)

$$C = 10 \text{ fF}/\mu\text{m}^2 \times 45 \text{ nm} \times 280 \text{ nm} = 10 \text{ fF}/\mu\text{m}^2 \times 0.045 \mu\text{m} \times 0.28 \mu\text{m} = 0.13 \text{ fF} \quad (12.12)$$

**Solution 4.4** Problem is on page 12.

a)

$$R_{\text{eff}} = \frac{1 \text{ V}}{500 \mu\text{A}} = 2 \text{ k}\Omega \quad (12.13)$$

$$R_{\text{eff}} = \frac{1 \text{ V}}{750 \mu\text{A}} = 1.33 \text{ k}\Omega \quad (12.14)$$

b)

$$R_{\text{eff}} = \frac{2 \text{ k}\Omega \mu\text{m}}{5 \mu\text{m}} = 400 \Omega \quad (12.15)$$

c)